## re: ballot comment #15, maintenance request 0286

## 2 802.1Q-Rev Project Editor, Mick Seaman

<sup>3</sup> This document is a project editor's discussion of, and proposed resolution to, ballot comment #15, which itself <sup>4</sup> was a request to implement maintenance request 0286. This comment and the others received on this ballot <sup>5</sup> can be found in the proposed disposition of comments (later revisions of the proposed disposition may be <sup>6</sup> found in the same directory):

7 https://www.ieee802.org/1/files/private/q-rev-drafts/d0/802-1Q-rev-d0-4-pdis-v1.pdf

8 An earlier draft of this document was discussed during the May 2021 interim sessions of the Maintenance

9 Task Group (the BRC for this ballot).

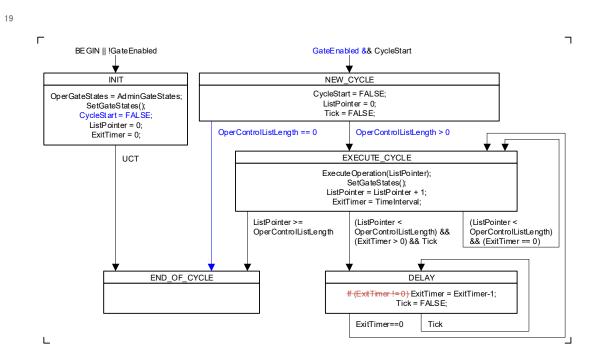

10 I propose that we adopt the replacement Figure 8-20 shown in this document (with <u>insert</u> and <u>strikeout</u> for 11 suggested technical changes) for the next WG recirculation ballot. Notes on the changes from the 12 P802.1Q-Rev/D0.4 version follow the figure, and include notes on the changes from the first proposed 13 change. Minor editorial change suggestions for readability are not shown. These include consistency of test 14 conditions in transitions and consistency of variable setting order in states. Since the actions in each state are 15 specified as occuring atomically and the state machine definition further requires that the entry condition to 16 the state be true when that atomic execution takes place,, these readibility changes have no technical effect.

## 17 Please note that there is a substantive issue outstanding, which is (or will be) the subject of a further 18 maintenance item: see discussion point 5 below.

20 The proposed replacement Fig 8-20 (above) differs slightly from the recorded resolution of maintenance 21 request.

1. The state machine conventions (see Annex E of 802.1Q) do not specify behavior when both UCT and another condition are True for exit from a state. Other descriptions of this state machine logic have maintained that the choice of next state is undefined when multiple conditions apply. Annex E does specify the use of ELSE, which would resolve the issue in the present case. However explicitly representing the

two cases of a zero and non-zero list would seem to be clearer in this case.

1 2. Given that clarification it would be possible to simply not leave the NEW\_CYCLE state at all if the list length is zero, but this would risk leaving the state at an unaligned time when the list length was changed, and the

is zero, but this would risk leaving the state at an unaligned time when the list length was changed, and the

END OF CYCLE state (which has no action, and could have been omitted) was presumably included for

4 clarity of documentation.

53. The state machine behavior in the case of !GateEnabled and CycleStart both being True is undefined [BEGIN is special by convention (and it and open transitions in general should be better described in 6 Annex E, but that should be left for another day) and does not suffer from this problem. In general state 7 machines should follow the rule that correctness is a local property, and in this case of this machine the 8 issue is not resolved within the set of related state machines as none of the machines appears to control 9 the relationship between GateEnabled and CycleStart. I believe it is the case that NEW CYCLE should 10 not be entered if GateEnabled is False. The open entry to NEW CYCLE is then best qualified 11 GateEnabled && CycleStart. To guard against a randomly time start occuring due to a transition to 12 GateEnabled True revealing a previous CycleStart it would also seem wise to reset CycleStart in INIT. 13 Notionally the open transition to INIT continuously executes the INIT actions so that the variables set/reset 14 in that states actions will have the assigned values up to the point that BEGIN becomes False and 15 GateEnabled becomes True. 16

17 4. The test (ExitTimer != 0) was unnecessary in state DELAY. The state will not be entered if ExitTimer is not greater than zero. If there is any worry about failure to evaluate ExitTimer == 0 to exit the state after the

rate actions set Tick = FALSE then the Tick exit could be qualified with (ExitTimer <math>!= 0), but that would be

20 an unusual interpretation of the machines.

21 5. The issue: the current understanding of the editor this is that the desired timing of each successive ExecuteOperation(..) is meant to be (for some at least) in synchronized time, while the Tick specified is an approximation (and unless the Tick occurs at the finest granularity of synchronized time possible the whole notion of counting down using a Tick that is not itself synchronized with synchronized time would by its nature yield an approximate time, even if the duration of the Tick was precise). The Editor does not see how this issue can be fixed by simple changes to the figure and it probably has much wider consequences, outside of the scope of the current ballot resolution

28