# 100GBASE-KP4 Transmitter Characteristics Ad Hoc

#### 24 Oct, 2012

IEEE 802.3bj 100GBASE-KP4 TX Ad Hoc

- This call is an IEEE appointed ad hoc.

- The meeting rules apply regarding IP, cost, confidential clauses, etc.

#### Attendance

- If you are on the call, please send me an email

- \* 6 to mute and unmute

# Agenda

- IEEE patent policy reminder <u>http://www.ieee802.org/3/patent.html</u>

- Open Action Items

- Rise time vs linear fit (Charles Moore)

- 100GBASE-KP4 training frame updates for full state pinning (Adee Ran)

- Discuss next steps

# **Open Action Items in Ad Hoc**

- First analysis of transition times from linear fit (Charles Moore)

- Training to data mode initialization with termination bits (Adee/Kent)

- Training pattern seed structure changed based on partial state to full state pinning (Adee/Kent)

- Example training frame sequence (Adee/Kent)

- Pk-pk limit approach is different from Clause 93. (TBD)

- Investigate linear fit pattern (Adee/Kent) in 2 weeks

- Coef ratios for INITIALIZE (Kent Lusted) in 2 weeks

- Report out discussion on overhead bits (Zhongfang Wang and Matt Brown)

#### Linear Fit Update – Charles Moore

See risetime\_vs\_fit\_pulse.pdf

### **Training Pattern Update**

• See pages 8-15

IEEE 802.3bj 100GBASE-KP4 TX Ad Hoc

#### 100GBASE-KP4 Training Frame Update Goals

- Use full-state pinning termination in Draft 1.2

- 1 PAM4 symbol (termination) with bits taken from known PRBS sequence

- 45 PAM4 symbols precoded

- Enable locking on termination PRBS during training

- Essential for data decoding

- Make training frame same size as PMA frame

- Simplifies implementation

- Use PAO for EEE ALERT frame only

- Maintain spectrally rich, DC balanced and uncorrelated lane sequences

# 100GBASE-KP4 Precoding changes from D1.2

- Training frame word (TFW) is still 46 UI

- Now TFW is same size as D1.2 termination block

- In D1.1, 1 TFW = 2 TB46

- TFW is now created from 92 bits of PRBS13 at a time (instead of 45 bits at a time in D1.1)

- Gray coding results in 46 bit-pairs

- First pair is used for initializing the precoder state

As per 94.2.2.6

- The remaining 45 pairs fed through the precoder

- As per 94.2.2.6

### Frame size changes from D1.2

- Propose to increase training pattern length to 338 TFWs

- Requires 338\*92=31096 bits from PRBS13

- PRBS13 full cycle is 8191 bits

- Use 3 full cycles + 4<sup>th</sup> cycle truncated to 6523 bits

- Bits from 2<sup>nd</sup> and 4<sup>th</sup> cycles are inverted

- Added to marker and control channel (10 TFW together), the new training frame is 348 TFWs, which is equal to the PMA frame size

# Transition from training to data

- Training frame is always aligned with the PMA frame; last training frame is immediately followed by 40-bit overhead of data

- No need for PAO field in training (only in EEE alert)

- Countdown field still used to signal transition

- 40-bit overhead should start with a termination symbol to be consistent; otherwise data should start with the termination symbol preceding the 40-bit overhead

- PRBS13 is re-seeded at the beginning of each training sequence during training mode, but keeps running freely in data mode

- Termination bits get synced during training

- PRBS always advances 92 bits per TFW in training and by 92 bits per term block in data mode

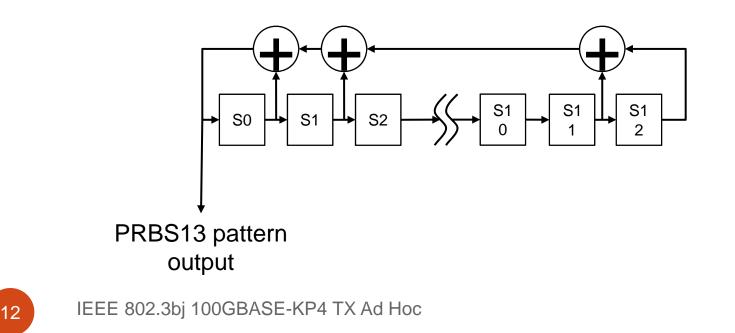

#### **PRBS** generator change

- Modified Fibonacci polynomial: G(x)=1+x+x<sup>2</sup>+x<sup>12</sup>+x<sup>13</sup>

- Old one was G(x)=1+x+x<sup>2</sup>+x<sup>11</sup>+x<sup>13</sup>

- Required to enable creating 4 DC balanced, quasiwhite, non-correlated sequences

# Initial outputs

- The *initial outputs* of the PRBS13 generator, right after the control channel transmission, shall be different for each of the PMD lanes, as follows (LSB transmitted first)

- PMD lane 0: 0x<u>C</u>D92

- PMD lane 1: 0x2AFB

- PMD lane 2: 0x<u>C</u>3D3

- PMD lane 3: 0x<u>E</u>2F6

- Generator is re-seeded to same values at the beginning of every training frame pattern

#### Initial sequences

k25

| Lane                                | Output of | Contents of first 2 TFWs (from left to right)                                                    |

|-------------------------------------|-----------|--------------------------------------------------------------------------------------------------|

| LO                                  | PRBS      | 010010011011001111000101010100001001001                                                          |

|                                     | Gray code | 103132022011113010312123121001210212102                                                          |

|                                     | Precoder  | 1301200200101031003201123322233220110021032320<br>0111101103333223211121021130331123112233001211 |

| L1                                  | PRBS      | 1101111101010100000010010011011001111000101                                                      |

|                                     | Gray code | 2122111000310213123033320031023220233002331323<br>3120203323022233232122330321221022131113120312 |

|                                     | Precoder  | 2333232222100230112212113123112022030002123021<br>3200221203111121120111213023332202301012331233 |

| L2                                  | PRBS      | 11001011110000111110111011101100110011                                                           |

|                                     | Gray code | 20322002232323202020230230200202323002020023<br>0213013033201310233330203100231232333202031111   |

|                                     | Precoder  | 2211131112033022002203112200022203300022000021<br>023001221200123112123312313301120303311301010  |

| L3                                  | PRBS      | 011011110100011110111110101100110111111                                                          |

|                                     | Gray code | 1322101232233202122302213323220301130320332230<br>3113322033113031220033211310222011132331011220 |

|                                     | Precoder  | 1202310211121133202133321203331223213022120213<br>3230333121012210200030232100202232302123101113 |

| IEEE 802.3bj 100GBASE-KP4 TX Ad Hoc |           |                                                                                                  |

#### Slide 14

#### k25 underline first symbol to indicate precoder init per 94.2.2.6?

#### put arrows denoting order

note first and 2nd TFW kclusted, 10/24/2012

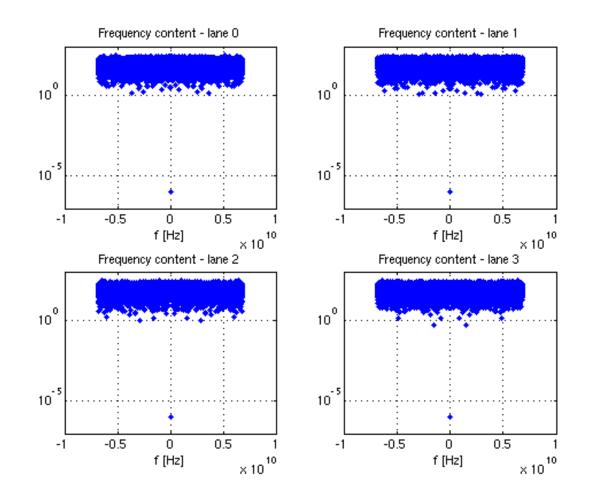

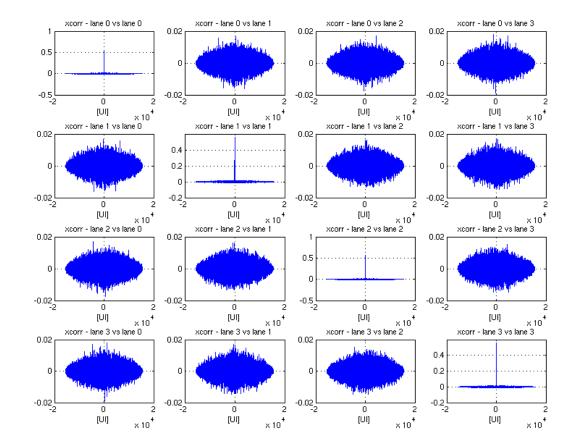

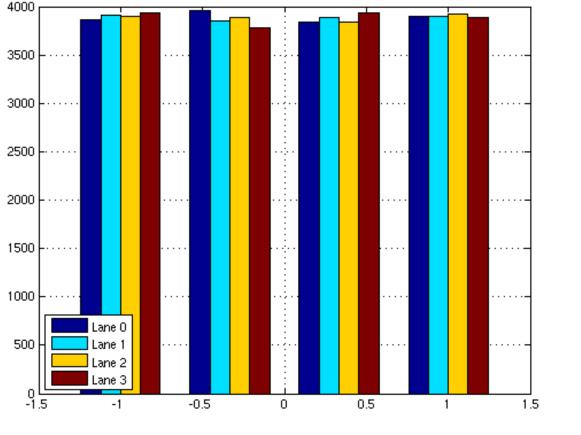

# Training pattern features

- The resulting sequences are DC balanced, quasiwhite and have low correlation between lanes

- Distribution of voltage levels is nearly uniform

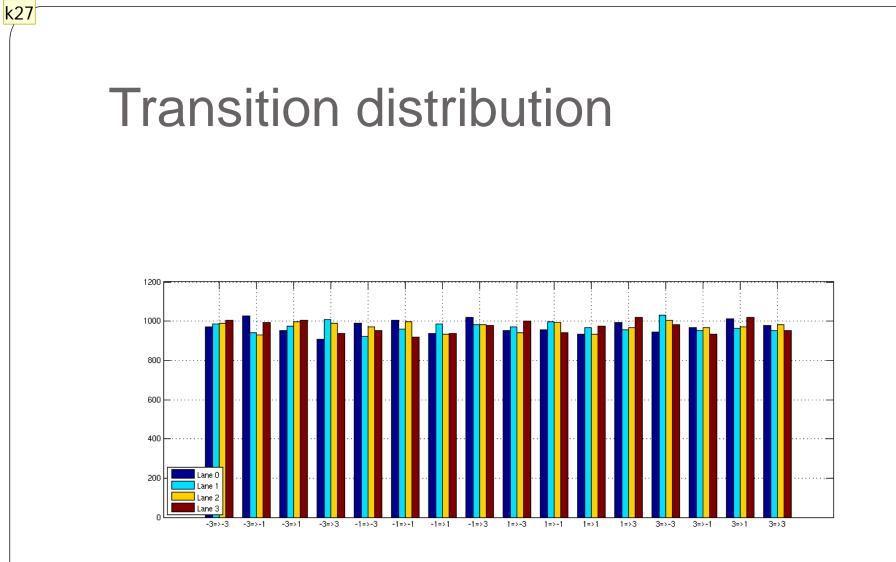

- Distribution of transitions between level is nearly uniform

#### Discussion

IEEE 802.3bj 100GBASE-KP4 TX Ad Hoc

### BACKUP

# Patterns are quasi-white and DC balanced

IEEE 802.3bj 100GBASE-KP4 TX Ad Hoc

#### Low correlation between lanes

IEEE 802.3bj 100GBASE-KP4 TX Ad Hoc

#### Level distribution

PRBS pattern portion only

Slide 21

| k27 | of pattern only      |

|-----|----------------------|

|     | kclusted, 10/22/2012 |