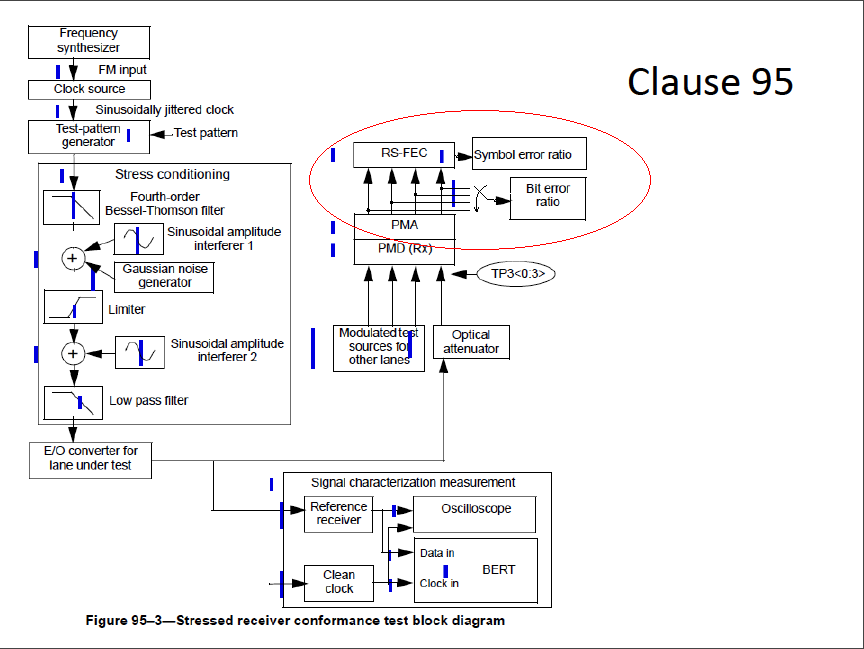

I think the switch is in the wrong place. It needs to be on the input to the PMD/PMA not on the input to the BER.

I agree that the sinusoidal inteferer 1 also creates jitter, however in clause 87 it has frequency between 100MHz and 2GHz which is above the typical FM modulation bandwidth of pattern generators and is being used to create additional high probability jitter that no CDR is expected to track. The FM input jitter is speced to follow the curve in amplitude and frequency for jitter tracking purposes.

Mike Dudek

QLogic Corporation

Director Signal Integrity

26650 Aliso Viejo Parkway

Aliso Viejo CA 92656

949 389 6269 - office.

From: Dan Dove [mailto:dan.dove@xxxxxxxxxxxxxxxxxx]

Sent: Friday, March 28, 2014 10:51 AM

To: Mike Dudek; STDS-802-3-100GNGOPTX@xxxxxxxxxxxxxxxxx

Subject: Re: [802.3_100GNGOPTX] MMF ad hoc - Thursday 27th March 2014 - SRS test diagram update

Jonathan,

I probably should have been more involved in the call, but was forced to listen while driving.

I agree with Paul's comments and illustrated how I might change the drawing below. Note the switch indicating that all lanes are selectively tested for BER versus the graphic implication that only one lane is tested.

In addition, I guess I don't get why you insert a sinusoidal amplitude source before the limiter. Is this not equivalent to just adding more sinusoidal jitter? I would expect the limiter to eliminate any amplitude interference and only leave phase interference.

Dan Dove

Chief Consultant

Dove Networking Solutions

530-906-3683 - MobileOn 3/28/14 9:01 AM, Mike Dudek wrote:

I agree with Paul’s comments.

I also re-read clause 87 to determine why the diagram shows the use of the “Clean clock” for the signal characterization in figure 87-3. The reason is that figure 87-3 is only used to measure J2, J9 and VECP when the sinusoidal jitter input frequency is “well within the 4 MHz to 10times LB”. (ie it is intend to be at a frequency that the CDR in the Rx can’t track). We need to make sure that this aspect of the test methodology is preserved in clause 95 (eg by referencing clause 87) when using this diagram.

Mike Dudek

QLogic Corporation

Director Signal Integrity

26650 Aliso Viejo Parkway

Aliso Viejo CA 92656

949 389 6269 - office.

From: Kolesar, Paul [mailto:PKOLESAR@xxxxxxxxxxxxx]

Sent: Friday, March 28, 2014 5:50 AM

To: Jonathan King; STDS-802-3-100GNGOPTX@xxxxxxxxxxxxxxxxx; a_flatman@xxxxxxxxxxxxx; Abbott, John S Dr; Amezcua, A. (Adrian); Andy Moorwood; Anslow, Peter; Anthony Torza; Bernstein, Gary; Ephrem Wu; Gary Nicholl (gnicholl); Harry Fu; Jack Jewell; Jeffery Maki; John Petrilla; Keith Nellis; Lian Zhao; Martin Gilpatric; Phil.McClay@xxxxxx; Mike Peng Li; Mike Dudek; mnowell@xxxxxxxxx; Oren Sela; Patrick Decker; Rabinovich, Rick (Rick); Rick.Pimpinella@xxxxxxxxxxx; Robert Coenen; ryan.latchman@xxxxxxxxxxxxx; Scott Kipp; Shmuel Levy; Swanson, Steven E; Tracy, Nathan L; Vipul Bhatt

Subject: RE: [802.3_100GNGOPTX] MMF ad hoc - Thursday 27th March 2014 - SRS test diagram update

Jonathan,

Thanks for your agile on-the-fly edits during yesterday’s call. The new diagram seems to reflect what we agreed during that call. I’ve just a couple touch-ups to suggest.

1. The “Symbol error ratio” and “Bit error ratio” test outputs should be presented with equivalent appearance. Specifically, they should both be shown within boxes or without boxes. My interpretation of the other boxes is that each represents a hardware entity. However, these test outputs do not. Therefore I recommend removal of the box around “Bit error ratio”.

2. The format of arrow pointing to “Symbol error ratio” is unlike all others. Unless there is a good reason for this distinction, I’d recommend making it the same as the others.

Regards,

Paul

From: Jonathan King [mailto:jonathan.king@xxxxxxxxxxx]

Sent: Thursday, March 27, 2014 7:58 PM

To: STDS-802-3-100GNGOPTX@xxxxxxxxxxxxxxxxx; a_flatman@xxxxxxxxxxxxx; Abbott, John S Dr; Amezcua, A. (Adrian); Andy Moorwood; Anslow, Peter; Anthony Torza; Bernstein, Gary; Ephrem Wu; Gary Nicholl (gnicholl); Harry Fu; Jack Jewell; Jeffery Maki; John Petrilla; Keith Nellis; Kolesar, Paul; Lian Zhao; Martin Gilpatric; Phil.McClay@xxxxxx; Mike Peng Li; mike.dudek@xxxxxxxxxx; mnowell@xxxxxxxxx; Oren Sela; Patrick Decker; Rabinovich, Rick (Rick); Rick.Pimpinella@xxxxxxxxxxx; Robert Coenen; ryan.latchman@xxxxxxxxxxxxx; Scott Kipp; Shmuel Levy; Swanson, Steven E; Tracy, Nathan L; Vipul Bhatt

Subject: RE: [802.3_100GNGOPTX] MMF ad hoc - Thursday 27th March 2014 - SRS test diagram update

Dear all

Following today’s MMF ad hoc review of the Stressed receiver conformance test diagram which will go into clause 95, here is an updated figure, implementing all the changes we’d agreed to during the call. The last slide is the crudely edited diagram we ended up with by the end of the call today, the first slide is the cleaned up version.

Please let me know

Thank you all for your participation this morning !

Best wishes

jonathan

Patrick Decker Hardware Engineer Oracle O: 408-276-0459 F: 408-276-3006 M: 404-388-8540