# **CAUI Loss Budget**

July 26 2012

# Agenda

- Recap and new presentations

- latchman\_01\_0312.pdf

- ghiasi\_02a\_0712.pdf

- CAUI4 options (Tom Palkert)

- Discussion

# Latchman\_01\_0312 Recommendation

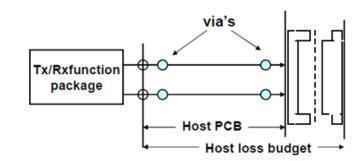

- Host Loss Budget: 8.5dB at 12.89GHz

- •includes PCB loss, two sets of vias and mated connector

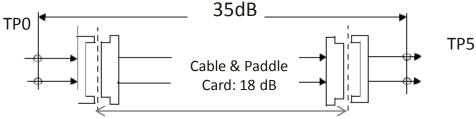

CR4 Budget: 5 m cable assembly link budget example with 8.5 dB host loss: 35 dB @12.89 GHz (FEC Required)

Nasdaq: MSPD

## Ghiasi\_02a\_0712 Summary

#### **CAUI-4 Applications** Chip to module applications supporting 250 mm Chip to chip applications supporting 300 mm 300 mm Switch/ Switch/ 200 mm ASIC ASIC Switch/ Mezzanine card ASIC 250 mm 300 mm Switch/ Switch/ ASIC ASIC

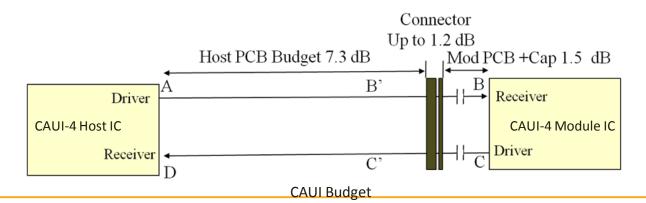

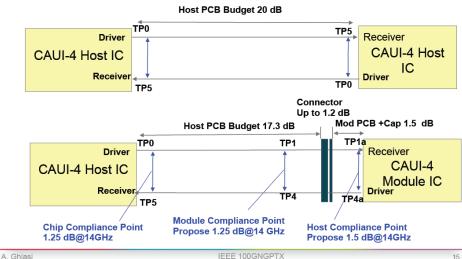

#### **Proposed CAUI-4 Architecture and Reference Points**

Following 802.3 CL83A/B (CAUI) where common I/O supports chip to chip and chip to module

A. Ghias

### Conclusion

Have a nice day

### Discussion

- Keep chip-module CAUI 4 budget as is and have one budget

- Repeaters for channels which do not meet budget

- Keeps common port for copper and optics

- Increase CAUI 4 chip-module budget

- Higher power module unless asymmetric interface is possible

- Lose common port with CR4 for that port type (interop issues)

- Consensus that a solution which is interoperable is required

- Add another CAUI 4 chip-module budget

- Lose common port with CR4 for that port type (interop issues)

- Make chip to chip spec different loss from chip to module

- Compliance points would be different relative to chip-module but would allow for higher loss budgets