# 100G-SR4 Link Modeling

Paul Kolesar, CommScope IEEE 802.3 Next Generation Optics Study Group September, 2011

#### **Objective & Methodology**

- Explore parameter space to establish possible solutions for supporting various reach targets for 850 nm systems at 25.8 Gbaud

- Exercise IEEE link model under certain assumptions

### Assumptions

- Clock recovery required (at this time)

- Jitter budget is biggest impairment for 100G-SR10

- VCSEL speed and spectral width are key performance concerns

- Reported speeds not scaling proportionally to 25G

- Spectral width relaxed by >40% for 100G-SR10

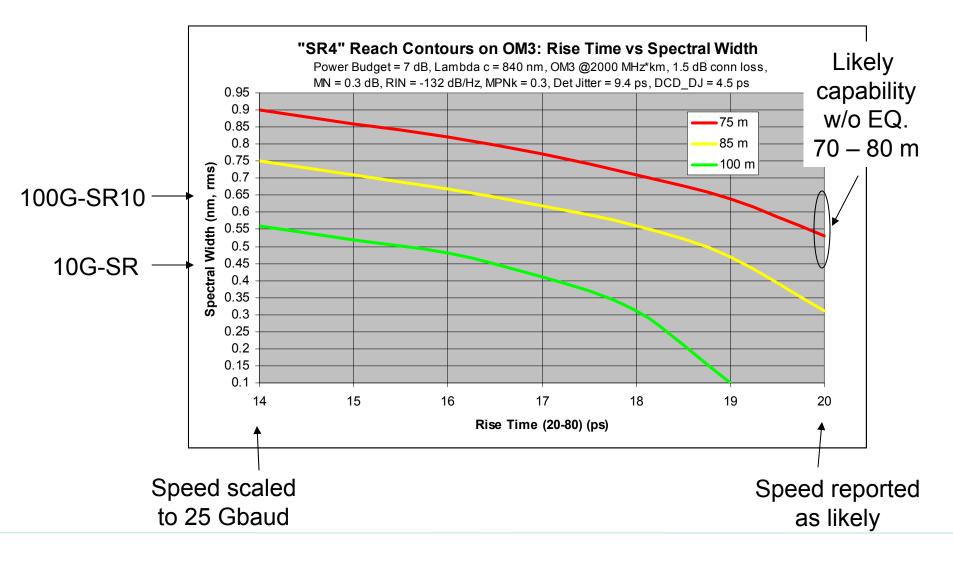

#### **OM3 Reach Contours**

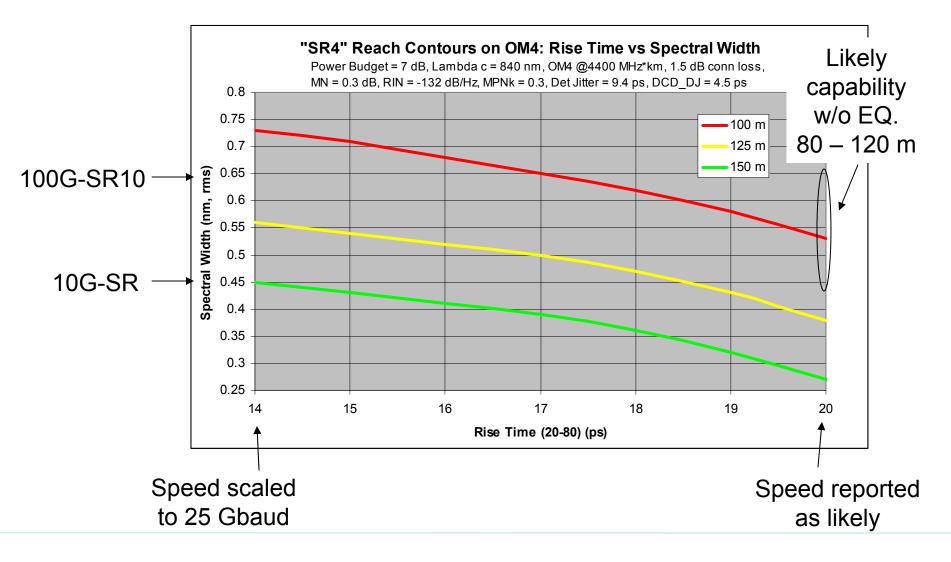

#### **OM4 Reach Contours**

#### Equalization

- Modest equalization would compensate slow VCSELs

- Explore fixed-coefficient 1- and 2-tap DFE

- With clock recovery employed, fixed DFE is incremental

- Modest EQ would allow seamless upgrade path

- 40GBASE-SR4 to 100GBASE-SR4

- Without change to cabling

- Without reconfiguration of data center

#### Thank You

## **COMMSCOPE**°