# Considerations on MB810 Decoder for 10 GbE

ChanGoo Lee\*, Yong Woo Chae\*, Dae Young Kim\*\*, Hae Won Jung\*, Hyeong Ho Lee\*

\*ETRI, \*\*CNU in Korea

e-mail: cglee@etri.re.kr

### **Abstract**

We made a decoder logic of MB810 for high-speed data. MB810 decoder can be implemented by combinational logic that accelerates data processing speed. However, it is required to consider fan-out of gates. We took into consideration the driving capabilities of general logic gates and assigned codeword so that the decoder logic can be simplified into XOR combinations.

We also suggest that MB810 use the same Comma as that of 8B/10B and give an example of Comma detection of MB810.

# **CONTENTS**

- 1. Decoder Logics for MB810

- 2. Comma Detection in MB810

- 3. Co-Existence with 8B/10B

- 4. Conclusion

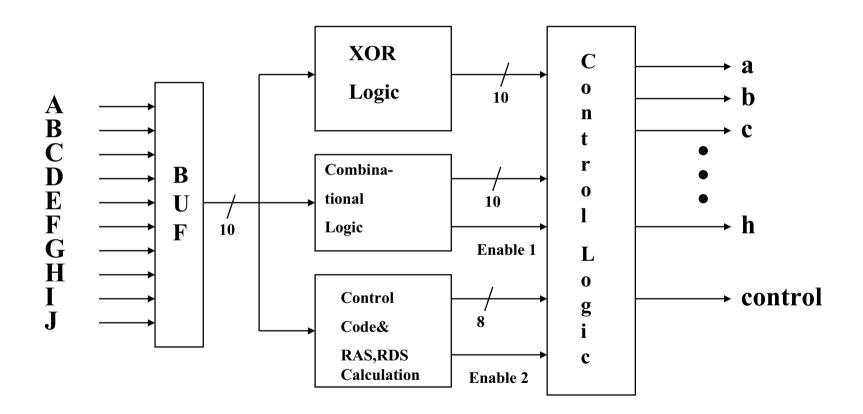

## **Decoder Logics for MB810**

- At last November meeting, We presented MB810 decoder running at 12.5Mbps, which was implemented in FPGA.

- MB810 Decoder is independent of the encoding state and so can be implemented with combinational logics only.

- Considering high speed data received, fan-outs may cause an abnormal operation of gates in chips.

- -We present a mapping rule in MB810 encoder to solve the above problem.

# **Decoding Rule**

Decoded data: abcdefgh (8 bits)

code-word: ABCDEFGHIJ (10 bits)

#### **Decoding Rule:**

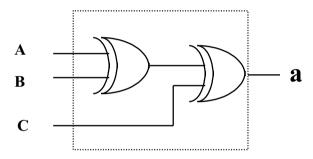

$a = A \times B \times C$

b = B xor C xor D

c = C xor D xor E

$d = D \times E \times F$

$e = E \times F \times G$

$f = F \times G \times G$

g = G xor H xor I

h = H xor I xor J

# Assignment Results

|          | S1  | S2  | S3  | S4  | S5  | S6  | S7  | S8  | S9  | S10 | S11 | S12 |  |

|----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--|

| V        | 196 | 214 | 226 | 194 | 221 | 228 | 228 | 222 | 194 | 226 | 220 | 196 |  |

| <u> </u> | 170 | 211 | 220 |     |     |     |     |     |     |     |     | 170 |  |

| N        | 60  | 42  | 30  | 62  | 35  | 28  | 28  | 34  | 62  | 30  | 36  | 60  |  |

| R        | 86  | 128 | 152 | 82  | 134 | 166 | 164 | 135 | 83  | 151 | 147 | 86  |  |

|          |     |     |     |     |     |     |     |     |     |     |     |     |  |

Sn: State

Y: # of codewords assigned with the preferred mapping rule

N:# of codewords assigned otherwise

R: # of codewords unused

# Decoder Block

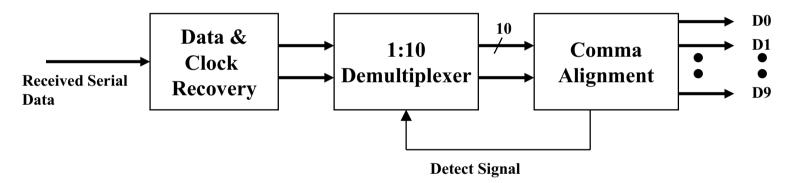

### **Comma Detection in PMD**

**Suggestion: Use 10 bits in Comma code detection**

Comma codes: 1100000101 or 0011111010

- Comma pattern should not be generated in any data sequences.

- For that purpose, Comma is generally chosen among violation codes.

- In MB810 line code, 1100000101 and 0011111010 are not violation codes.

- However, Comma codes can be assigned the same as those of in 8B/10B when we use all of 10 bits to declare the detection of Comma codes.

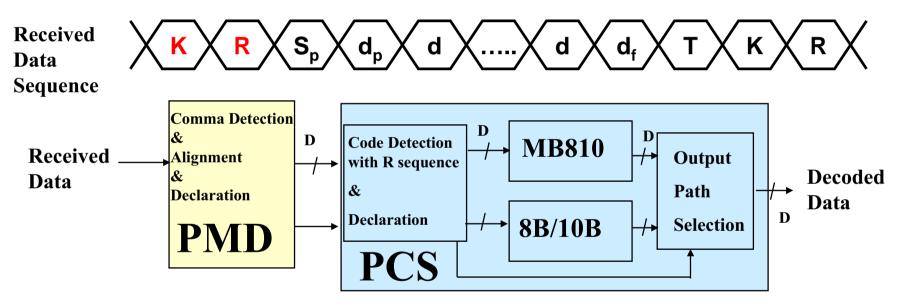

### **Sharing the Same PMD with 8B/10B**

• When we use the same Comma codes as in 8B/10B, both codes can be used in PCS

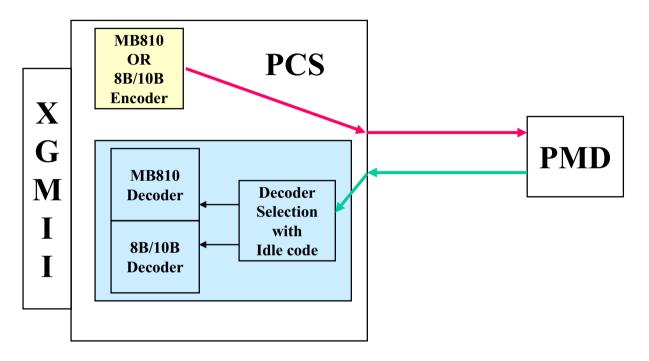

### An Architecture of PCS

- In PCS data reception, the code in use is discriminated by monitoring the Idle data pattern.

- We can use the same PMD if we choose common comma words, with but a small increase in gate counts(several K).

# **Conclusion**

- MB810 Decoder can be implemented in simple combinational logic gates but we need to consider the fanouts of gates in chips for processing high speed data.

- Using common comma words is a good way to promote 10GbE standard. Customers just use the same PMD and PCS chips without concerning about the used coding algorithm.

- We suggest to use all of 10 bits in Comma words to declare the detection.