### **10GbE Serial Technology Proposal**

#### Presentation To IEEE July 7, 1999

Frederick Weniger Gigabit Product Marketing Manager Vitesse Semiconductor Corporation

# **Proposed 10GbE Standard Interfaces**

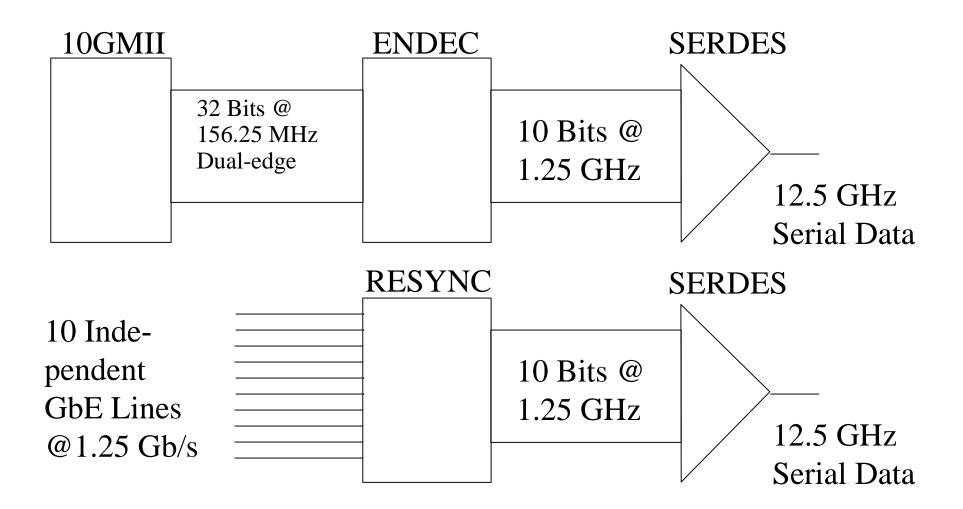

- □ 32 Bit Bus@156.25 MHz Dual-Edge

- Wide, Low Speed

- Simple CMOS I/F

- No Data Skew Concerns

- □ Ten Bit Interface (TBI)

- Standard, Familiar I/F

- Existing Technology Absorbs Data Skew

- Multi-Purpose (SerDes & Mux/Demux) Broader Market, Lower Cost

- □ Serial Optical (12.5 Gb/s)

- Achievable Today

- Major Industry Drive To Lower Cost Of Optics

- Point-To-Point No Central Timing Constraints

### **10GbE Interface Definitions**

Frederick Weniger Product Mktg Mgr

# **PHY Comparison (W/O Optics)**

| Coding       | <u>8B/10B</u> | <u>Scrambling</u> | Scramb +FEC |

|--------------|---------------|-------------------|-------------|

| Data Rate    | 12.5          | 10.0              | 10.0 + ?    |

| Edge Density | Highest       | Lower             | Lower       |

| DC Balance   | Short Term    | Long Term         | Long Term   |

| Gate Count   | Low           | Low               | High        |

| Power        | Low           | Low               | High        |

| Latency      | Low           | Low               | Higher      |

| Synchron     | Fastest       | Slower            | Slowest     |

## Comparison: 4 x 2.5 vs 10 x 1.25

<u>4 x 2.5</u>

10 Gb/s Link Single Ser/Des 8B/10B Coding Scrambling Optical Link Multi-Vendor CMOS EnDec ASIC Integratable 4 Serial Streams Hard/Hard Requires Striping Even Soon (WDM) Not Yet Yes (.18um) Later

#### <u>10 x 1.25</u>

10-bit bus Easier/Easier Simple, Ideal Fit Even Now (Parallel Links) Yes Yes (.35um) Now

4 x 2.5:

Feature

WDM-Oriented

4 Separate Streams, Not A Bus

Not Intended To Connect To A SerDes

10 x 1.25:

Easiest To Connect To A SerDes

Straightforward 8B/10B @ 12.5 Gb/s

Can Be Implemented As Synchronous Bus

# **In Conclusion**

- □ We Believe At Least Two, If Not Three I/Fs Should Be Defined

- □ 32-Bit Bus Plus Control Bits Are A Natural Fit

- □ Consider Carefully The Nature Of 4 x 2.5 vs 1 x 10 Gb/s W/TBI

- Really Is 4 Separate Streams vs One Serial Stream From Synchronous Bus

- □ On 8B/10B vs Scrambling

- We Can Support Either One

- Mainly Affects Optical Component And Media Mfrs

- We Need To Hear More From Them

- Excellent Timing Between Standardization Process And Broad Product Availability

- 10 GbE Should And Ultimately Will Be <u>Optimized</u>, Not <u>Compromised</u>