# MII Issues for 10Gb/s Operation

3 June 1999 HSSG Coeur d'Alene, ID

Robert M. Grow bob.grow@intel.com 619-487-9320

#### **Contents**

- Proposed Objective

- MII and GMII Operation

- HSSG MII "Requirements"

- Multi-Octet Interface Issues

- Conclusion

## **Proposed Objective**

Include a specification for an optional Media Independent Interface

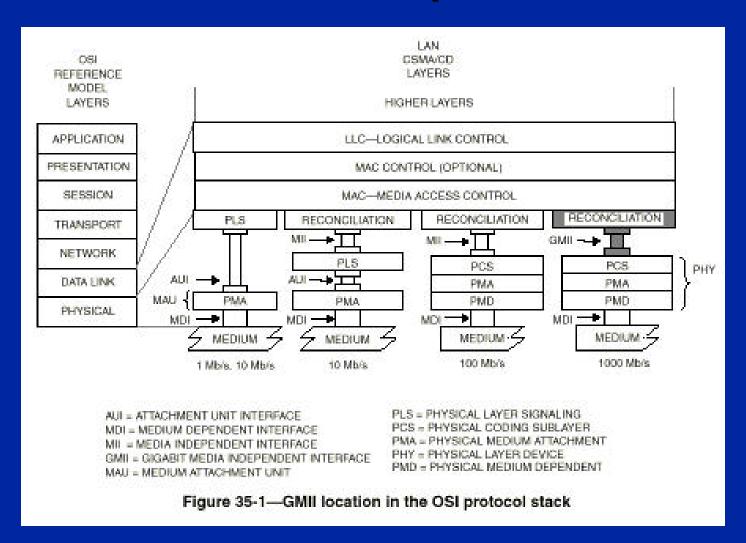

## 802.3 Architecture (1000BASE-X)

## Why an MII?

- Separates MAC and PHY for ease of specification and implementation

- Solve problems common to different PHYs

- Common management framework

- Simplifies specification

- Decouple development of MAC and PHY components

- Easier addition of a new PHY to the standard

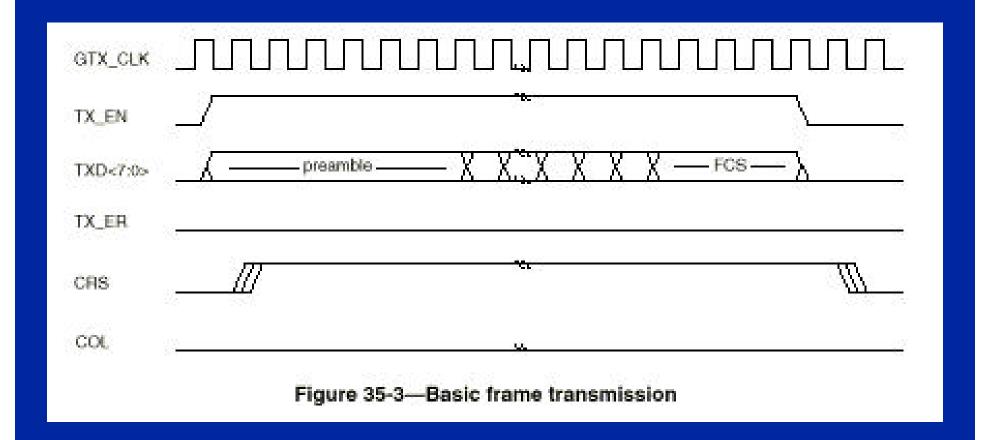

### **GMII Transmit**

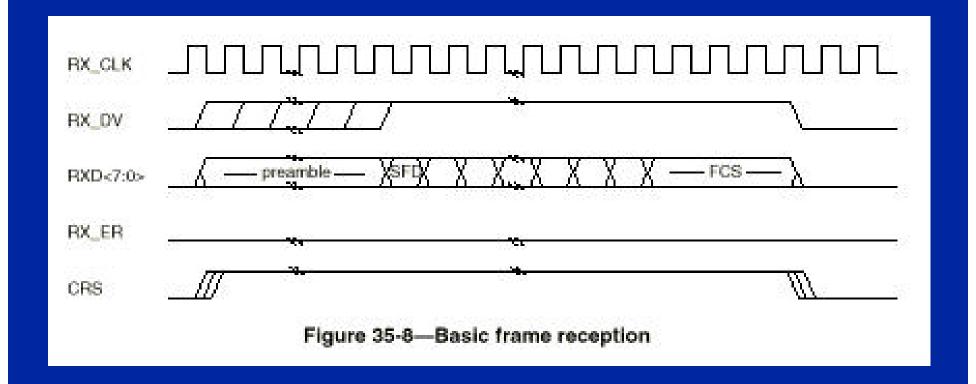

#### **GMII Receive**

## Reconciliation Sublayer

- Architectural entity that adapts the bit serial MAC of clause 4 (with its bit serial PLS Service Primitives) to the 4-bit wide MII and 8-bit wide GMII

- Includes mappings to service primitives specified for higher speeds (clause 22, clause 35)

## **HSSG MII "Requirements"**

- Capable of supporting: 10 Mb/s, 100 Mb/s

1000 Mb/s and ~10,000 Mb/s data rates.

- Allow practical implementation as on-board chip-to-chip interface.

- Precisely delimit frame lengths.

- Allow block code and word oriented PCS.

- Support existing management interface and register set.

- Not required to support multiple PHYs.

## **Some Options**

- Use existing GMII

- -1250 MHz for 10 Gb/s

- Limits implementation technologies (cost)

- Avoids complexity of a multi-octet interface width

- Go wider and faster

- -32-bit ≥312.5 MHz for 10 Gb/s

- -64-bit ≥156.25 MHz for 10 Gb/s

#### **Multi-Octet Issues**

- Creating a word orientation within 802.3 has wide ranging implications

- The MII is not the only thing that brings up the issues of word orientation

- There is experience with 16- and 32-bit wide MAC designs, and implementers will not want to be restricted to an octet MAC implementation

- We had the 2-byte ordered set in 1000BASE-X

- Some WDM proposals create the same problems

- PHY proposals must balance the implementation trade-offs (e.g., compressed IPG for SONET)

#### **Data Stream**

- 802.3 does not easily support a word width

- Legacy 802.3 is octet oriented

- Word orientation properties cannot be depended on with optional MII

- Interframe and preamble lengths might change between transmit and receive

- A word oriented PCS may require preamble shrinkage

- An odd data length must change inter-frame

#### **Frame Delimitation**

- Multi-octet interface doesn't match octet nature of 802.3 framing

- Additional signal are required to indicate valid data, e.g., RX\_V<3:0>

- Requires some interframe to align next frame

- Requires at least one word of preamble + Start Frame Delimiter to align Destination Address

#### **Multi-Octet Characteristics**

- Assume MAC is word aligned with MII

- 4-octet is a fairly natural width, 8-octet moves Type/Length field within word

- -Preamble + SFD = 8

- -DA + SA = 12

- -VLAN tag = 4

- 4-octet allows preamble shrinkage, while 8octet does not

- A multi-octet interface would affect granularity of shrinkage or expansion

#### Conclusions

- GMII is possible but limits technology

- 4-octet width is "bleeding-edge" for high density logic

- 8-octet width produces most dramatic changes in handling of interframe gap and preamble

#### **TANSTAAFL**

(There Ain't No Such Thing As A Free Lunch)