#### Thoughts on Low-pin-count Low-power Media Independent Interface

Fort Worth September, 2016

Jay Cordaro, Pat Thaler Broadcom Limited

## **Contributors and Supporters**

#### Contributors

Mehmet Tazebay, Broadcom Limited Mehdi Kilani, Broadcom Limited

#### Supporters

Bernd Körber, FTZ Zwickau

Dinh Thuyen, Pulse

Dongok Kim, Hyundai

Hideki Goto, Toyota

Farid Hamidy, Pulse

Jinhwa Yun, Hyundai

John Hess, Bel Fuse

Version 1.0

Ahmad Chini, Broadcom Limited

Kirsten Matheus, BMW

Nobukatsu Kitajima, Renesas

Stefan Buntz, Daimler

Sterling Vaden, Surtec Industries

## Agenda

- Overview

- Goals & Assumptions

- Media Independent Interface Options

- Conclusions

## Overview

- The standard Clause 22 MII interface, operating at 10Mbps requires 14-16 pins.

- Industry standard **RGMII** requires 12 pins.

- Some targets of 10Mbps single pair will not have integrated PHYs and will have a price point which requires keeping pin count down and implementation complexity as low as possible to meet the cost objective.

## **Goals and Assumptions**

- While some targets are cost constrained, other targets require a MAC interface which is already standardized, namely MII.

- The goal of this presentation is not to preclude implementation of a 10SPE PHY with MII.

- Rather, it is to suggest feasibility for a low-power, low-pin count MAC interface for those cost constrained nodes which require it.

- This presentation enumerates some MAC interface possibilities "xMII" where xMII is used for a generic media interface.

## MII

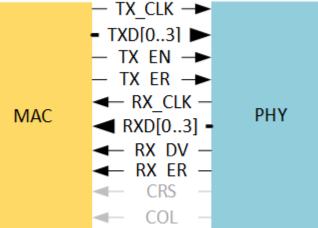

- **MII** interface defined for 100Mbps operation. It has 16 pins.

- If half duplex capability is eliminated (MII-Lite),

14 pins are required.

IEEE 802.3 10SPE Study Group – September 2016 Interim

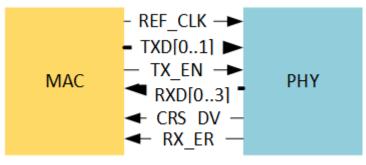

## RMII

- Industry standard RMII was defined to save pins vs.

MII. It requires 8 pins and the clock runs at 50MHz, 10Mbps data is repeated 10 x.

- 50MHz can increase emissions.

- Repeating data **10x** is wasteful.

## xMII Option: DME

- One option for a low-pin count interface between the MAC and the PHY is to utilize Differential Manchester Encoding (DME).

- DME is used in Clause 73 and Clause 98

- Self-synchronizing, eliminates need for clock. Could drive single-ended with 2 pins, or differential with 4.

- More complex and **EMC** may be a concern

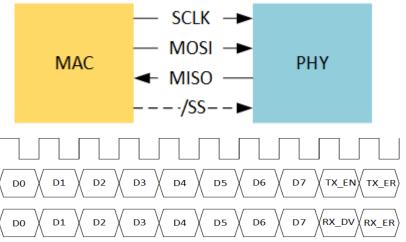

## xMII Option: SPI

- SPI is used for many microcontroller peripherals including moderate-rate ADCs and is defined in SDIO (SD Card specification)

- Widespread use in various technologies

- 3-4 pin serial interface:

- SCK Provided by MAC controller (Master)

- MOSI (Master Output, Slave Input)

- MISO (Master Input, Slave Output)

- /SS Slave Select

- Data pins could send 10 bits per data octet @ 12.5MHz SCK, with TX\_EN, TX\_ER RX\_DV, RX\_ER added at end of octet.

- If clock stops when no data transferred to save power, may require additional pin to signal to MAC to start clock.

## xMII Option: SPI-like Variants

- Many possible variations on **SPI**:

- Can make the **PHY** the master instead of the **MAC**

- Run double data rate (1 bit transferred per level change

- Use Clock line to indicate start of packet.

- SPI may provide a starting point for a reduced-pin xMII.

#### Media Independent Interface Options

| xMII                   | # of PINS | Clock                    | Complexity | EMC<br>Concern |

|------------------------|-----------|--------------------------|------------|----------------|

| MII                    | 14-16     | 2 x 2.5 MHz              | Simple     | No             |

| RMII                   | 8         | 1 x 50 MHz               | High       | Yes            |

| SPI                    | 3-4       | 1 x 12.5 MHz             | Medium     | No             |

| Serial DME             | 2 or 4    | N/A                      | High       | Yes            |

| SPI-like<br>Variations | 3 - 5     | 1 x 10MHz or<br>1 x 5MHz | Medium     | No             |

## **Other Thoughts**

- All of the clocks suggested are below **30MHz** which should help with the fundamental radiating.

- With automotive **EMC**, possibility exists for significant radiation at harmonics of the clock, which might make board design more costly.

- Optionally, **FM** modulating the clock(s) could significantly reduce detected radiation from clock harmonics.

## **Management Interface**

- MII defined the data interface and the management interface.

- The management interface should be separate from the **MAC** interface.

- It could be **Clause 45 MDIO** which is a 2-pin interface or a management interface used in the industry.

## Conclusions

- DME, SPI, or an SPI-variant interface can help 10SPE achieve its cost and complexity objectives by reducing pin count substantially

- Each interface has its advantages and disadvantages

- SPI is already an industry standard and could be utilized with existing MAC interface equipment.

- **DME** eliminates the clock.

- An variant of **SPI** could allow stopping the clock for power savings.

- There exist feasible options for a low-pin-count low power media independent interface for **10SPE**

# Thank You!

IEEE 802.3 10SPE Study Group - September 2016 Interim