Hi Winston

There is a penalty to be paid with restricted bandwidth PAM4 no matter which approach is taken, and I believe this is one reason that our experimental results show that 100G/lambda PAM4 does not perform as well in practice compared to DMT as predicted by simplistic calculations, especially given the bandwidth of real components such as ADC and DAC and when clock jitter is taken into account.

If all the DSP is at the RX side (case 1), the vertical eye opening for high-frequency data (01010101) is reduced since only low-frequency data (00001111) fills the dynamic range of the ADC – in other words, the constellation spacing in this case is smaller relative to the TIA/ADC noise floor, and any equalisation then amplifies the noise as well as signal – a DFE does not amplify noise but has many issues with actual realisation at these data rates due to its recursive nature.

If all the equalisation is performed with DSP at the TX side then the peaking can be quite large (depending on component bandwidth) and this directly reduces the available transmit power into the fiber.

If Nyquist shaping is performed at the TX side then not only does this carry a hardware penalty (digital power for shaping) but the horizontal eye opening at the receiver is very small, which makes the system very sensitive to jitter (e.g. on reference clock, internal PLL).

This is made worse by the fact that with one sample per symbol (used in most/all PAM propositions to reduce power) the CDR phase estimation (Mueller-Muller or similar) is very noisy so a lot of averaging (low loop gain) is needed to reduce the jitter caused by this; the low tracking loop bandwidth makes the phase noise requirements on the clock path much harder to meet in practice without increasing power and/or cost (this is the case for all 1-sample-per-symbol PAM4 systems).

These are all non-negligible real-life degradations which reduce the performance or increase the power/cost of PAM4 compared to oversimplified analyses; if we want to get an “apples-to-apples” comparison with other proposals these cannot be ignored and must be included when estimating system margins.

As far as I am aware, the only PAM4 systems these issues do not apply to is ones where all the components have wide enough bandwidth that little or no equalisation is required, and I don’t think anyone is suggesting that this is achievable with low power and cost for 100G/lambda PAM4.

Cheers

Ian

IAN DEDIC

Chief Engineer

Fujitsu Semiconductor Europe GmbH

3 Concorde Park, Concorde Road

SL6 4FJ Maidenhead, Berkshire, United Kingdom

Phone: +44 (0) 1628 50 4711

Fax: +44 (0) 1628 50 4777

Mobile: +44 (0) 786 7829539

Mailto: ian.dedic@xxxxxxxxxxxxxx

Internet: http://emea.fujitsu.com/semiconductor

From: Winston Way [mailto:winston.way@xxxxxxxxxxxxxxxx]

Sent: 01 October 2014 01:08

To: IEEE_listserver

Subject: Re: [STDS-802-3-400G] IEEE P802.3bs 400 Gb/s Ethernet SMF Ad Hoc conference call draft agenda

Chris,

There are three approaches in IEEE802.3bs contributions regarding 100Gb/s PAM4:

1. No DSP at the TX side, all DSP is at RX side.

2a. DSP at the TX side, with a pre-equalization that is performing the inverse function of the original end-to-end response.

2b. DSP at the TX side, performing Nyquist shaping.

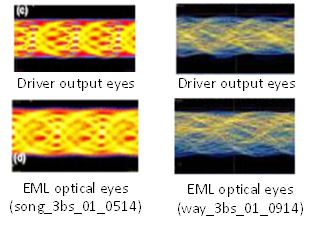

In case 1., there is no peaking due to the limited bandwidth of DAC, driver amp, or EML, as shown in the two experiments below:

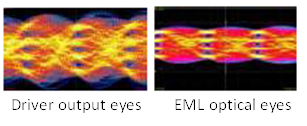

In case 2a, there is a peaking out of the driver amp, due to the suppression of low-frequency components, as you have quoted; but that peaking was smoothed out by the EML transfer function, as shown below:

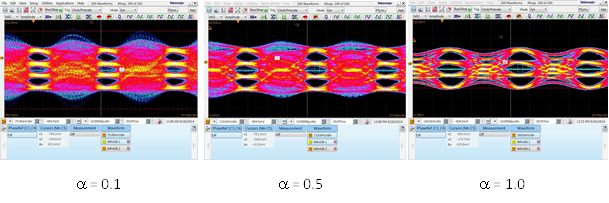

In case 2b, Nyquist shaping clearly generates significant peaking mainly at a small alpha factor (e.g., a ≤ 0.1), but not at a large alpha factor (e.g., a=1.0). See diagrams below. Note that the jitter tolerance due to a small alpha factor is very poor due to the much smaller eye width, as can be seen in the left-most diagram, and therefore may not provide the best performance even though it is more bandwidth efficient. Therefore, using a small alpha and a strong peaking as examples, as shown in your comparison analysis today, may not be quite appropriate.

So Nyquist shaping with a small alpha factor is just one of the multiple 100Gb/s PAM4 approaches, and should not be generalized to say that all PAM4 modulations will generate peaking. There are PAM4 approaches that do not generate peaking, and it is not true that “in all cases there is non-negligible peaking”.

Thanks,

Winston

From: Chris Cole [mailto:chris.cole@xxxxxxxxxxx]

Sent: Tuesday, September 30, 2014 9:17 AM

To: STDS-802-3-400G@xxxxxxxxxxxxxxxxx

Subject: Re: [STDS-802-3-400G] IEEE P802.3bs 400 Gb/s Ethernet SMF Ad Hoc conference call draft agenda

On today’s SMF Ad Hoc conference call, during presentation of “Optical Specifications of SMF PMDs Study” it was suggested that the only time there is peaking in a PAM-4 waveform is when using the “Nyquist PAM-4” approach.

Peaking is a function of TX bandwidth and pulse shaping. If TX is driven by a DAC, then pulse shaping is limited by the DAC sampling rate and analog bandwidth. In the case of the 100G/wavelength proposals in .bs, even for “Broadband PAM-4”, the DAC imposes a severe limitation on pulse shaping, and in all cases there is non-negligible peaking.

A clear example of peaking can be seen in “Single Wavelength over 112Gb/s PAM4 …” by Way and Chan, despite the obvious design preference to have none.

http://www.ieee802.org/3/bs/public/14_09/way_3bs_01a_0914.pdf#page=6 (see 3rd and 4th images)

This peaking is unavoidable because of the DAC and Driver limitations listed on the following pages.

A complete link budget has to account for reduction in TX OMA to manage the clipping level due to component limitations. It is not acceptable to ignore this penalty.

Chris

From: Anslow, Peter [mailto:panslow@xxxxxxxxx]

Sent: Tuesday, September 30, 2014 6:53 AM

To: STDS-802-3-400G@xxxxxxxxxxxxxxxxx

Subject: [STDS-802-3-400G] IEEE P802.3bs 400 Gb/s Ethernet SMF Ad Hoc conference call draft agenda

Hi,

As previously announced, there is an SMF Ad Hoc meeting starting at 7:30 am Pacific Today, Tuesday 30 September.

I have currently received two requests for presentations so the draft agenda is:

Attendees names and affiliations will be taken from the Webex participants list. If you attend via phone only, or if your employer and affiliation are different, please send me an e-mail.

Discussion

· IEEE patent policy reminder

o http://www.ieee802.org/3/patent.html

· Approval of the agenda

· Approval of the draft minutes from 19 August 2014 call

· Presentations

o Updated Considerations on 400Gb/s Ethernet SMF PMDs Peter Stassar, Huawei

o Optical Specifications of SMF PMDs Study Chris Cole, Finisar

Discussion

Peter Anslow from Ciena has invited you to join a meeting on the Web, using WebEx. Please join the meeting 5-10 minutes early so we may begin on time.

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

Topic: "P802.3bs SMF Ad Hoc"

Date & Time: Tuesday, 30 September 2014 at 15:30, GMT Summer Time (London, GMT+01:00)

To join web meeting click here: https://ciena.webex.com/ciena/j.php?MTID=m6572f354a7a856a704aec5ef0fb5e0e2

Meeting password: IEEE (please note passwords are case sensitive)

Teleconference: Provide your phone number when you join the meeting to receive a call back. Alternatively, you can call:

4438636577 (United States)

2064450056 (Canada)

4006920013 (China)

Show global numbers: https://www.tcconline.com/offSite/OffSiteController.jpf?cc=2070125535

Conference Code: 207 012 5535

Meeting number: 689 183 943

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

Additional Notes:

- To add this meeting to your calendar program click the following link, or copy the link and paste it into your Web browser: https://ciena.webex.com/ciena/j.php?MTID=m18ec485fd6625cb9308800f19f10c384

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

Pete Anslow | Senior Standards Advisor

43-51 Worship Street | London, EC2A 2DX, UK

Direct +44 2070 125535 |

This transmission is intended for the sole use of the individual and entity to whom it is addressed, and may contain information that is privileged, Neoconfidential and exempt from disclosure under applicable law. You are hereby notified that any dissemination, distribution or duplication of this transmission by someone other than the intended addressee or its designated agent is strictly prohibited. If your receipt of this transmission is in error, please notify the sender immediately by reply to this transmission and delete it from your computer. Thank You.

NeoPhotonics Corporation | 2911 Zanker Road | San Jose, CA 95134