## 400GbE Architecture Baseline Proposal

#### IEEE P802.3bs 400 Gb/s Ethernet Task Force

November 2014 San Antonio

Pete Anslow - Ciena

John D'Ambrosia – Dell

Mark Gustlin – Xilinx

Adam Healey – Avago

David Law – HP

Gary Nicholl - Cisco

Dave Ofelt – Juniper

Steve Trowbridge - ALU

## **Supporters**

**TBD**

### **Agenda**

➤ Proposed 400G architecture

### What Needs to be Supported in the Architecture?

- ➤ The coding needs of the electrical interface may vary independently from the PMD interface

- ➤ The requirements for each interface can be different, both the FEC, modulation and number of lanes can change over time for each interface

- ➤ We need a single high level architecture which can support the evolving requirements of the interfaces over time

- This does not mean it is requires a complicated implementation

### **Names & definitions**

#### > ... the naming of things

| Item               | Name Used Temporarily | Function/definition                                                                                                                                                                         |

|--------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

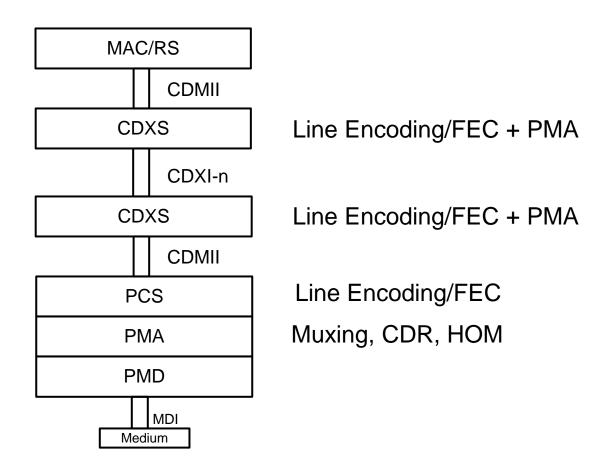

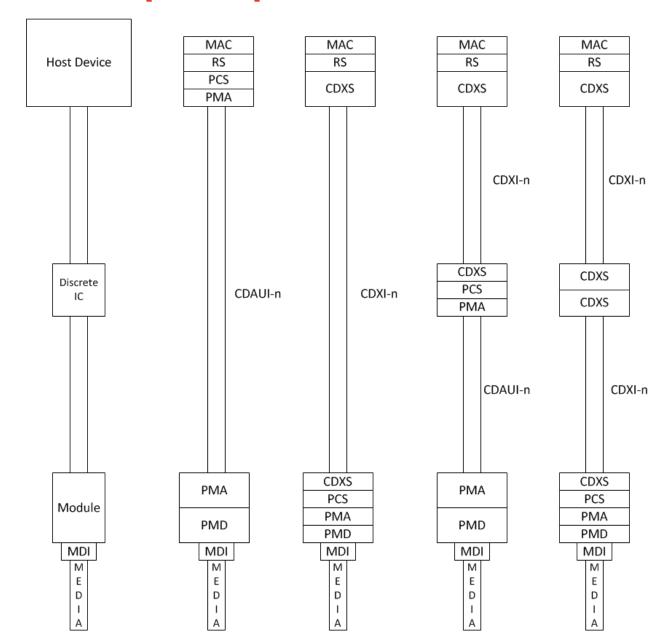

| Extender sublayer  | CDXS                  | Extends xMII (recovers raw 400G datastream) – used whenever a different coding or FEC is required further out in the PHY. Includes line code, FEC & timing required for extender interface. |

| Extender interface | CDXI-n                | Interface between two CDXS, may be various widths                                                                                                                                           |

| PMA interface      | CDAUI-n               | Physical instantiation of PMA service interface (similar to CAUI)                                                                                                                           |

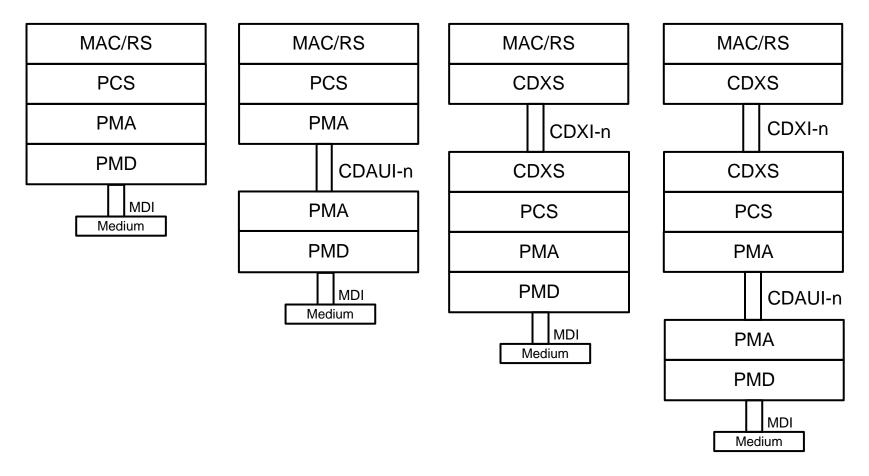

#### A Possible 400G Architecture

The PCS can be unique for each PMD!

Though we strive for commonalty where possible

### Sublayer Functions (at a high level)

| Sublayer | 10GbE                                            | 100GbE                                   | 400GbE (proposed)                      |

|----------|--------------------------------------------------|------------------------------------------|----------------------------------------|

| MAC      | Framing, addressing, error detection             | Framing, addressing, error detection     | Framing, addressing, error detection   |

| Extender | PCS + PMA                                        | N/A                                      | PCS + PMA + FEC                        |

| PCS      | Coding (8B/10B, 64B/66B), lane distribution, EEE | Coding (64B/66B), lane distribution, EEE | Coding, lane distribution, EEE, FEC    |

| FEC      | FEC, transcoding                                 | FEC, transcoding, align and deskew       | N/A?                                   |

| PMA      | Serialization, clock and data recovery           | Muxing, clock and data recovery, HOM     | Muxing, clock and data recovery, HOM?? |

| PMD      | Physical interface driver                        | Physical interface driver                | Physical interface driver              |

Note that there are variations with a single speed, not all are captured in this table

#### A Possible 400G Architecture

➤ The interface between the CDXS and the MAC or PCS sublayer is always a CDMII

### **400GbE Example Implementations**

# Thanks!