## Comment (#140, 412, #413, #414,#415, #416, #417):

- 1. TDL #275 and #276 D2.1 (comments: #108, #420, #421, #281 D2.2) was not fully implemented.

- 2. In addition, editor has noted that due to comment #452 D2.2 (removal of PPort\_PD) we can't use the term PPort\_PD. 33A.1 was written to address Type 1 PSE and PD. It is still relevant for Type 2 PSE. It was updated not to address Type 3 and Type 3 system therefore <u>it should be limited for clause 33 only</u>. As a result, Pport\_PD term can be use.

- 3. To move this material to clause 33 and file maintenance request.

### Proposed Remedy: Make the following changes:

## **PSE-PD** stability

#### 33A.1 Recommended PSE design guidelines and test setup

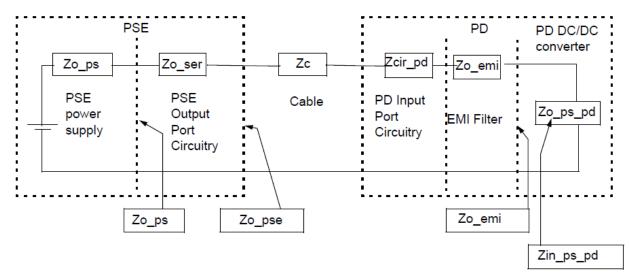

In order to prevent potential oscillations between the PSE and PD, the sum of the PSE port output impedance (Zo\_pse), the cable impedance (Zc), the PD input port circuitry impedance (Zcir\_pd) and the PD EMI output filter impedance (Z\_emi) should be lower than the PD power supply input impedance (Zin\_ps\_pd). All the above impedances are converted to the equivalent series impedance form as described by Figure 33A-1.

PSE PI output impedance consists of two parts:

- PSE power supply output impedance (Zo\_ps), which is a function of the load at the PSE PI, and

- the series elements (Z\_ser) that connect the PSE power supply output to the PSE PI.

Therefore, the PSE PI output impedance during normal powering mode is Zo\_pse=Zo\_ps+Z\_ser.

In order to maintain PSE-PD stability, the following guidelines apply:

-- Zo\_ps max = 0.3  $\Omega_{\tau}$  at frequencies up to 100 kHz at the highest output power level that the PSE supports, as defined in Table 33–1333-7 At lower power Ppse\_actual, Zout\_ps\_max =0.3 $\Omega$  x PClass / Ppse\_actual. Ppse\_actual is the actual power that the PSE support below PClass. Zo\_ps can be extracted from Zo\_port by measuring VPort\_PSE-2P-/ IPort (with an external power dynamic analyzer system) as a function of frequency and subtracting from Zo\_port the value of ZserZo\_ser which is limited by the value of Zo\_ser at DC (low frequency).

— If Zo\_ps < Zo\_ser and VPort 2P is kept to VPort 2P min and VPort 2P max as defined in Table 33– 17 during dynamic load changes from 10 Hz to 100 kHz, then the value of Zo\_ps is not limited.

— The value of Zo\_ps is not limited if the following conditions are met simultaneously:

- 1) Zo\_ps < Zo\_ser

- Vpse is kept in the range of VPort\_PSE-2P-as defined in Table 33-17 33-11 during dynamic load changes from 10 Hz to 100 kHz.

Verification of these guidelines can be made by measuring the PSE PI output impedance from 10 Hz to 100 kHz at the highest output power level that the PSE supports, as defined in Table 33-7 with the maximum load per the PSEs assigned Class, as defined in Table 33–13 at short cable length, or by performing simulations.

See Figure 33A-1 for the PSE-PD system impedance allocation.

#### 33A.2 Recommended PD design guidelines

PD PI input impedance consists of the following two parts:

- PD PI input circuits Zcir\_pd and the EMI filterZ\_emi\_Zo\_emi,

- PD power supply input impedanceZin\_ps\_pd.

In order to maintain stability with the PSE, the PD power supply input impedance Zin\_ps\_pd should be higher than the output impedance of the total network that precedes it (Zo\_emi+Zcir\_pd+Zc+Zo\_pse).

The worst-case scenario is when the channel length is zero (in terms of lower damping factor).

Access to the PD input power supply is not possible through the PD port for evaluating the various impedances in the PD and derivation of the above individual impedances. The following guidelines are recommended when measuring the PD input impedance:

— The PD power supply input impedance (Zin\_ps\_pd) at  $\frac{Pclass_PD}{PClass_PD}$  as defined in Table  $\frac{33}{30 \cdot 33 \cdot 18}$  should be higher than 30  $\Omega$  at any frequency up to the PD power supply crossover closed loop

frequency. If the PD power supply is consuming less than <u>PClass\_PD\_max</u>, -as defined in Table<del>33</del>-<del>30</del>33-18 i.e. Ppd\_actual, then Zin\_ps\_pd min = 30 x <u>Pport\_PD\_max\_PClass\_PD</u>-/Pport\_PD. <u>PPort\_PD is</u> the actual power consumed by the PD below PClass\_PD.

Comment D2.2/#452 removed PPort\_PD. Replacing the above by PClass\_PD would be incorrect. Solution needed.

— The PD power supply EMI filter output impedance should be Zo\_emi =  $2.7 \Omega$  max. If the PD power supply is consuming less than <u>PClass\_PD</u>, then Zo\_emi =  $2.7 \times \frac{PPort_PD - max_PClass_PD}{PPort_PD}$ .

See Figure 33A–1 for the PSE-PD system impedance allocation.

# End of Baseline