1 Comment (clause 33.3.3.12 #251 page 130 line 24)

5

6 7

8

9

10

1112

13 14

15

1617

18 19 20

2122

23

24

25

2627

28

2930

313233

34

3536

- 2 The following changes are required in the dual-signature PD variable list in clause

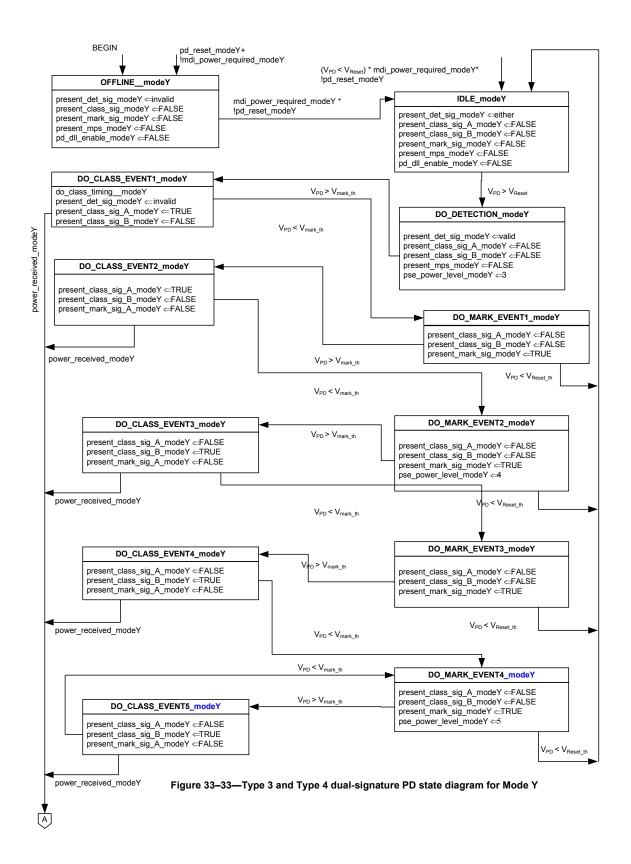

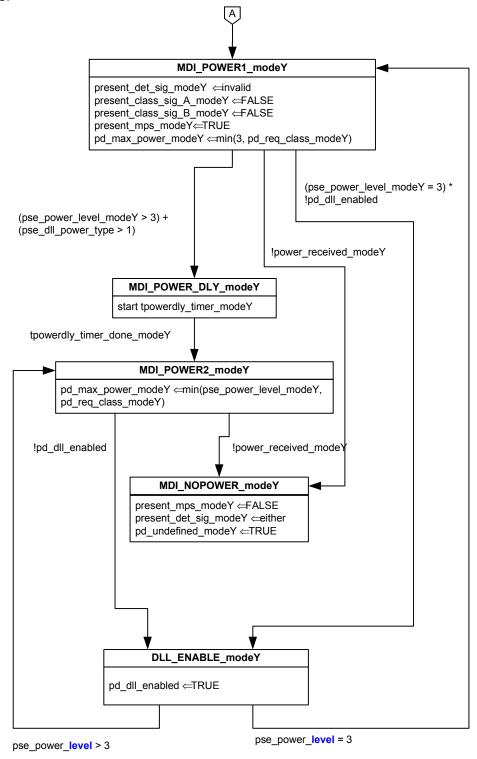

- 3 33.3.3.12 and in the dual-signature Type 3 and 4 PD state machines Figure 33-33 and Figure 33-34:

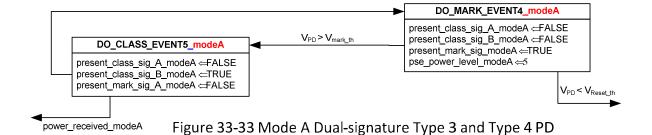

- 1. The exits from DLL\_ENABLE in Figure 33-33 page 136 and Figure-34 page 138 should be update according to the exits in Figure 33-32 page 129 with the prefix modeA and modeB.

- 2. There is no need for DLL\_ENABLE\_modeA/B due to the fact that if DLL is enabled, it is done for all powered pairs.

- 3. There is also no need for pd\_dll\_enable\_modeA and pd\_dll\_enable\_modeB due to the fact that if DLL is enabled, it is done for all powered pairs.

- 4. In figure 33-33, DO\_CLASS\_EVENT5 and DO\_MARK\_EVENT4 is missing the suffix " modeA.

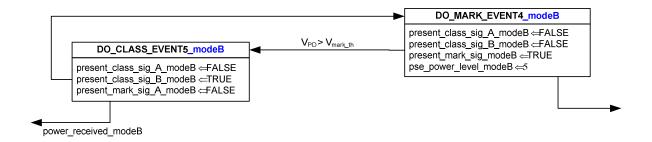

- 5. In figure 33-34, DO\_CLASS\_EVENT5 and DO\_MARK\_EVENT4 is missing the suffix " modeB.

- 6. To verify that all changes will be in sync with Figure 33-50.

## See "OPTION A" suggested remedy for reference in the next pages.

7. Consider to further simplifying the whole dual-signature state machine and its constant, variable, timers and functions starting at page 129 up to page 138 by doing the following actions:

All constants, variables, timers and functions that ends with the suffix \_modeA i.e. parameter\_name\_modeA (e.g. pd\_req\_class\_modeA) will be change to parameter nameY where the suffix "Y" will be "A" or "B".

- a) All constants, variables, timers and functions that ends with the suffix modeB will be deleted.

- b) Figure 33-33 will be updated with the new suffix "Y".

- c) Figure 33-34 will be deleted.

See "OPTION B" suggested remedy for reference in the next pages.

# Baseline starts at next page:

## Suggested Remedy -Option A

2 Make the following changes:

### 33.3.3.11 Type 3 and Type 4 dual-signature constants

3 4

1

#### This is not part of the base line

Work need to be done to verify that single signature and dual-signature state machine and their variable list are sync with DLL state machines Figure 33-49 and Figure 33-50.

5 6

Editor Note: DLL PSE and PD power control state diagram (Figure 33-49 and Figure 33-50) need to be evaluated and sync with the single signature and dual-signature PD state machine.

7 8 9

11

12

13

14

15

16 17

18

19

20

21

The PD state diagram uses the following constants:

10 VReset

Reset voltage per pairset (see Table 33–26)

VReset th

Reset voltage threshold per pairset (see Table 33–26)

VMark\_th

Mark event voltage threshold per pairset (see Table 33–26)

pd req class modeA

A constant indicating the requested Class of the PD over mode A.

Values:

- 1: The PD requests Class 1.

- 2: The PD requests Class 2.

- 3: The PD requests Class 3.

- 4: The PD requests Class 4.

- 5: The PD requests Class 5.

22 23 24 25 26 27 28 29 30 pd req class modeB

A constant indicating the requested Class of the PD over mode B.

Values:

- 1: The PD requests Class 1.

- 2: The PD requests Class 2.

- 3: The PD requests Class 3.

- 4: The PD requests Class 4.

- 5: The PD requests Class 5.

33 34

35

36

37

40

41

42

31

32

#### 33.3.3.12 Type 3 and Type 4 dual-signature variables

The PD state diagram uses the following variables:

38 mdi power required modeA 39

A control variable indicating that over mode A, the PD is enabled and should request power from the PSE by applying a PD detection signature to the link, and when the PSE sources power to apply the MPS to keep the PSE sourcing power. A variable that is set in an implementation-dependent manner. Values:

FALSE:PD functionality is disabled. TRUE:PD functionality is enabled.

mdi power required modeB

A control variable indicating that over mode B, the PD is enabled and should request power from the PSE by applying a PD detection signature to the link, and when the PSE sources power to apply the MPS to keep the PSE sourcing power. A variable that is set in an implementation-dependent manner. Values:

FALSE:PD functionality is disabled.

TRUE:PD functionality is enabled.

#### This is not part of the base line

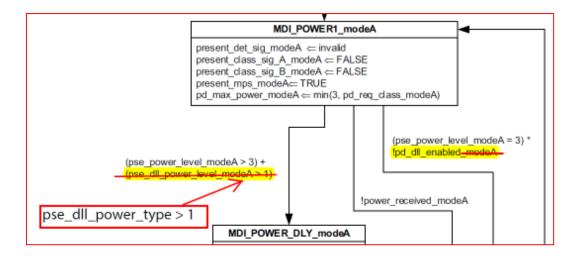

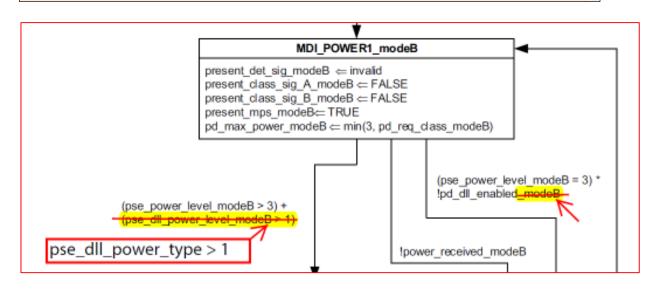

When dual-signature DLL is enabled, it is enabled for both pairset. As a result pd\_dll\_enabled variable is the same for both modeA and modeB.

14

15 16 17

18

19

32

33

34

35

36

37

38

39

40

41 42

43

44

45

46

47

48 49

50

51

52

pd dll enabled-modeA

A variable indicating whether the Data Link Layer classification mechanism is enabled over mode A. Values:

FALSE:Data Link Layer classification is not enabled. TRUE:Data Link Layer classification is enabled.

pd\_dll\_enabled\_modeB

— A variable indicating whether the Data Link Layer classification mechanism is enabled over mode B. Values:

FALSE: Data Link Layer classification is not enabled.

TRUE: Data Link Layer classification is enabled

pd max power modeA

A control variable indicating the max power that the PD may draw from the PSE over mode A. See power classifications in Table 33–28.

Values:

- 1: PD may draw Class 1 power

- 2: PD may draw Class 2 power

- 3: PD may draw Class 3 power

- 4: PD may draw Class 4 power

- 5: PD may draw Class 5 power

#### pd max power modeB

A control variable indicating the max power that the PD may draw from the PSE over mode B. See power classifications in Table 33–28.

Values:

- 1: PD may draw Class 1 power

- 2: PD may draw Class 2 power

- 3: PD may draw Class 3 power

- 4: PD may draw Class 4 power

- 5: PD may draw Class 5 power

pd\_reset\_modeA

An implementation-specific control variable that unconditionally resets the PD state diagram over mode A to the OFFLINE modeA state.

Values:

FALSE: The device has not been reset (default).

TRUE: The device has been reset.

pd\_reset\_modeB

An implementation-specific control variable that unconditionally resets the PD state diagram over mode B to the OFFLINE\_modeB state.

Values:

FALSE: The device has not been reset (default).

TRUE: The device has been reset.

pd undefined modeA

A control variable that indicates that the PD is in an undefined condition over mode A. The PD may or may not show a valid or invalid detection signature, may or may not draw mark current, may or may not draw any class current, may or may not show MPS and may change the pse\_power\_level\_modeA variable.

Values:

FALSE: The PD is in a defined condition (default).

TRUE: The PD is an undefined condition.

pd undefined modeB

A control variable that indicates that the PD is in an undefined condition over mode B. The PD may or may not show a valid or invalid detection signature, may or may not draw mark current, may or may not draw any class current, may or may not show MPS and may change the pse\_power\_level\_modeB variable.

Values:

FALSE: The PD is in a defined condition (default).

TRUE: The PD is an undefined condition.

power received modeA

An indication from the circuitry that power is present on the PD's PI over mode A.

Values:

FALSE: The input voltage does not meet the requirements of VPort PD in Table 33–28.

TRUE: The input voltage meets the requirements of VPort PD.

power\_received\_modeB

An indication from the circuitry that power is present on the PD's PI over mode B.

Values:

FALSE: The input voltage does not meet the requirements of VPort\_PD in Table 33–28.

TRUE: The input voltage meets the requirements of VPort\_PD.

present\_class\_sig\_A\_modeA

Controls presenting the classification signature that is used during first two class events (see 33.3.5) by the PD over mode A.

Values:

FALSE: The PD classification signature is not to be applied to the link.

TRUE: The PD classification signature is to be applied to the link.

present class sig A modeB

Controls presenting the classification signature that is used during first two class events (see 33.3.5) by the PD over mode B.

Values:

FALSE: The PD classification signature is not to be applied to the link.

TRUE: The PD classification signature is to be applied to the link.

present\_class\_sig\_B\_modeA

Controls presenting the classification signature that is used during the third class event and all subsequent class events over mode A (see 33.3.5) by the PD.

Values:

56

FALSE: The PD classification signature is not to be applied to the link.

TRUE: The PD classification signature is to be applied to the link.

```

1 2 3 4 5 6 7 8 9

present_class_sig_B_modeB

Controls presenting the classification signature that is used during the third class event and all subsequent class events

over mode B (see 33.3.5) by the PD.

Values:

FALSE: The PD classification signature is not to be applied to the link.

TRUE: The PD classification signature is to be applied to the link.

10

present det sig modeA

11

Controls presenting the detection signature (see 33.3.4) by the PD over mode A.

12

Values:

13

invalid: A non-valid PD detection signature is to be applied to the link over mode A regardless of any

14

voltage above Vreset applied to mode B.

15

16

valid: A valid PD detection signature is to be applied to the link over mode A regardless of any voltage

17

above Vreset applied to mode B.

18

either: Either a valid or non-valid PD detection signature may be applied to the link.

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

40

41

42

43

44

present det sig modeB

Controls presenting the detection signature (see 33.3.4) by the PD over mode B.

Values:

invalid: A non-valid PD detection signature is to be applied to the link over mode B regardless of any

voltage above Vreset applied to mode B.

valid: A valid PD detection signature is to be applied to the link over mode B regardless of any voltage

above Vreset applied to mode B.

either: Either a valid or non-valid PD detection signature may be applied to the link.

present mark sig modeA

Controls presenting the mark event current and impedance (see 33.3.5.2.1) by the PD over mode A.

Values:

FALSE: The PD does not present mark event behavior.

TRUE: The PD does present mark event behavior.

present mark sig modeB

Controls presenting the mark event current and impedance (see 33.3.5.2.1) by the PD over mode B.

Values:

FALSE: The PD does not present mark event behavior.

TRUE: The PD does present mark event behavior.

present mps modeA

Controls applying MPS over mode A (see 33.3.7.10) to the PD's PI.

45

FALSE: The Maintain Power Signature (MPS) is not to be applied to the PD's PI.

46

TRUE: The MPS is to be applied to the PD's PI.

47

48

present mps modeB

49

50

51

52

53

Controls applying MPS over mode B (see 33.3.7.10) to the PD's PI.

Values:

FALSE. The Maintain Power Signature (MPS) is not to be applied to the PD's PI.

TRUE: The MPS is to be applied to the PD's PI.

54

pse dll power level modeA

55

A control variable output by the PD power control state diagram (Figure 33–50) that indicates the power level of the

```

PSE by which the PD is being powered over mode A.

17

18 19

20

21

22

36

37

42

43

44

45

46

- 1: The PSE has allocated Class 3 power or less (default).

- 2: The PSE has allocated Class 4 power.

- 3: The PSE has allocated Class 5

pse dll power level modeB

A control variable output by the PD power control state diagram (Figure 33-50) that indicates the power level of the PSE by which the PD is being powered over mode B.

- 1: The PSE has allocated Class 3 power or less (default).

- 2: The PSE has allocated Class 4 power.

- 3: The PSE has allocated Class 5

#### This is not part of the base line

pse dll power type was missing from the variable list and it is used in the state machine. In addition, For dualsignature PD it is not possible that different pse\_dll\_power\_type values for the same PSE port will be indicated by the PD as for the PSE type it is connected to. As a result pse\_dll\_powerType\_modeA and pse\_dll\_powerType\_modeB should be merged to pse\_dll\_powerType only.

pse dll power type

A control variable output by the PD power control state diagram (Figure 33-50) that indicates the PSE type connected as 1 or 2, see 79.3.2.4.1.

The PSE type will be set according to the pairset with the highest power capability. Vlaues:

1: The PSE is a Type 1 PSE, for a Type-1 PSE.

2: The PSE is a Type 2 PSE, for a Type 2, 3 and, 4 PSE.

pse power level modeA

A control variable that indicates to the PD over mode A the level of power the PSE is supplying. Values:

- 3: The PSE has allocated the PD's requested power or Class 3 power, whichever is less.

- 4: The PSE has allocated the PD's requested power or Class 4 power, whichever is less.

- 5: The PSE has allocated the PD's requested power or Class 5 power, whichever is less.

pse power level modeB

A control variable that indicates to the PD over mode B the level of power the PSE is supplying. Values:

- 3: The PSE has allocated the PD's requested power or Class 3 power, whichever is less.

- 4: The PSE has allocated the PD's requested power or Class 4 power, whichever is less.

- 5: The PSE has allocated the PD's requested power or Class 5 power, whichever is less.

**Editor Note:**

The variables:

- a) pse\_power\_type\_modeA

- b) pse power type modeB

should be generated by PD Type 3 and Type 4 dual-signature state machine (as pse power type is also needed to be generated by Type 3 and Type 4 signle-signature PD state machine) in order to

be used later by Figure 33-50 which is the DLL state machine and as a result need to be added also 1 2 to 33.6.3.3 variable list. 3 4 5 6 7 8 9 They are not required for Type 3 and 4 single or dual-signature PD state machine. VPD modeA Voltage at the PD PI as defined in 1.4.425 over mode A. VPD modeB Voltage at the PD PI as defined in 1.4.425 over mode B. 10 11 33.3.3.13 Type 3 and Type 4 dual-signature timers 12 All timers operate in the manner described in 14.2.3.2 with the following addition. A timer is reset and stops counting 13 upon entering a state where "stop x timer" is asserted. 14 tpowerdly\_timer\_modeA 15 A timer used to prevent class 4 Type 3 dual-signature PDs from drawing more than Type 1 power over mode A and 16 class 5 Type 4 dual-signature PDs from drawing more than Class 2 power over mode A during the PSE's inrush 17 period; see Tdelay-2P in Table 33-28. 18 19 tpowerdly timer modeB 20 A timer used to prevent class 4 Type 3 dual-signature PDs from drawing more than Type 1 power over mode B and 21 class 5 Type 4 dual-signature PDs from drawing more than Class 2 power over mode B during the PSE's inrush 22 period; see Tdelay-2P in Table 33-28. 23 24 33.3.3.14 Type 3 and Type 4 dual-signature functions 25 26 27 28 29 30 31 32 33 34 35 36 37 38 This function is used by a Type 3 or Type 4 PD to evaluate the Type of PSE connected to the link by measuring the length of the class event over mode A. The class event timing requirements are defined in Table 33–26. This function returns the following variable: short mps: A control variable that indicates to the PD the Type of PSE to which it is connected. This variable is used to indicate which MPS timing requirements (see 33.3.8) the PD should use. Values: TRUE: The PSE uses Type 3, 4 MPS requirements. FALSE: The PSE uses Type 1, 2 MPS requirements. do class timing modeB This function is used by a Type 3 or Type 4 PD to evaluate the Type of PSE connected to the link by measuring the length of the class event over mode B. The class event timing requirements are defined in Table 33–26. This function 39 returns the following variable: 40 short\_mps: A control variable that indicates to the PD the Type of PSE to which it is connected. This variable 41 is used to indicate which MPS timing requirements (see 33.3.8) the PD should use. Values: 42 TRUE: The PSE uses Type 3, 4 MPS requirements. 43 FALSE: The PSE uses Type 1, 2 MPS requirements. 44 45 46

Make the following changes on page 135 on Figure 33–33—Type 3 and Type 4 dual-signature PD state diagram for Mode A.

Make the following changes on Page 136 on Figure 33–33—Type 3 and Type 4 dual-signature PD state diagram for Mode A (continued).

Change the exits from DLL\_ENABLE in Figure 33-33 page 136 and Figure-34 page 138 should to match with the exits in Figure 33-32 page 129 with the prefix **\_modeA** per the approved remedy for comments on this subject.

Make the following changes on page 137 in Figure 33–34—Type 3 and Type 4 dual-signature PD state diagram for Mode A.

Make the following changes in:

Figure 33-34—Type 3 and Type 4 dual-signature PD state diagram for Mode B (continued), Page 138

Change the exits from DLL\_ENABLE in Figure 33-33 page 136 and Figure-34 page 138 should to match with the exits in Figure 33-32 page 129 with the prefix **\_modeB** per the approved remedy for comments on this subject.

### Suggested Remedy -Option B

- 2 Make the following changes:

- 3 The following are the requirements for dual-signature PD state machine over each modeA and

- 4 modeB. The dual-signature state machine shall be implemented over each pairset for mode A

- 5 and mode B independently unless otherwise specified. All the parameters that applies to mode A

- 6 and mode B are denoted with the suffix "\_modeY" where "Y" can be "A" or "B". A parameter that

- 7 ends with the suffix "modeY" may have different values for mode A and mode B.

### 33.3.3.11 Type 3 and Type 4 dual-signature constants

8 9

1

#### This is not part of the base line

Work need to be done to verify that single signature and dual-signature state machine and their variable list are sync with DLL state machines Figure 33-49 and Figure 33-50.

10 11

Editor Note: DLL PSE and PD power control state diagram (Figure 33-49 and Figure 33-50) need to be evaluate and sync with the single signature and dual-signature PD state machine.

12 13 14

16

17

18

19

```

The PD state diagram uses the following constants:

```

15 VReset

Reset voltage per pairset (see Table 33–26)

VReset th

Reset voltage threshold per pairset (see Table 33–26)

$V_{Mark\_th}$

Mark event voltage threshold per pairset (see Table 33–26)

pd\_req\_class\_<del>modeA</del> <u>modeY</u>

A constant indicating the requested Class of the PD over mode Y<del>mode A</del>.

Values:

- 1: The PD requests Class 1.

- 2: The PD requests Class 2.

- 3: The PD requests Class 3.

- 4: The PD requests Class 4.

- 5: The PD requests Class 5.

pd\_req\_class\_modeB

A constant indicating the requested Class of the PD over mode B.

Values:

- 1: The PD requests Class 1.

- 2: The PD requests Class 2.

- 3: The PD requests Class 3.

- 4: The PD requests Class 4.

- 5: The PD requests Class 5.

#### 1 33.3.3.12 Type 3 and Type 4 dual-signature variables 2 The PD state diagram uses the following variables: 3 4 5 mdi power required modeYmodeA 6 7 8 9 A control variable indicating that over mode Y mode A, the PD is enabled and should request power from the PSE by applying a PD detection signature to the link, and when the PSE sources power to apply the MPS to keep the PSE sourcing power. A variable that is set in an implementation-dependent manner. Values: 10 FALSE:PD functionality is disabled. 11 TRUE:PD functionality is enabled. 12 13 mdi power required modeB 14 A control variable indicating that over mode B, the PD is enabled and should request power from the PSE by 15 applying a PD detection signature to the link, and when the PSE sources power to apply the MPS to keep the 16 PSE sourcing power. A variable that is set in an implementation dependent manner. Values: 17 FALSE:PD functionality is disabled. 18 TRUE:PD functionality is enabled. 19 This is not part of the base line When dual-signature DLL is enabled, it is enabled for both pairset. As a result pd\_dll\_enabled variable is the same for both modeA and modeB. 20 21 22 23 24 25 26 27 28 29 30 pd dll enabled-modeA A variable indicating whether the Data Link Layer classification mechanism is enabled over mode A. Values: FALSE:Data Link Layer classification is not enabled. TRUE:Data Link Layer classification is enabled. pd dll enabled modeB A variable indicating whether the Data Link Layer classification mechanism is enabled over mode A. Values: FALSE: Data Link Layer classification is not enabled. 31 TRUE: Data Link Layer classification is enabled. 32 33 pd max power modeYmodeA 34 A control variable indicating the max power that the PD may draw from the PSE over mode Y<del>mode A</del>. See power 35 classifications in Table 33-28. 36 Values: 37 1: PD may draw Class 1 power 38 2: PD may draw Class 2 power 39 3: PD may draw Class 3 power 40 4: PD may draw Class 4 power 41 5: PD may draw Class 5 power 42 43 pd\_max\_power\_modeB 44 A control variable indicating the max power that the PD may draw from the PSE over modeB. See power 45 classifications in Table 33 28. 46 Values: 47 1: PD may draw Class 1 power 2: PD may draw Class 2 power 48 3: PD may draw Class 3 power 49

4: PD may draw Class 4 power

```

1

present class sig A modeY modeA

23456789

Controls presenting the classification signature that is used during first two class events (see 33.3.5) by the PD over

mode Ymode A.

Values:

FALSE: The PD classification signature is not to be applied to the link.

TRUE: The PD classification signature is to be applied to the link.

present_class_sig_A_modeB

10

Controls presenting the classification signature that is used during first two class events (see 33.3.5) by the PD over

11

mode B.

12

Values:

13

FALSE: The PD classification signature is not to be applied to the link.

14

TRUE: The PD classification signature is to be applied to the link.

15

16

present_class_sig_B_modeYmodeA

17

Controls presenting the classification signature that is used during the third class event and all subsequent class events

18

over mode A-Y (see 33.3.5) by the PD.

19

Values:

20

FALSE: The PD classification signature is not to be applied to the link.

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

TRUE: The PD classification signature is to be applied to the link.

present class sig B modeB

Controls presenting the classification signature that is used during the third class event and all subsequent class events

over mode B (see 33.3.5) by the PD.

Values:

FALSE: The PD classification signature is not to be applied to the link.

TRUE: The PD classification signature is to be applied to the link.

present det sig modeYmodeA

Controls presenting the detection signature (see 33.3.4) by the PD over mode \underline{AY}.

Values:

invalid: A non-valid PD detection signature is to be applied to the link over mode A regardless of any

voltage above Vreset applied to mode B.

valid: A valid PD detection signature is to be applied to the link over mode A regardless of any voltage

above Vreset applied to mode B.

either: Either a valid or non-valid PD detection signature may be applied to the link.

40

present det sig modeB

41

Controls presenting the detection signature (see 33.3.4) by the PD over mode B.

42

Values:

43

44

invalid: A non-valid PD detection signature is to be applied to the link over mode B regardless of any

voltage above Vreset applied to mode B.

45

46

-valid: A valid PD detection signature is to be applied to the link over mode B regardless of any voltage

47

above Vreset applied to mode B.

48

either: Either a valid or non-valid PD detection signature may be applied to the link.

49

50

51

present_mark_sig_modeA_modeY

Controls presenting the mark event current and impedance (see 33.3.5.2.1) by the PD over mode AY.

52

53

Values:

FALSE: The PD does not present mark event behavior.

54

TRUE: The PD does present mark event behavior.

```

```

1

present mark sig modeB

23456789

Controls presenting the mark event current and impedance (see 33.3.5.2.1) by the PD over mode B.

Values:

FALSE: The PD does not present mark event behavior.

TRUE: The PD does present mark event behavior.

present_mps_modeAmodeY

Controls applying MPS over mode \frac{A}{Y} (see 33.3.7.10) to the PD's PI.

Values:

10

FALSE: The Maintain Power Signature (MPS) is not to be applied to the PD's PI.

11

TRUE: The MPS is to be applied to the PD's PI.

12

13

present mps modeB

14

Controls applying MPS over mode B (see 33.3.7.10) to the PD's PI.

15

Values:

16

FALSE: The Maintain Power Signature (MPS) is not to be applied to the PD's PI.

17

TRUE: The MPS is to be applied to the PD's PI.

18

19

20

pse dll power level modeA modeY

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

A control variable output by the PD power control state diagram (Figure 33-50) that indicates the power level of the

PSE by which the PD is being powered over mode \frac{AY}{A}.

Values:

1: The PSE has allocated Class 3 power or less (default).

2: The PSE has allocated Class 4 power.

3: The PSE has allocated Class 5

pse dll power level modeB

A control variable output by the PD power control state diagram (Figure 33-50) that indicates the power level of the

PSE by which the PD is being powered over mode B.

Values:

1: The PSE has allocated Class 3 power or less (default).

2: The PSE has allocated Class 4 power.

3: The PSE has allocated Class 5

This is not part of the base line

For dual-signature PD it is not possible that different pse dll power type values for the same PSE port will be

indicated by the PD as for the PSE type it is connected to. As a result pse_dll_powerType_modeA and

pse_dll_powerType_modeB should be merged to pse_dll_powerType only.

36

37

pse dll power type

38

A control variable output by the PD power control state diagram (Figure 33-50) that

39

indicates the PSE type connected to mode Y as 1 or 2, see 79.3.2.4.1.

40

Values:

41

1: The PSE is a Type 1 PSE, for a Type-1 PSE.

42

2: The PSE is a Type 2 PSE, for a Type 2, 3 and, 4 PSE.

43

44

45

46

47

```

pse\_power\_level\_modeAmodeY 1 2 3 4 5 6 7 8 9 A control variable that indicates to the PD over mode <u>A-Y</u> the level of power the PSE is supplying. Values: 3: The PSE has allocated the PD's requested power or Class 3 power, whichever is less. 4: The PSE has allocated the PD's requested power or Class 4 power, whichever is less. 5: The PSE has allocated the PD's requested power or Class 5 power, whichever is less. se\_power\_level\_modeB A control variable that indicates to the PD over mode B the level of power the PSE is supplying. 10 Values: 11 12 13 3: The PSE has allocated the PD's requested power or Class 3 power, whichever is less. 4: The PSE has allocated the PD's requested power or Class 4 power, whichever is less. 5: The PSE has allocated the PD's requested power or Class 5 power, whichever is less. 14 15 **Editor Note:** 16 The variables: 17 a) pse power type modeA 18 b) pse power type modeB 19 should be generated by PD Type 3 and Type 4 dual-signature state machine (as pse power type is also needed to be generated by Type 3 and Type 4 signle-signature PD state machine) in order to 20 21 be used later by Figure 33-50 which is the DLL state machine and as a result need to be added also 22 to 33.6.3.3 variable list. 23 They are not required for Type 3 and 4 single or dual-signature PD state machine. 24 25 26 27 28 29 VPD modeAmodeY Voltage at the PD PI as defined in 1.4.425 over mode  $\underline{AY}$ . VPD modeB 30 Voltage at the PD PI as defined in 1.4.425 over mode B. 31 32 33.3.3.13 Type 3 and Type 4 dual-signature timers 33 All timers operate in the manner described in 14.2.3.2 with the following addition. A timer is reset and stops counting 34 upon entering a state where "stop x timer" is asserted. 35 tpowerdly timer modeAmodeY 36 37 38 39 40 A timer used to prevent class 4 Type 3 dual-signature PDs from drawing more than Type 1 power over mode A-Y and class 5 Type 4 dual-signature PDs from drawing more than Class 2 power over mode A-Y during the PSE's inrush period; see Tdelay-2P in Table 33-28. tpowerdly\_timer\_modeB 41 A timer used to prevent class 4 Type 3 dual signature PDs from drawing more than Type 1 power over mode B and 42 class 5 Type 4 dual signature PDs from drawing more than Class 2 power over mode B during the PSE's inrush 43 period; see Tdelay-2P in Table 33 28. 44 45 46 47

#### 23 45 67 89 do class timing modeAmodeY This function is used by a Type 3 or Type 4 PD to evaluate the Type of PSE connected to the link by measuring the length of the class event over mode AY. The class event timing requirements are defined in Table 33–26. This function returns the following variable: short mps: A control variable that indicates to the PD the Type of PSE to which it is connected. This variable is used to indicate which MPS timing requirements (see 33.3.8) the PD should use. Values: TRUE: The PSE uses Type 3, 4 MPS requirements. FALSE: The PSE uses Type 1, 2 MPS requirements. 10 11 do class timing modeB 12 This function is used by a Type 3 or Type 4 PD to evaluate the Type of PSE connected to the link by measuring the 13 length of the class event over mode B. The class event timing requirements are defined in Table 33 26. This function 14 returns the following variable: 15 short mps: A control variable that indicates to the PD the Type of PSE to which it is connected. This variable is used to indicate which MPS timing requirements (see 33.3.8) the PD should use. Values: 16 17 TRUE: The PSE uses Type 3, 4 MPS requirements. 18 FALSE: The PSE uses Type 1, 2 MPS requirements. 19 20 Make the following changes in Figure 33-33: 21 22 1. Change the title of figure 33-33 on page 135 as follows: 23 "Figure 33–33—Type 3 and Type 4 dual-signature PD state diagram for mode X mode Y" 24 25 2. Change the title of figure 33-33 on page 136 as follows: "Figure 33–33—Type 3 and Type 4 dual-signature PD state diagram for mode X mode Y (continued)" 26 27 28 3. Make the following changes in Figure 33-33 on page 135. 29 30 DO CLASS EVENT5 and DO MARK EVENT4 is missing the suffix "modey". 31 32 33 4. Make the following changes in Figure 33-33 on both pages 135 and 136: 34 35 Replace all parameters with the suffix "modeA" with "modeX modeY" 36 37 5. Make the following changes in Figure 33-33 on page 136: 38 39 -Replace "pse dll power level modeA" with "pse dll power type modeXmodeY. -Replace "!pd dll enabled modeA" with "!pd\_dll\_enabled". 40 -Replace "pse dll power level modeA" with "pse dll power type. 41 -Replace "pse\_power\_level\_modeA > 3" with "pse\_power\_type > 3" 42 -Replace "pse power level modeA = 3" with "pse power type = 3" 43 44 45 6. Make the following changes in Figure 33-34 on page 137 and 138: 46 Delete Figure 33-34 on pages 137 and 138. 47 48

1

33.3.3.x4 Type 3 and Type 4 dual-signature functions

7. The revised Figure 33-33 is attached below (two pages)

Figure 33–33—Type 3 and Type 4 dual-signature PD state diagram for Mode Y *(continued)*

# Base Line ends here

## **Revision History**

| # | Revision | Draft | Changes made                                                                   |

|---|----------|-------|--------------------------------------------------------------------------------|

| 1 | 002      | 1.8   |                                                                                |

| 2 | 003      | 2.0   | 1. Deleting unused variables.                                                  |

|   |          |       | 2. Deleting suffix "modeA' from pd_dll_enabled and delete pd_dll_enabled_modeB |

|   |          |       | 3. pse_dll_power_type was added.                                               |

|   |          |       | 4. Figures 33-33 and 33-34 where updated accordingly.                          |

| 3 | 004      |       | Optional solution to further simplifying dual-signature state                  |

|   |          |       | machine was added (Option B). Suffix "X" was changed to "Y"                    |

|   |          |       | since "X" is used in other places.                                             |