## 33.2.8.5.1 PSE pair-to-pair current unbalance

This section describes unbalance requirements for Type 3 and Type 4 PSEs that operate over 4-pair. The PSE PI pair-to-pair effective resistance unbalance contributes to the effective system end-to-end resistance unbalance as specified in Annex 33B.

A compliant unbalanced load,  $R_{load\_min}$  and  $R_{load\_max}$ , consists of the channel (cables and connectors) and PD effective resistances, including the effects (or influence) of system end-to-end unbalance.

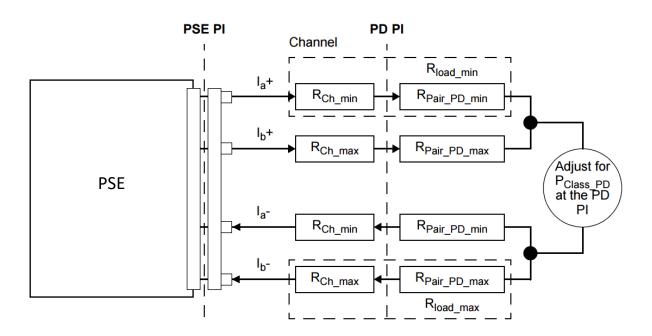

Figure 33–X shows a test circuit for the current unbalance requirements measurement, illustrating the relationship between current unbalance at the PSE PI ( $I_a$ +,  $I_b$ +,  $I_a$ -,  $I_b$ -), and  $R_{load\_min}$  and  $R_{load\_max}$  as specified in Table 33–X.

Current unbalance requirements ( $I_{Con-2P-unb}$ ) of a PSE shall be met with  $R_{load\_max}$  and  $R_{load\_min}$  as specified by Table 33–X.

Figure 33-X-PSE unbalance evaluation model

Table 33–  $X-R_{load\_max}$  and  $R_{load\_min}$  requirements

| PSE<br>Class | $R_{	ext{Ch\_min}} \ (\Omega)$ | $R_{Ch\_max} \ (\Omega)$ | $R_{Pair\_PD\_min} \ (\Omega)$ | $R_{Pair\_PD\_max} \ (\Omega)$ | $R_{load\_min} \ (\Omega)$ | $R_{load\_max} \ (\Omega)$ | Additional information                                     |

|--------------|--------------------------------|--------------------------|--------------------------------|--------------------------------|----------------------------|----------------------------|------------------------------------------------------------|

| 5            | 0.087                          | 0.1                      | 0.636                          | 1.528                          | 0.723                      | 1.628                      | R <sub>load</sub> is at low channel resistance conditions  |

| 6            | 0.087                          | 0.1                      | 0.536                          | 1.189                          | 0.623                      | 1.289                      |                                                            |

| 7            | 0.087                          | 0.1                      | 0.503                          | 0.990                          | 0.590                      | 1.090                      |                                                            |

| 8            | 0.087                          | 0.1                      | 0.457                          | 0.875                          | 0.544                      | 0.975                      |                                                            |

| 5            | TBD                            | TBD                      | TBD                            | TBD                            | 5.920                      | 7.190                      | R <sub>load</sub> is at high channel resistance conditions |

| 6            | TBD                            | TBD                      | TBD                            | TBD                            | 5.780                      | 7.000                      |                                                            |

| 7            | TBD                            | TBD                      | TBD                            | TBD                            | 5.710                      | 6.870                      |                                                            |

| 8            | TBD                            | TBD                      | TBD                            | TBD                            | 5.650                      | 6.790                      |                                                            |

The current unbalance test method is described below:

- 1) Use  $R_{load\_min}$  and  $R_{load\_max}$  from Table 33–X for  $R_{load}$  at low channel resistance conditions.

- 2) With the PSE powered on, adjust the load to P<sub>Class PD</sub> at the PD PI.

- 3) Measure  $I_a+$ ,  $I_b+$ .

- 4) Swap  $R_{load\_max}$ ,  $R_{load\_min}$ , repeat steps 2 and 3.

- 5) Repeat steps 2 to 4 for  $I_a$ -,  $I_b$ -.

- 6) Verify that the current in each case does not exceed  $I_{Con-2P-unb}$  minimum in Table 33–18.

- 7) Repeat steps 2 to 6 for  $R_{load\_min}$  and  $R_{load\_max}$  from Table 33–X for  $R_{load}$  at high channel resistance conditions.

## **Annex 33B**

(informative)

# PSE PI pair-to-pair resistance/current unbalance

#### 33B.1 Introduction

End to end pair-to-pair resistance/current unbalance (E2EP2PRunb) refers to current differences in powered pairs of the same polarity. Current unbalance can occur in positive and negative powered pairs when a PSE uses all four pairs to deliver power to a PD.

Lower  $R_{PSE\_max}$  than required by Equation (33B–1) is obtained by using smaller constant  $\alpha$  and larger constant  $\beta$  in the equation  $R_{PSE\_max} = \alpha \times R_{PSE\_min} + \beta$ .

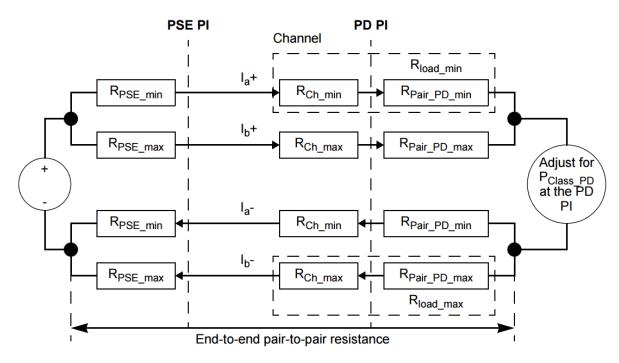

Equation (33B–1), specified for the PSE, assures that E2EP2PRunb will be met in the presence of all compliant unbalanced loads ( $R_{load\_min}$  and  $R_{load\_max}$ ) attached to the PSE PI.

The PSE PI pair-to-pair effective resistance unbalance determined by  $R_{PSE\_max}$  and  $R_{PSE\_min}$  ensures that along with any other parts of the system, i.e. channel (cables and connectors) and the PD, the maximum pair current including unbalance does not exceed  $I_{Con-2P-unb}$  as defined in Table 33–18 during normal operating conditions.  $I_{Con-2P-unb}$  is the current in the pairset with the highest current in case of maximum unbalance and will be higher than  $I_{Con}/2$ .

R<sub>PSE\_max</sub> and R<sub>PSE\_min</sub> are specified and measured under maximum P<sub>Class</sub> sourcing conditions. The following design guidelines may be implemented to ensure PSE PI pair-to-pair current unbalance requirements are met:

$$R_{PSE\_max} = \begin{cases} 2.200 \text{ x } R_{PSE\_min} - 0.040 & \text{ for Class 5} \\ 2.010 \text{ x } R_{PSE\_min} - 0.040 & \text{ for Class 6} \\ 1.800 \text{ x } R_{PSE\_min} - 0.030 & \text{ for Class 7} \\ 1.750 \text{ x } R_{PSE\_min} - 0.030 & \text{ for Class 8} \end{cases}_{\Omega} \tag{33B-1}$$

where

R<sub>PSE\_max</sub> is, given R<sub>PSE\_min</sub>, the highest allowable common mode effective resistance in

the powered pairs of the same polarity

R<sub>PSE min</sub> is the lower PSE common mode effective resistance in the powered pairs of the

same polarity

The values of  $R_{PSE\_max}$  and  $R_{PSE\_min}$  are implementation specific and need to satisfy Equation (33B–1). A PSE which uses current balancing methods which effectively using lower  $R_{PSE\_max}$  than required by Equation (33B–1) and meets  $I_{Con-2P-unb}$  requirements by definition also meets Equation (33B–1). See 33.2.8.5.1 for PSE unbalance requirements and PSE unbalance measurement method.

Figure 33B-1 illustrates the relationship between effective resistances at the PSE PI as specified by Equation (33B-1) and end-to-end pair-to-pair resistance.

Figure 33B-1-PSE PI unbalance specification

## 33B.2 Direct R<sub>PSE</sub> measurement

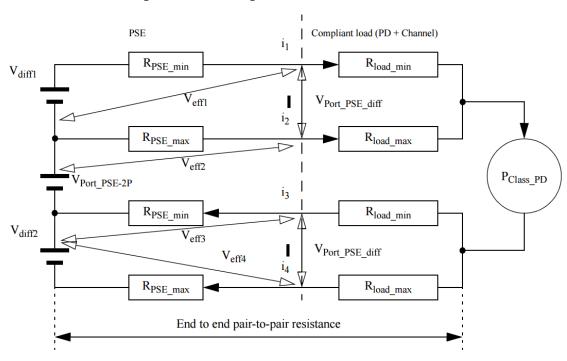

If there is access to internal circuits, effective resistance may be determined by sourcing current in each path corresponding to maximum  $P_{Class}$  operation, and measuring the voltage across all components that contribute to the effective resistance, including circuit board traces and all components passing current to the PSE PI output connection. The effective resistance is the measured voltage  $V_{eff}$ , divided by the current through the path e.g. the effective value of  $R_{PSE\_min}$  for  $i_1$  is  $R_{PSE\_min} = V_{eff1}/i_1$  as shown in Figure 33B–2.

Figure 33B–2—Direct measurements of effective  $R_{PSE\ max}$  and  $R_{PSE\ min}$

# 33B.3 Effective resistance $R_{PSE}$ measurement

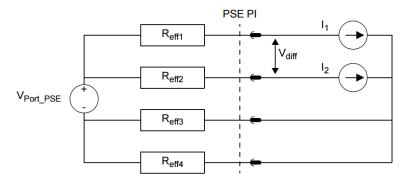

Figure 33B–3 shows a possible test circuit for effective resistance measurements on a PSE port for evaluating conformance to Equation (33B–1) if the internal circuits are not accessible. In Figure 33B–3, the positive pairs of the same polarity are shown as an example. The same concept applies to the negative pairs.

Figure 33B-3—Effective resistance test circuit

The effective resistance test procedure is described below:

1) With the PSE powered on, set the following current values

a. 10 mA <

$$I_2$$

< 50 mA

$$b.\ I_1 = 0.5 \times (P_{max}/V_{port}) - I_2 \label{eq:local_port}$$

- 2) Measure V<sub>diff</sub>.

- 3) Reduce  $I_1$  by 20% (= $I_1$ '). Ensure  $I_2$  remains unchanged.

- 4) Measure  $V_{diff}$ ' in the same manner as  $V_{diff}$ .

- 5) Calculate  $R_{eff1}$ :  $R_{eff1} = [(V_{diff}) (V_{diff}')] / (I_1 I_1')$

- 7) Repeat procedure for  $R_{eff2}$ , with  $I_1$ ,  $I_2$  values swapped.

- 8) Repeat procedure for  $R_{eff3}$ ,  $R_{eff4}$ .

- 9) Evaluate compliance of  $R_{eff1}$  and  $R_{eff2}$  with Equation (33B–1). Evaluate compliance of  $R_{eff3}$ , and  $R_{eff4}$  with Equation (33B–1).