# PD Behavior during PSE Transient D1.2 comment # 232, v3

Fred Schindler, Seen Simply

IEEE 802.3bt Task Force, September 2015, Bonita Springs

# 33.3.7.6 PD behavior ...

- This section exists to ensure that the PSE does not remove power from the PD during a PSE transient.

- This section was added when Type 2 devices were defined.

- This section may be used provide PD requirements during PSE increasing (original case) and decreasing voltages (text added during D1.1, which ensures PD has adequate stored energy).

# 33.3.7.6 System View

This section results in a quantifiable load transient for a multiport PSE system so that the system power supply can be specified.

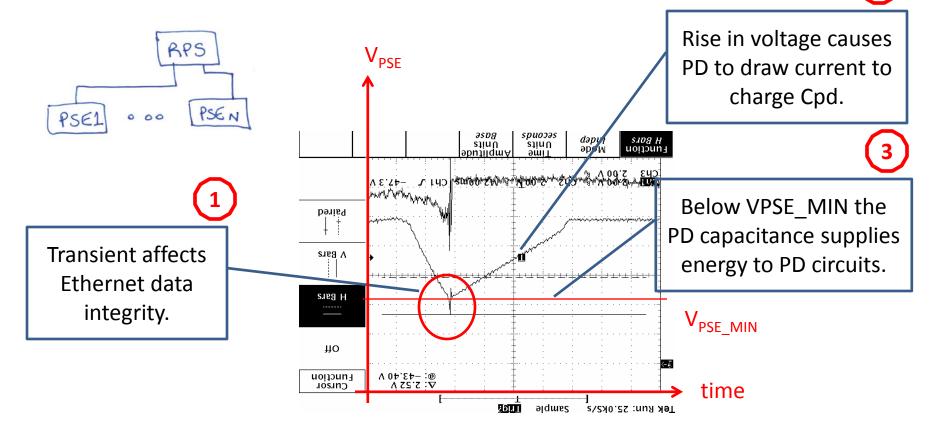

# **PSE Transient**

• One failed PSE supply is backed up by a remote power supply (RPS).

Waveform from schindler\_1\_0107, IEEE 802.3at development effort.

IEEE 802.3bt Task Force, September 2015, Bonita Springs

# System behavior

- The PSE provides current limit ILIM for up to TLIM. (2)

- The PD is not required to provide a current limit unless it exceeds a specific bulk capacitance value.

- A higher channel resistance increases the time for 2 the PD bulk capacitance to reach its voltage.

- A lower channel resistance increases the peak current that charges the PD bulk capacitance. The PD is tested for a possible PSE transient response.

# 33.3.7.6 PD behavior ... 2

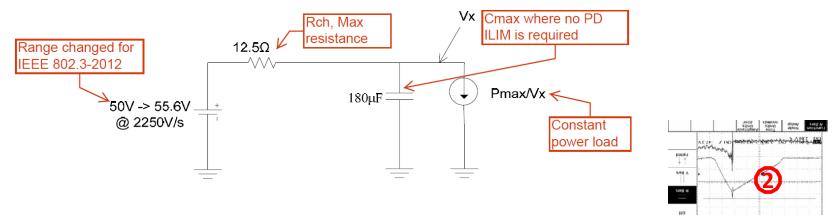

#### 33.3.7.6 PD behavior during transients at the PSE PI

A Type 1 PD with input capacitance of 180  $\mu$ F or less requires no special considerations with regard to transients at the PD PI. A Type 2 PD with peak power draw that does not exceed  $P_{Class_{PD}}$  max and has an input capacitance of 180  $\mu$ F or less requires no special considerations with regard to transients at the PD PI. PDs that do not meet these requirements shall comply with the following:

— A Type 1 PD input current shall not exceed the PD upperbound template (see Figure 33-18) after T<sub>LIM</sub> min (see Table 33-11 for a Type 1 PSE) when the following input voltage is applied. A current limited voltage source is applied to the PI through a R<sub>Ch</sub> resistance (see Table 33-1). The current limit meets Equation (33-14) and the voltage ramps from V<sub>Port\_PSE</sub> min to V<sub>Port\_PSE</sub> max at 2250 V/s.

#### Drawing from vetteth\_1\_0911, IEEE 802.3at development effort.

**Seen Simply**

Eurotion

101-11-10 125-7

# 33.3.7.6 PD behavior ... 1

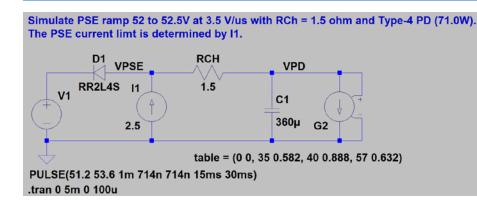

#### 33.3.7.6 PD behavior during transients at the PSE PI

A Type 2 PD shall meet both of the following:

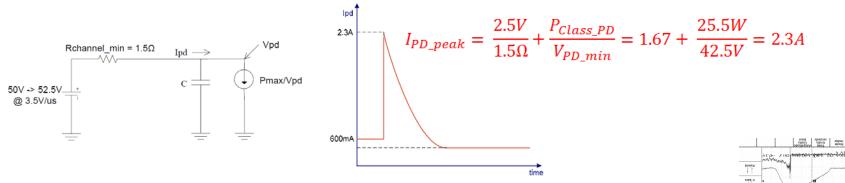

- a) The PD input current spike shall not exceed 2.5 A and shall settle below the PD upperbound template (see Figure 33–18) within 4 ms. During this test, the PD PI voltage is driven from 50 V to 52.5 V at greater than 3.5 V/µs, a source impedance of 1.5 Ω, and a source that supports a current greater than 2.5 A.

- b) The PD shall not exceed the PD upperbound template beyond T<sub>LIM</sub> min under worst-case current draw under the following conditions. The input voltage source drives V<sub>PD</sub> from V<sub>Port\_PSE</sub> min to 56 V at 2250 V/s, the source impedance is R<sub>Ch</sub> (see Table 33–1), and the voltage source limits the current to MDI I<sub>LIM</sub> per Equation (33–14).

The PD input capacitor can be any value.

Drawing from vetteth\_1\_0911, IEEE 802.3at development effort.

IEEE 802.3bt Task Force, September 2015, Bonita Springs

**Seen Simply**

2

### Review

- Transients above 3.5V/us may affect Ethernet data integrity. A PSE will limit dv/dt below this level. PD requirement 1 prevents the PSE from exceeding ILIM after TLIM.

- Equipment tests established dv/dt rates for 2 are less than 2,250 V/s and requirement 2 prevents the PSE from exceeding ILIM after TLIM.

# **New PD Types**

- 4-pair powering , increases current limits and halves Rch for the PI. Current P2P unbalance may exist. The requirement should be written for a powered PD Mode demand.

- Type-3 PDs

- Class-6 is 51.0 W, Extended power is 60.0 W

- 180 uF, TLIM = 10 ms

- Type-4 PDs

- Class-8 is 71.0 W, Extended power is 90.0 W

- 360 uF, TLIM = 6 ms, Start at 52 V.

# 33.3.7.6 PD behavior ...

- The existing PD static operating mask is for the total PD power.

- DS PD are should have the same class value on each Mode. DS PDs were tested the same as SS PDs.

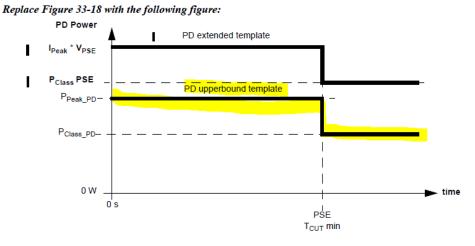

Figure 33–18—PD static operating mask

# New PD Types Test Setup

- Both PD Modes are driven for PD Types that provide 4-pair power.

- Each PD Mode sees the same resistance as the two pair test because half the test current flows through each pair set.

- Current unbalance is not considered and tests resistances on each pairset should be equal.

- The source current limit is doubled when a single source is used.

### **Problems Encountered**

- D1.2 does not provide a scale factor to get PpeakPD for class 6, and classes 7 and 8 when they are not Extended.

- Recommend that these be added to Table 33-18 and use a scale factor of 1.05.

- Note that an Autoclass extension being proposed by Lennart of Philips, should enable PDs to be placed in their maximum power consuming state.

# **New PD Types Simulations**

- Test ① results passes for all Types including for extended classes.

- The peak current seen for higher-power PDs was lower than estimated.

- Test 2 results show significant margin for all Types including for extended classes.

# Proposed baseline text 33.3.7.6 D1.2 page 275

A Type 1 PD with input capacitance of 180  $\mu$ F or less requires no special considerations with regard to transients at the PD PI. A Type 2 or Type 3 PD with peak power draw that does not exceed PClass\_PD max and has an input capacitance of 180  $\mu$ F or less requires no special considerations with regard to transients at the PD PI. A Type 4 PD with peak power draw that does not exceed PClass\_PD max and has an input capacitance of 360  $\mu$ F or less requires no special considerations with regard to transients at the PD PI. PDs that do not meet these requirements shall comply with the following:

— A Type 1 PD input current shall not exceed the PD upperbound template (see Figure 33–18) after TLIM min (see Table 33–11 for a Type 1 PSE) when the following input voltage is applied. A current limited voltage source is applied to the PI through a RCh resistance (see Table 33–1). The current limit meets Equation (33–14) and the voltage ramps from VPort\_PSE min to VPort\_PSE max at limit 2250 V/s.

# Proposed baseline text, continued 33.3.7.6 D1.2 page 275

A Type 2, Type 3, and Type 4 PD that demand less than class 5 power levels shall meet both of the following:

a) The PD input current spike shall not exceed 2.5 A and shall settle below the PD <u>upperbound</u> template (see Figure 33–18) within 4 ms. During this test, the PD PI voltage is driven from <u>VPort\_PSE min</u><del>50 V</del> to <u>VPort\_PSE min</u><u>+</u><u>5</u>2.5 V at greater than 3.5 V/µs, a source impedance <del>of</del><u>within 2.5% of</u> 1.5  $\Omega$ , and a source that supports a current greater than 2.5 A.

b) The PD shall not exceed the PD upperbound template beyond TLIM min under worst-case current draw under the following conditions. The input voltage source drives VPD from VPort\_PSE min to 56 V at 2250 V/s, the source impedance within 2.5% of is-RCh (see Table 33–1), and the voltage source limits the current

to MDI ILIM<u>-2P</u> per Equation (33–14).

# Proposed baseline text, continued 33.3.7.6 D1.2 page 275

<u>A Type 3 or Type 4 PD that demands class 5 power levels shall meet both of the following:</u>

a) The PD Mode input current spike shall not exceed 2.5 A and shall settle below the PD upperbound template value (see Figure 33–18) within 4 ms. During this test, both PD Modes voltage are driven from <u>VPort PSE min to VPort PSE min +2.5 V</u> at greater than 3.5 V/ $\mu$ s, a source impedance within 2.5% of 1.5  $\Omega$ , and a source that supports a current greater than 5.0 A. b) The PD shall not exceed the PD upperbound template beyond TLIM min under worst-case current draw under the following conditions. The input voltage source drives both PD Modes from <u>VPort\_PSE</u> min to 56 V at 2250 V/s, the source impedance within 2.5% of RCh (see Table 33–1), and the voltage source limits the current to MDI ILIM-2P per Equation (33–14).

### Note that this is all new text. Red highlights how legacy Type-2 text was changed to accommodate new PD Types.

IEEE 802.3bt Task Force, September 2015, Bonita Springs

# Proposed baseline text, continued 33.3.7.6 D1.2 page 275

A Type 3 or Type 4 PD that demand more than class 5 power levels shall meet both of the following: a) The PD Mode input current spike shall not exceed **3.0** A and shall settle below the PD extended template value (see Figure 33–18) within 4 ms. During this test, both PD Modes voltage are driven from VPort PSE min to VPort PSE min +2.5 V at greater than  $3.5 \text{ V/}\mu\text{s}$ , a source impedance within 2.5% of  $1.5 \Omega$ , and a source that supports a current greater than 5.0 A. b) The PD shall not exceed the PD upperbound template beyond TLIM min under worst-case current draw under the following conditions. The input voltage source drives both PD Modes from VPort PSE min to 56 V at 2250 V/s, the source impedance within 2.5% of RCh (see Table 33–1), and the voltage source limits the current to MDI ILIM-2P per Equation (33–14).

Note that this is all new text. Yellow highlights how the text on the previous page was changed to accommodate new PD Types.

# Proposed baseline text, continued D1.2 page 275 lines 16 to 21

Type 1, Type 2, and single-signature Type 3 PDs with classes 0 to 4 shall meet the requirement for Cport as defined in Table 33–18 item 9. Type 3 dual-signature PDs with class 0 to 4 shall meet the requirement for Cport as defined in Table 33–18 item 9 for each pairset. For class 5 and 6 singlesignature PDs, if-CPort\_min shall be  $\geq 10\mu F_7$  to support transient behavior has no further requirements. For dual-signature class 5 PDs, this recommendation applies to each pairset. For class 7 and 8 single signature PDs, if-CPort\_min shall be  $\geq 20\mu F_7$  to support transient behavior has no further requirements. For dual-signature Class 5 PDs, this recommendation applies to each pairset. For class 7 and 8 single signature PDs, if-CPort\_min shall be  $\geq 20\mu F_7$  to support transient behavior has no further requirements. See 33.2.7.2 (TBD) or the transient conditions.

Strike Editor's Note,

"2. A drop out specification needs to be added to this section that requires PDs to ride out PSE transients. This is in place of increasing Cport.

# Seen Simply

Turning complexity into understanding.

IEEE 802.3bt Task Force

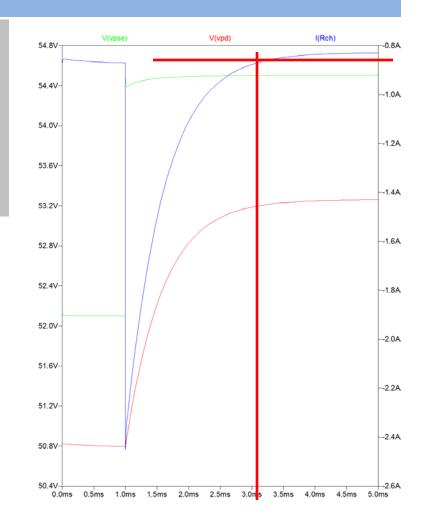

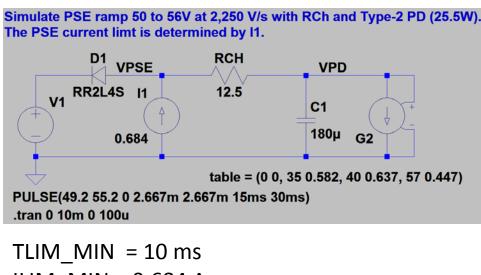

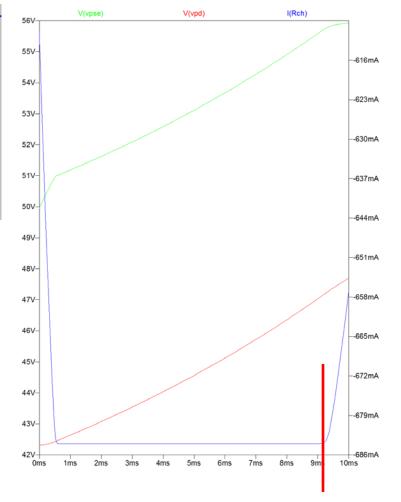

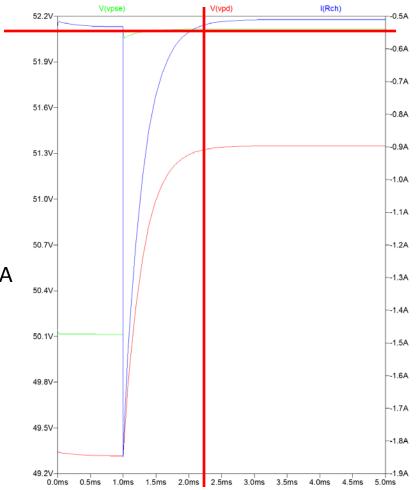

# Type-2 PD, 2,250V Ramp

ILIM\_MIN = 0.684 A

Note that current is higher at the bottom of the graph.

Special thanks to Jean Picard and Dave Dwelley For their input on SPICE simulations.

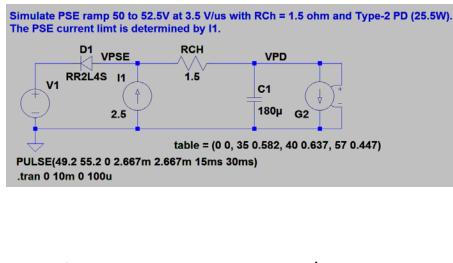

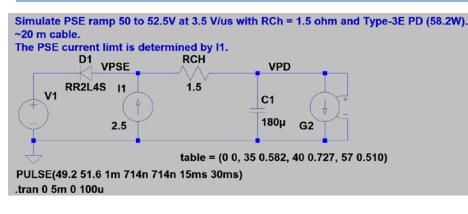

# Type-2 PD, 3.5V/us Ramp

Ppeak\_PD = 28.3 W, I = 28.3W/52.5V = 0.539 A

Subtract 1 ms from a scale value to get the actual value.

# Type-3 PD

Type 3 systems provide 2x Type 2 system but the power limits match on PD Modes.

|            |                  |       |     |                  |         | Estimated | Simulated |

|------------|------------------|-------|-----|------------------|---------|-----------|-----------|

| Туре       | Class            | Power | Rs  | PPD              | VPD_MIN | Ipeak     | Ipeak     |

|            |                  | W     | Ω   | W                | VPD_MIN | А         | Α         |

| 2          | 4                | 2P    | 1.5 | 25.5             | 42.5    | 2.3       | 1.9       |

| 3          | 5                | 4P    | 1.5 | 35.5             | 44.3    | 2.1       |           |

| 3          | 6                | 4P    | 1.5 | 51.0             | 42.5    | 2.3       | 1.9       |

| 3E         | <mark>6</mark> E | 4P    | 1.5 | < 60             |         |           | 2.2       |

| 4          | 7                | 4P    | 1.5 | 62.0             | 42.9    | 2.4       |           |

| 4          | 8                | 4P    | 1.5 | 71.0             | 41.2    | 2.5       | 2.3       |

| <b>4</b> E | <mark>8</mark> E | 4P    | 1.5 | < <del>9</del> 0 |         |           | 2.4       |

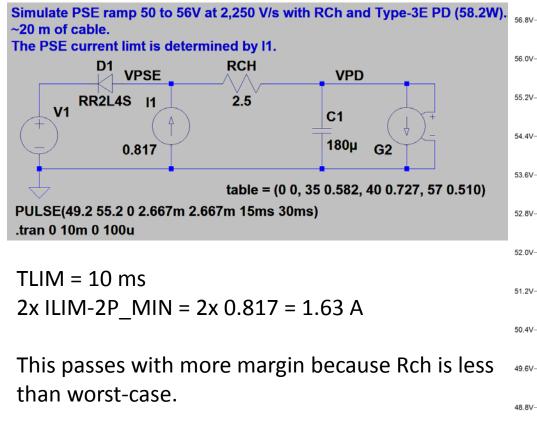

# Type-3 Extended PD, 2,250V Ramp

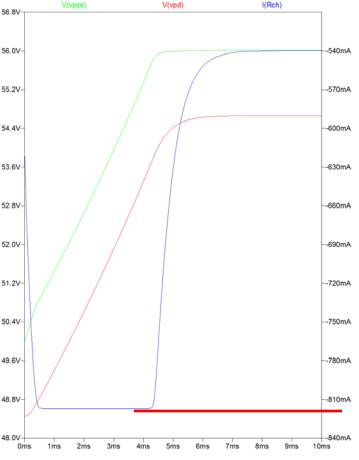

### Type-3 Extended PD, 3.5 V/us Ramp

Ppeak\_PD = 1.05 x PCLASS\_PD = 61.1 W, I = 61.1W/51.6V = 1.18 A = 0.59 A

Note PD is drawing less than Ppeak\_PD.

Subtract 1 ms from a scale value to get the actual value.

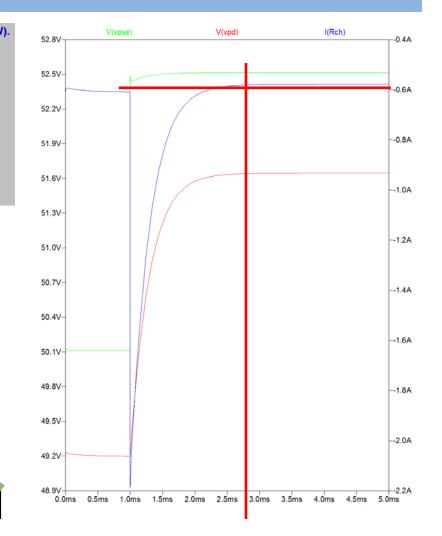

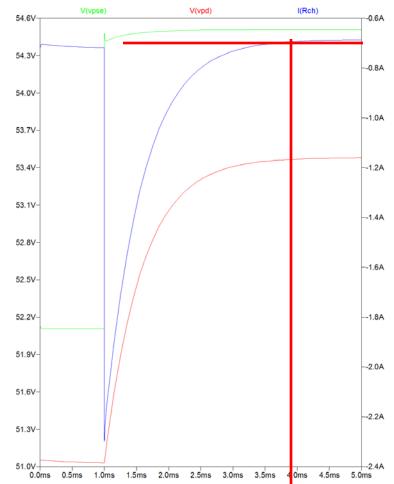

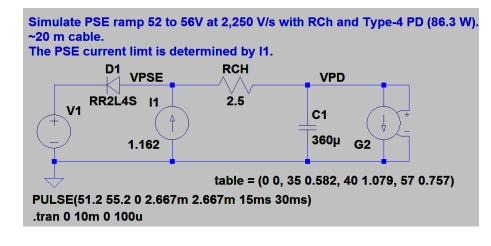

# Type-4 PD, 2,250V Ramp

# Type-4 PD, 3.5 V/us Ramp

Ppeak\_PD = 1.05 x PCLASS\_PD = 74.6 W, I = 74.6W/53.5V = 1.39 A = 2x 0.695 A This is nonExtended class 8.

The PD draw ~73.7 W at 4 ms

Subtract 1 ms from graph value to get actual time from the ramp start.

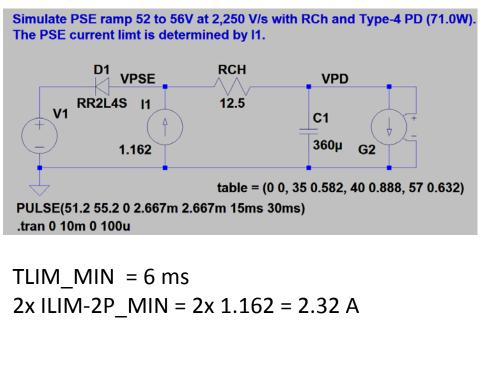

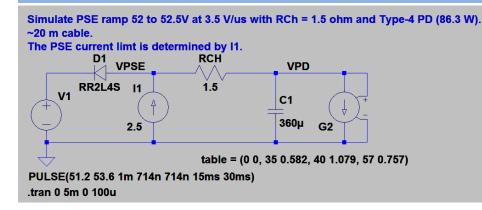

# Type-4 Extended PD, 2,250V Ramp

TLIM\_MIN = 6 ms  $2x ILIM-2P_MIN = 2x 1.162 = 2.32 A$

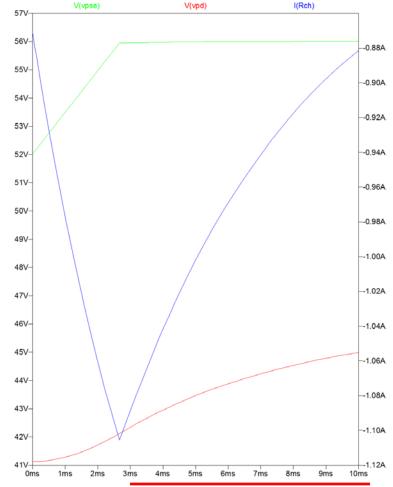

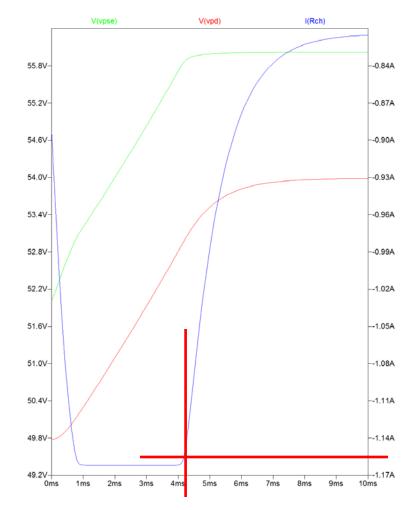

### Type-4 Extended PD, 3.5 V/us Ramp

Ppeak\_PD = 1.05 x PCLASS\_PD = 1.05 x 86.3 W, I = 90.6 W/53.3V = 1.7 A = 2x 0.85 A

The PD draw ~87.8 W at 4 ms

Subtract 1 ms from graph value to get actual time from the ramp start.