# Simplified classification in the State Diagram II v100

#### Info (not part of baseline)

This baseline is the follow up to ➡yseboodt\_01\_1116\_simpleclass.pdf. Aims are as follows:

- 1. The current D2.2 state diagram uses a complex combination of class\_num\_events and pse\_avail\_pwr to control the classification flow. A further problem is that in the D2.1 text several permutations that should be possible are not (eg. A Type 4 PSE can only have pse\_avail\_pwr = 7 or 8) This baseline simplifies this by removing class\_num\_events and only work with pse\_avail\_pwr.

- 2. The variables pd\_req\_power and pd\_allocated\_power are currently returned by a function. The assignment of those variables is however complex (due to power demotion) and should be done explicitly by the SD, rather than 'magically' get filled out by a function.

- 3. An open ticket on the TDL is to implement improved discovery for the PD's requested Class, even for PSEs that have pse\_power\_available ≤ 3. This is implemented through a function do\_class\_probe (which allows flexible implementation) in the new states CLASS\_PROBE and CLASS\_RESET.

- 4. There are several 'shalls' in the Type 3/4 variable list. These are moved to the appropriate sections and struck from the variable list.

## **Simplified classification**

### 33.2.5.9 Type 3 and Type 4 variables

#### Add the following variables:

#### option\_classprobe

This variable indicates if the PSE should determine the requested Class of the PD when pse\_avail\_pwr is less than 3. When set to TRUE, the PSE will issue 3 class events to determine the requested Class, perform a classification reset by applying  $V_{Reset}$  for at least  $T_{Reset}$  to the PI (see Table 33–17), followed by a normal classification procedure. Values:

FALSE: The PSE will not probe for the PD requested Class TRUE: The PSE probes for the PD requested Class

#### pd\_allocated\_pwr

A variable that indicates the Class that has been assigned to the PD. Values:

- 1: Class 1 2: Class 2 3: Class 3 4: Class 4

- 5: Class 5

- 6: Class 6

- 7: Class 7 8: Class 8

- 0. 01455 0

#### Info (not part of baseline)

The pd\_req\_pwr variable (returned by do\_classification) had a shall in it and a may. Both of these have been moved to the classification section. The original text was:

pd\_req\_pwr: This variable indicates the power class requested by the PD. When a PD requests a higher class than a PSE can support, the PSE shall assign the PD Class 3, 4, or 6, whichever is the highest that it can support. For Type 3 and Type 4 PSEs, when connected to a single-signature PD, operating over 4-pairs, classification events may appear on one or both pairsets. See 33.2.7.

pd\_req\_pwr

The variable indicates the power class requested by the PD. When a PD requests a higher Class than a PSE can support, the PSE assigns the PD to Class 3, Class 4, or Class 6, whichever is the highest Class it can support. If pse\_avail\_pwr is less than 5, this variable may not contain the actual requested Class by the PSE; see pd\_req\_pwr\_probe.

Values:

- 0: Class 0 1: Class 1 2: Class 2 3: Class 3 4: Class 4 5: Class 5

- 6: Class 6

- 7: Class 7

- 8: Class 8

#### Info (not part of baseline)

We can now remove Table 33–7 (which ties PSE Type to class\_num\_events) and Table 33–8 (which ties class\_num\_events to pse\_avail\_power). This is then replaced by a Table that links PSE Type to the allowed values of pse\_avail\_power.

#### Change text on page 85 as follows:

Type 3 and Type 4 PSEs shall meet at least one of the allowable variable definition permutations described in Table 33–7 and Table 33–8.

Type 3 and Type 4 PSEs shall set pse\_avail\_pwr, pse\_avail\_pwr\_pri, and pse\_avail\_pwr\_sec from the range in Table 33-7.

#### Remove Table 33–7 and 33–8.

Insert a new Table as follows:

# Table 33–7 — Allowed Type 3 and Type 4 values for pse\_avail\_pwr, pse\_avail\_pwr\_pri, and pse\_avail\_pwr\_sec.

| PSE Type | pse_avail_pwr | pse_avail_pwr_pri,<br>pse_avail_pwr_sec |

|----------|---------------|-----------------------------------------|

| Type 3   | 1 to 6        | 1 to 4                                  |

| Type 4   | 1 to 8        | 1 to 5                                  |

## 33.2.5.11 Type 3 and Type 4 functions

#### Remove variables pd\_req\_pwr and pd\_allocated\_pwr from the do\_classification function.

#### **Rename variables as follows:**

| Old name              | New name         |

|-----------------------|------------------|

| pd_class_detected     | pd_class_sig     |

| pd_class_detected_pri | pd_class_sig_pri |

| pd_class_detected_sec | pd_class_sig_sec |

#### Add a new function do\_class\_probe as follows:

do\_class\_probe

This functions discovers the requested Class of the PD by producing a number of classification events. This function returns the following variables:

pd\_req\_pwr\_probe: This variable contains the requested Class of the PD. Values:

0: Class 0 1: Class 1 2: Class 2 3: Class 3 4: Class 4 5: Class 5 6: Class 6 7: Class 7 8: Class 8

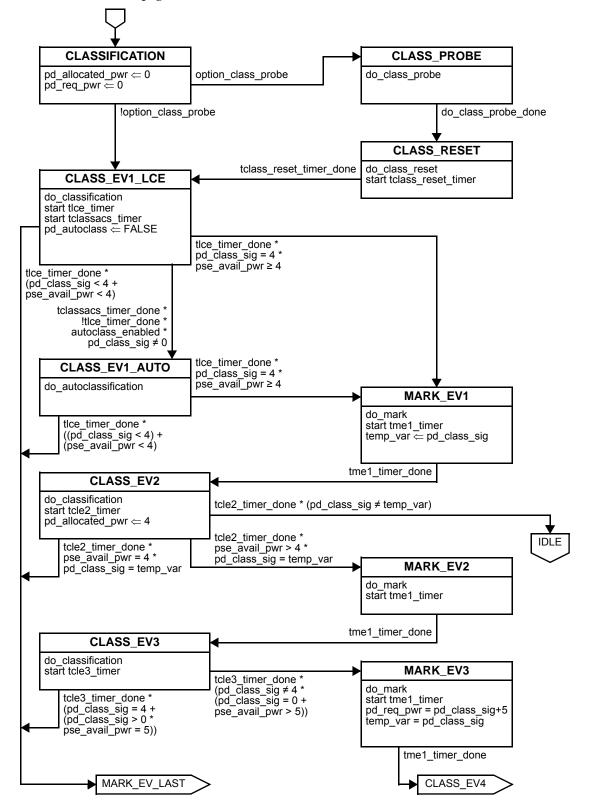

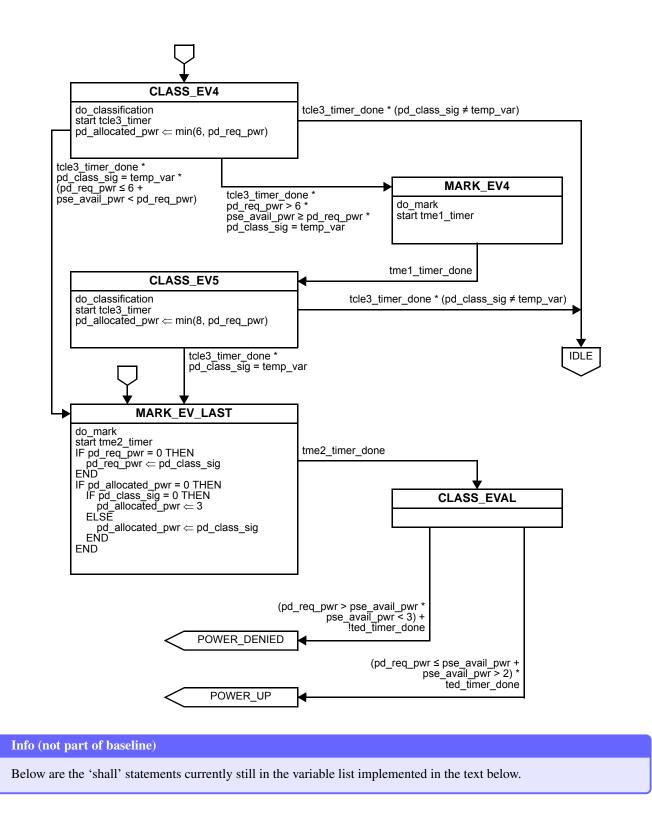

### 33.2.5.12 Type 3 and Type 4 state diagrams

Change the arcs going from DETECT\_EVAL and CXN\_CHK\_DETECT\_EVAL to CLASS\_EV1\_LCE to go to CLAS-SIFICATION in stead.

Remove the CLASS\_EVAL state from page 95.

**Replace the classification SD on page 97 as follows:**

## 33.2.7 PSE classification of PDs and mutual identification

#### Change the text on page 106, line 5 as follows:

Physical Layer classification occurs before a PSE supplies power to a PD, when the PSE asserts a voltage in the range of V Class as defined in Table 33–17 onto one or both pairsets. This is called a class event. The PD responds to each class event with a current representing one of a limited number of classification signatures.

The assigned Class is the result of the PDs requested Class and the number of class events produced by the PSE as shown in Table 33–13 and Table 33–14. See 33.3.6 for PD classification behavior. When a single- signature PD requests a higher Class than a Type 3 or Type 4 PSE can support, the PSE shall assigns the PD to Class 3, 4, or 6, whichever is the highest that it can support. When a dual-signature PD requests a higher Class than a Type 3 or Type 4 PSE can support, the PSE assigns the PD Class 3 or 4, whichever is the highest that it can support.

## 33.2.7.2 PSE Multiple-Event Physical Layer classification

#### Make changes to 33.2.7.2 as follows:

Type 2 PSEs shall provide a maximum of two class events and two mark events. Type 3 and Type 4 PSEs that require more class events for mutual identification than the available power allows may issue a class reset event after performing mutual identification.

Type 3 PSEs

— shall . . .

Type 4 PSEs

— shall ...

Type 3 and Type 4 PSEs that require more class events for mutual identification, or to discover the requested Class of the PD, than the available power allows may issue a class reset event after performing mutual identification or classification.

• • •

All class event voltages and mark event voltages shall have the same polarity as defined for  $V_{Port,PSE-2P}$  in 33.2.4. Type 3 and Type 4 PSEs may issue classification events on one or both pairsets, when connected to a single-signature PD and operating over 4-pairs.

The PSE shall complete Multiple-Event Physical Layer classification and transition to the POWER\_ON, POWER\_ON\_PRI, or POWER\_ON\_SEC state without allowing the voltage at the PI or pairset to go below  $V_{Mark}$  min, unless in the CLASS\_RESET, CLASS\_RESET\_PRI, or CLASS\_RESET\_SEC states. If the PSE returns to the IDLE state, it shall maintain the PI voltage at  $V_{Reset}$  for a period of at least  $T_{Reset}$  min before starting a new detection cycle. If the PSE is in the CLASS\_RESET, CLASS\_RESET\_PRI, or CLASS\_RESET\_SEC state it shall maintain the PI or pairset voltage at  $V_{Reset}$  for a period of at least  $T_{Reset}$  min before starting a new detection cycle. If the PSE is in the CLASS\_RESET, CLASS\_RESET\_PRI, or CLASS\_RESET\_SEC state it shall maintain the PI or pairset voltage at  $V_{Reset}$  for a period of at least  $T_{Reset}$  min.

## Fixes to the PD state diagram

#### Info (not part of baseline)

No default value is set for the variable pse\_dll\_power\_type. This causes an invalid comparison on the exit from MDL\_POWER1 to MDL\_POWER2. Best solution is to set pse\_dll\_power\_type to '1' in the IDLE state.

#### Append the IDLE state in Figure 33–32 with the statement as follows:

$pse_dll_power_type \leftarrow 1$