### **Backfeed Adhoc**

14 May 2018

ON Semiconductor®

# **Backfeed voltage**

ON Semiconductor®

#### Backfeed voltage ... a closer look (single-signature PD)

#### Existing IEEE Std 802.3-2015:

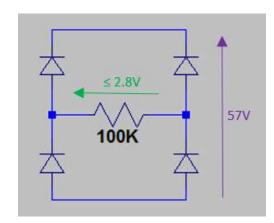

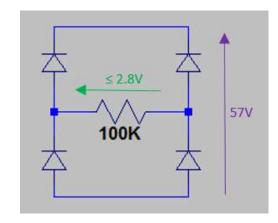

When  $V_{Port\_PD}$  max is applied across the PI at either polarity specified on the conductors for Mode A according to Table 33–13, the voltage measured across the PI for Mode B with a 100 k $\Omega$  load resistor connected shall not exceed  $V_{bfd}$  max as specified in Table 33–18. When  $V_{Port\_PD}$  max is applied across the PI at either polarity specified on the conductors for Mode B according to Table 33–13, the voltage measured across the PI for Mode A with a 100 k $\Omega$  load resistor connected shall not exceed  $V_{bfd}$  max.

#### P802.3bt D3.4:

When any voltage in the range of 0 V to  $V_{Port\_PD-2P}$  max is applied across the PI at either polarity specified on the conductors of either Mode A or Mode B according to Table 145–20, the voltage measured across the PI for the other Mode with a 100 k $\Omega$  load resistor connected across that other Mode shall not exceed  $V_{bfd}$  as defined in Table 145–29.

ON

#### Backfeed voltage ... a closer look (single-signature PD)

#### Existing IEEE Std 802.3-2015:

When  $V_{Port\_PD}$  max is applied across the PI at either polarity specified on the conductors for Mode A according to Table 33–13, the voltage measured across the PI for Mode B with a 100 k $\Omega$  load resistor connected shall not exceed  $V_{bfd}$  max as specified in Table 33–18. When  $V_{Port\_PD}$  max is applied across the PI at either polarity specified on the conductors for Mode B according to Table 33–13, the voltage measured across the PI for Mode A with a 100 k $\Omega$  load resistor connected shall not exceed  $V_{bfd}$  max.

#### Yseboodt\_01\_0518\_backfeed\_baseline:

For a single-signature PD, when any voltage in the range of 0 V to  $V_{Port\_PD-2P}$  max is applied per any of the valid 2-pair configurations, defined in Table 145–20, that have only a single pair connected to positive  $V_{PSE}$  (see Figure 145–29a), the voltage on the Mode not connected to the voltage source, with a  $100 \text{ k}\Omega$  resistor connected across that Mode, shall not exceed  $V_{refl}$  as defined in Table 145–29.

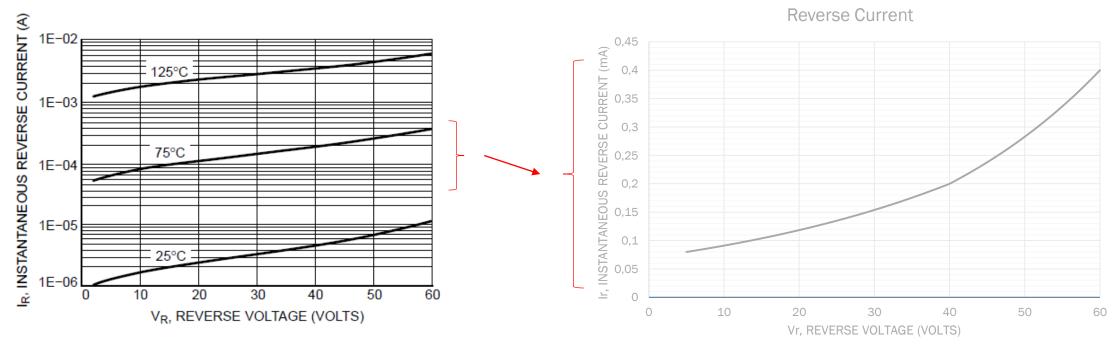

### **Schottky Power Rectifier MBRA160**

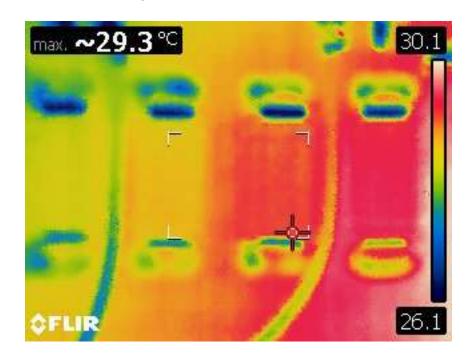

The temperature of the diode bridge on the unpowered pairset will be close to the lead temperature of the diodes conducting the current on the powered pairset.

Figure 3. Typical Reverse Current

A lead temperature around 65°C corresponds to a common operating condition (the same temperature is used to specify the max cable DCR – see 145C.3)

ON

### Backfeed voltage ... a closer look (single-signature PD)

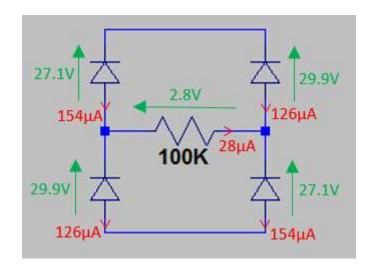

When extending the existing 'symmetrical' backfeed voltage specification to an 'asymmetrical' 3P reflected voltage specification, a significantly larger reflected voltage value can be expected even with PDs using real diode bridges.

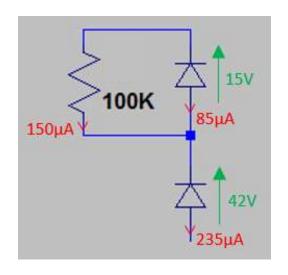

Moreover when introducing a backfeed/reflected current specification and furthermore reducing the  $100 \text{k}\Omega$  down to  $0~\Omega$ , much larger backfeed/reflected currents than  $28 \mu\text{A}~(2.8 \text{V}/100 \text{k}\Omega)$  can be expected (e.g.  $360 \mu\text{A}@57 \text{V}$ ).

# **Backfeed voltage**

Backfeed Voltage as specified in the past and today (P802.3bt D3.4) seems only to prevent significant power dissipation or damage on a pairset not capable of transferring power.

Extending the backfeed voltage specification from a pairset not capable of transferring power to a pairset capable of transferring power but that's not powered up (yet) in a 3P configuration, introduces the risk to make even PDs that use real diode bridges non-compliant.

# Reflected voltage

ON Semiconductor®

We are on the path to introduce a new requirement for 3P detection (Yseboodt\_01\_0518\_backfeed\_baseline):

For a single-signature PD, when any voltage in the range of 0 V to 10.1 V is applied per any of the valid 2-pair configurations, defined in Table 145–20, including those with two pairs connected to positive  $V_{PSE}$  (see Figure 145–29a and Figure 145–29b), the voltage on the Mode with at least one pair not connected to the voltage source, with a  $100 \, \text{k}\Omega$  resistor connected across that Mode, shall not exceed  $V_{refl}$  as defined in Table 145–29.

We should be careful not to introduce any new issues or to be too strict and making solutions non-compliant without reason.

When extending the existing 'symmetrical' detection specifications to an 'asymmetrical' 3P detection specification, again things are different:

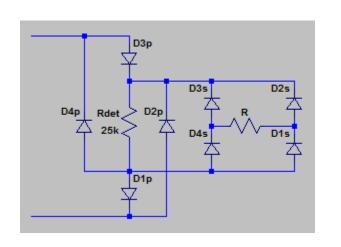

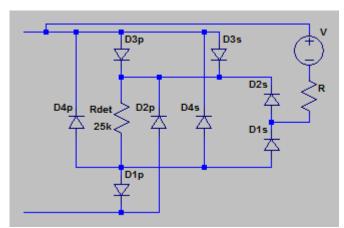

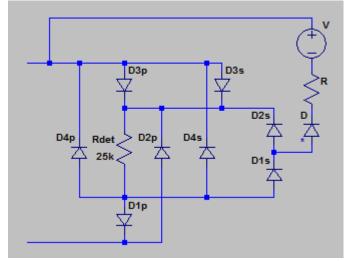

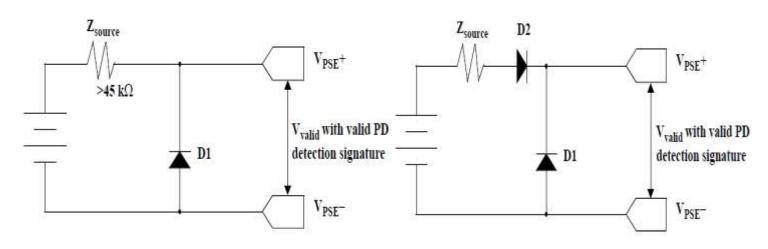

The 2P overall schematic (on the left) versus the new 3P overall schematic(s) (on the right).

The Schottky diode DC leakage current is usually overlooked!

VS

What should be the V, R and (optional?) D for the other mode of the "3P PSE"?

(... if any combination is possible anyhow allowing a "3P PSE")

Some additional background on the schematics on the previous slide:

Figure 145–19—PSE detection source

Figure 145–20—Alternative PSE detection source

The PSE voltage source corresponds to V; the PSE Zsource corresponds with R; the optional diode D2 in the PSE corresponds with D.

D1p, D2p, D3p, D4p form the diode bridge from the PD on the primary alternative (used for detection) D1s, D2s, D3s, D4s form the diode bridge from the PD on the secundary alternative ('not' used for detection)

Will this new text (in Yseboodt\_01\_0518\_backfeed\_baseline) not create unnecessary new issues like making (schottky) diode bridges non-compliant:

For a single-signature PD, when any voltage in the range of 0 V to 10.1 V is applied per any of the valid 2-pair configurations, defined in Table 145–20, including those with two pairs connected to positive  $V_{PSE}$  (see Figure 145–29a and Figure 145–29b), the voltage on the Mode with at least one pair not connected to the voltage source, with a  $100 \text{ k}\Omega$  resistor connected across that Mode, shall not exceed  $V_{refl}$  as defined in Table 145–29.

This text would then cover the case V=0, R=100k and no diode.

This text would then basically become a requirement for diode D1s:

its DC leakage current should be below 28uA for a 7V reverse voltage.

Is this really required to meet 3P detection? (Overall, detection has to do with a current difference for a 1V voltage difference.)

Also, how would this relate to the 1.3mA Irefl requirement for the PSE?

Rather then including this requirement in the Reflected voltage section, For a single-signature PD, when any voltage in the range of 0 V to 10.1 V is applied per any of the valid 2-pair configurations, defined in Table 145–20, including those with two pairs connected to positive V<sub>PSE</sub> (see Figure 145–29a and Figure 145–29b), the voltage on the Mode with at least one pair not connected to the voltage

source, with a  $100 \,\mathrm{k}\Omega$  resistor connected across that Mode, shall not exceed  $V_{\mathrm{refl}}$  as defined in Table 145–29.

shouldn't we rather look at what really matters for 3P detection and include the test requirements for this in the PSE section 145.2.6 (PSE detection of PDs) and PD sections 145.3.4 (PD valid and non-valid detection signatures) and 145.3.5 (PD signature configurations)?

Let's not forget or neglect the Schottky diode DC leakage current!

### Measurements

ON Semiconductor®

#### Measurements - 1

Discrete diode bridge not powered by PoE, far a way from heat source

Vbfd= 6.73mV @ 10V

**Vbfd=47.2mV** @ 57V

3P Reflected voltage over  $100k\Omega$ :

113mV and 123mV @ 10V

57V: 2.12V and 2.4V @ 57V

Perfectly OK for the existing backfeed voltage specification with huge margin: 0.0472V << 2.8V

Coming close to the limit if 3P reflected voltage would be extended to a high voltage.

#### Measurements - 2

Discrete diode bridge not powered by PoE, closer to heat source

Vbfd= 7.65mV @ 10V

**Vbfd=33.4mV** @ 57V

3P Reflected voltage over  $100k\Omega$ :

108mV and 127mV @ 10V

2.4V and 3.34V @ 57V

Perfectly OK for the existing backfeed voltage specification with huge margin: 0.0334V << 2.8V

Would go above the limit if 3P reflected voltage would be extended to a high voltage.

### Conclusions

ON Semiconductor®

#### **Conclusions based on the measurements**

1. The backfeed voltage specification has always been a symmetrical 2P test.

- 2. If the symmetrical 2P backfeed voltage is extended to an asymmetrical 3P reflected voltage, a larger threshold then 2.8V would need to be taken into account for higher operating voltages.

- 3. There is no such thing as a 28uA backfeed current requirement for resistances lower than 100kOhm.

# Conclusion based on full circuit analysis

4. A 4-pair capable PSE that does not switch the positive conductor of the other mode during detection will influence the detection of a single-signature PD.