50 Gb/s Ethernet over a Single Lane and Next Generation 100 Gb/s and 200 Gb/s Ethernet Study Groups Considerations for Cable Assembly, Test Fixture and Channel Specifications

Chris DiMinico MC Communications/PHY-SI LLC/Panduit cdiminico@ieee.org

## Purpose

•Considerations for 50 Gb/s cable assembly, test fixture and channel specifications consistent with adopted objectives

- Define single-lane 50 Gb/s PHYs for operation

- copper twinaxial cables.

- printed circuit board backplane.

- MMF with lengths up to at least 100m.

- SMF with lengths up to at least 2km.

- SMF with lengths up to at least10km

-Define single-lane 200 Gb/s PHYs for operation

- <u>copper twinaxial cables.</u>

- printed circuit board backplane.

- MMF with lengths up to at least 100m.

-Provide physical layer specifications which support 200 Gb/s operation over

- At least 2 km SMF

- At least 2 km SMF

- Define a two lane 100 Gb/s PHY for operation over copper twinaxial cables.

- Define a two lane 100 Gb/s PHY for operation over a printed circuit board backplane.

-Define a two fiber 100 Gb/s PHY for operation over MMF with lengths up to at Least 100m

Source: http://www.ieee802.org/3/50G/public/objectives\_50G\_NGOATH\_01a\_0116.pdf

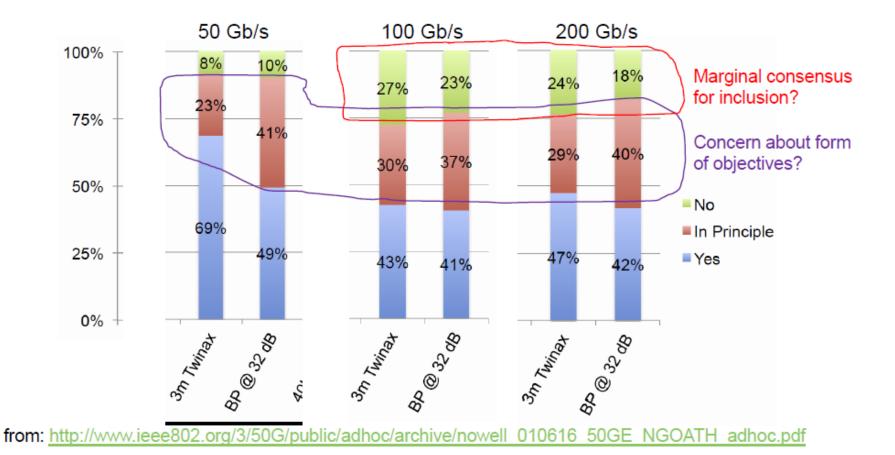

## **Consensus survey monkey**

Survey monkey results were published from Mark Nowell.

### **Consensus survey comments**

| <ul> <li>3m Twinax → 50Gb/s no-FEC option for low-latency applications.<br/>→ We should be open to a slightly shorter reach to ensure practicality.<br/>→ need confirmation of technical feasibility     </li> <li>Backplane → The numbers 32 and 12.9 are wrong. Nyquist frequency for the likely         encoding is approx. 13.3 GHz. The work done in OIF suggests that an insertion loss of         27-28 dB is the limit for reasonable PAM4 transceivers at this rate, far less than 32 dB.         </li> <li><a href="mailto:senip"><i>senip</i></a> I intend to propose an objective for "PCB backplane consistent with a total         insertion loss equivalent to 3m of Twinax cable".         </li> <li>A Need technical feasibility data         <ul> <li>I think an insertion loss in the range of 28 to 30dB is more realistic.</li> <li>More detailed work on Channel loss             <ul> <li>uncertain of the 32 dB limit.</li> </ul> </li> </ul> </li> </ul>                                                    | 50 Gb/s  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3m Twinax       → need BMP data         → We should be open to a slightly shorter reach to ensure practicality.         → Only reach should be defined. Strongly recommend to consider high performance computing applications where latency is critical and Active cable may be needed.         Backplane       → Adoption of a backplane objective is fine. It is not clear what an appropriate insertion loss target should be.         → With serial 100 Gb/s not technically feasible it does not make sense to define 2x50G Cu         → technical feasibility and should mirror 50G objective.         → uncertain of the 32 dB limit.                                                                                                                                                                                                                                                                                                                                                                                        | 100 Gb/s |

| 3m Twinax       → I see no reason to define a 200G copper PMD at this point in time. The primary purpose for such PMDs would be to connect servers to TOR switches         → We should be open to a slightly shorter reach to ensure practicality.         → Only reach should be defined. Strongly recommend to consider high performance computing applications where latency is critical and Active cable may be needed.         Backplane → The numbers 32 and 12.9 are wrong. Nyquist frequency for the likely encoding is approx. 13.3 GHz. The work done in OIF suggests that an insertion loss of 27-28 dB is the limit for reasonable PAM4 transceivers at this rate, far less than 32 dB. <snip> I intend to propose an objective for "PCB backplane consistent with a total insertion loss equivalent to 3m of Twinax cable".         → Same reason as above. I see no need for a 200GE backplane interface at this point in time         → I think an insertion loss         → More detailed work on Channel loss</snip> | 200 Gb/s |

→ uncertain of the 32 dB limit.

### Observation: Common theme is concern for choice of backplane insertion loss number.

from: http://www.ieee802.org/3/50G/public/adhoc/archive/nowell 010616 50GE NGOATH adhoc.pdf

# **Copper twinaxial cables objectives**

•Considerations for 50 Gb/s cable assembly, test fixture and channel specifications consistent with adopted objectives

- Define single-lane 50 Gb/s PHYs for operation

- copper twinaxial cables.

-Define a two lane 100 Gb/s PHY for operation over copper twinaxial cables.

-Define single-lane 200 Gb/s PHYs for operation

• copper twinaxial cables.

•802.3by Adopted and approved Objective

– Define a single-lane 25 Gb/s PHY for operation over links consistent with copper twin axial cables, with lengths up to at least 3m

•Considerations for 50 Gb/s, 100 Gb/s, 200 Gb/s cable assembly, test fixture and channel specifications consistent with adopted objectives

– Define single-lane 50 Gb/s PHYs for operation over links consistent with copper twin axial cables with lengths up to at least 3 m.

–Define two-lane 100 Gb/s PHYs for operation over links consistent with copper twin axial cables with lengths up to at least 3 m.

-Define four-lane 200 Gb/s PHYs for operation over links consistent with copper twin axial cables with lengths up to at least 3 m.

## **Copper twinaxial cables objectives**

•Considerations for 50 Gb/s, 100 Gb/s, 200 Gb/s cable assembly, test fixture and channel specifications consistent with adopted objectives

Define single-lane 50 Gb/s PHYs for operation over links consistent with copper twin axial cables with lengths up to at least 3 m.

–Define two-lane 100 Gb/s PHYs for operation over links consistent with copper twin axial cables with lengths up to at least 3 m.

-Define four-lane 200 Gb/s PHYs for operation over links consistent with copper twin axial cables with lengths up to at least 3 m.

•Length considerations predicated on development of channel insertion loss budget

#### Table 110A–1—Cable insertion loss budget values at 12.8906 GHz

| Parameter            | CA-25G | L CA-25G-S | G CA-25G-N | Units |  |

|----------------------|--------|------------|------------|-------|--|

| IL <sub>Chmax</sub>  | 35     | 29         | 28.02      | dB    |  |

| II. <sub>Camax</sub> | 22.48  | 16.48      | 15.50      | dB    |  |

| IL <sub>Ch0.5m</sub> |        | 20.52      |            |       |  |

| III <sub>Camin</sub> |        | 8          |            | dB    |  |

| III <sub>Host</sub>  |        | 9.85       |            |       |  |

| III_MatedTF          |        | 3.59       |            | æ     |  |

## Leverage of industry investment

| Technology            | Nomenclature       | Description           | Status                                 |

|-----------------------|--------------------|-----------------------|----------------------------------------|

| Backplanes            | 100GBASE-KP4 & KR4 | 4 x 25 Gb/s backplane | IEEE 802.3bj Published                 |

|                       | CEI-56G-LR-PAM4    | 56 Gb/s PAM4          | Straw Ballot                           |

| Chip-to-Module        | CDAUI-8            | 8 x 50 Gb/s PAM4      | IEEE P802.3bs in Task Force Rev        |

|                       | CEI-56G-VSR-PAM4   | 60 Gb/s PAM4          | Straw Ballot                           |

| Chip-to-Chip          | CDAUI-8            | 8 x 50 Gb/s PAM4      | IEEE P802.3bs in Task Force Rev        |

|                       | CEI-56G-MR-PAM4    | 60 Gb/s PAM4          | Straw Ballot                           |

| SMF Optical           | 400GBASE-FR8 & LR8 | 8 x 50 Gb/s PAM4      | IEEE P802.3bs in Task Force            |

|                       | 400GBASE-DR4       | 4 x 100 Gb/s PAM4     | Review                                 |

| Module Form<br>Factor | SFP56              | 1 x 50 Gb/s           | Extension to Summary Document SFF-8402 |

|                       | QSFP56             | 4 x 50 Gb/s           | Extension to Summary Document SFF-8665 |

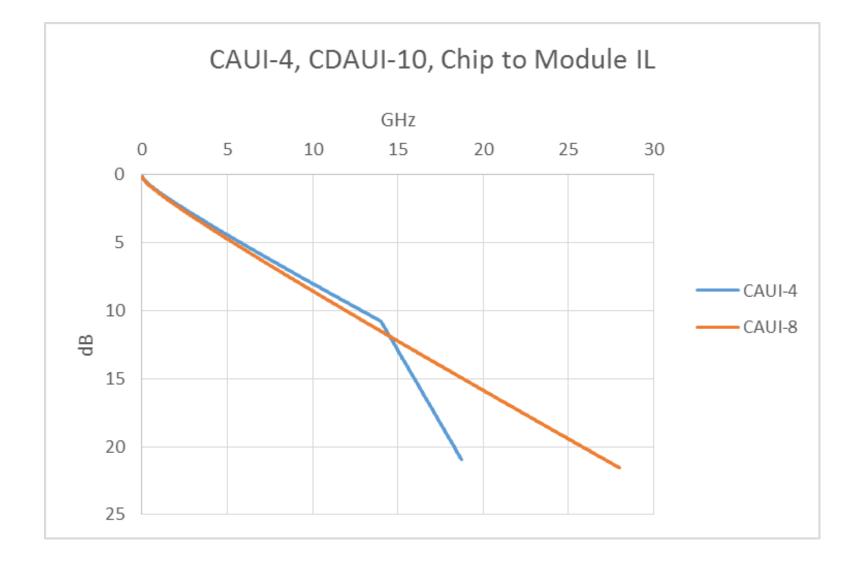

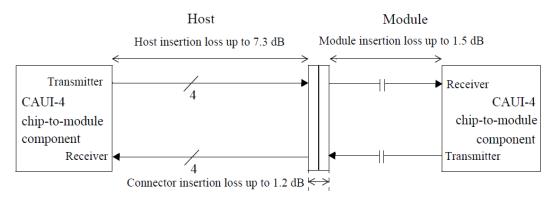

# **CAUI/CDAUI chip-to-module interfaces**

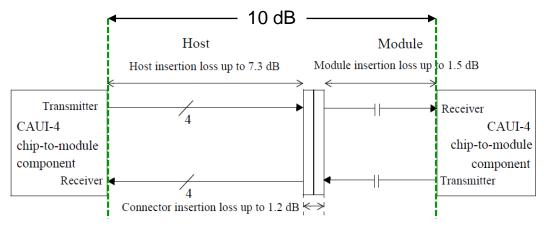

• CAUI-4 signaling rate for each lane is 25.78125 GBd<sup>1</sup>.

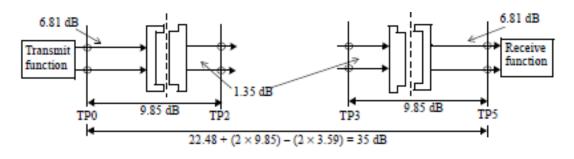

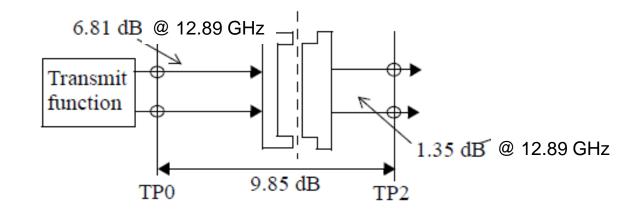

Figure 83E-2-Chip-to-module insertion loss budget at 12.89 GHz

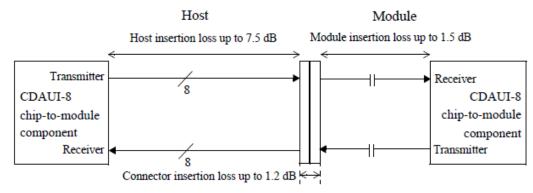

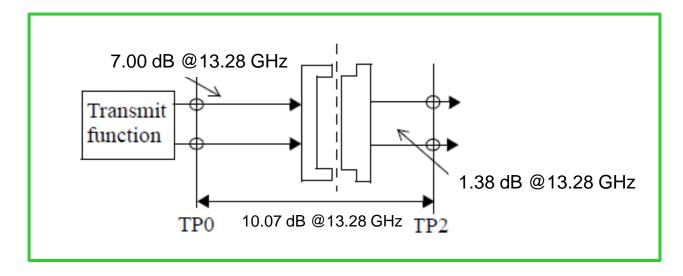

• CDAUI-8 signaling rate for each lane is 26.5625 GBd<sup>2</sup>

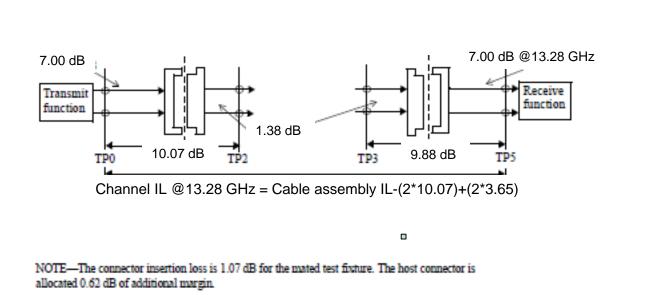

Figure 120E-2-Chip-to-module insertion loss budget at 13.28 GHz

[1] using spec similar to CEI-28G-VSR, [2] using spec similar to CEI-56G-VSR-PAM

# **Host Channels**

• CAUI-4 signaling rate for each lane is 25.78125 GBd<sup>1</sup>.

Figure 83E-2-Chip-to-module insertion loss budget at 12.89 GHz

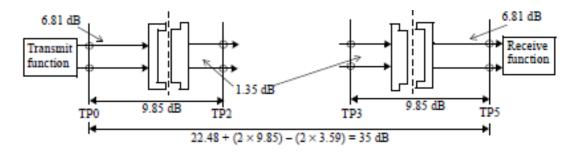

### Figure 110A–1—Host Loss budget at 12.8906 GHz

[1] using spec similar to CEI-28G-VSR, [2] using spec similar to CEI-56G-VSR-PAM

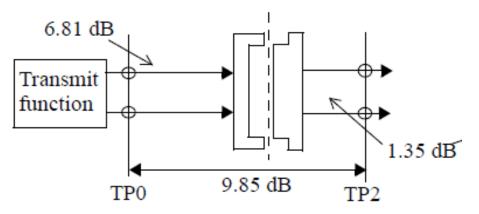

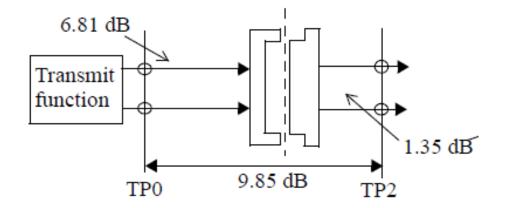

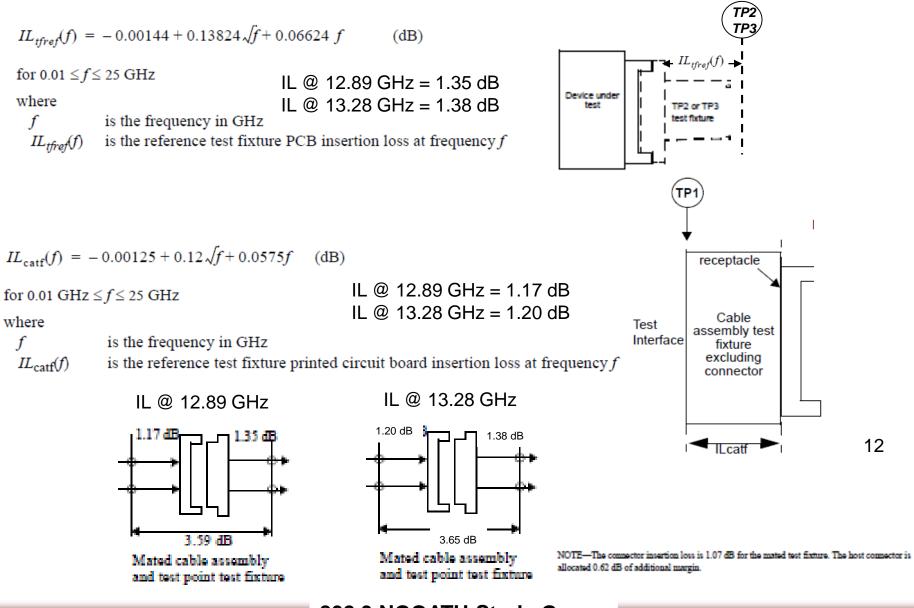

# **Tx/RX PCB and Test Fixture PCB - Baseline**

- Transmitter and receiver differential printed circuit board trace loss (with IL @ 13.28GHz)

- Specified in 92A.4 EQ(92A-1 and 92A-2) referenced 110A.4

- Test fixture printed circuit board reference insertion loss (with IL @ 13.28 GHz)

- Specified in 92.11 EQ(92-35) referenced 110B.1.1

Host Loss budget at 12.8906 GHz

## **Transmitter and receiver differential PCB IL**

(

### IL @ 13.28 GHz

$IL_{PCB}(f) \le IL_{PCBmax}(f) = 0.5(0.0694 + 0.4248\sqrt{f} + 0.9322f)$  (dB)

for 0.01 GHz  $\leq f \leq$  19 GHz.

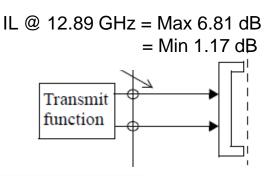

IL @ 12.89 GHz = 6.81 dB IL @ 13.28 GHz = 7.00 dB

where

fis the frequency in GHz $IL_{PCB}(f)$ is the insertion loss for the transmitter and receiver PCB $IL_{PCBmax}(f)$ is the recommended maximum insertion loss for the transmitter and receiver PCB

$$IL_{PCB}(f) \ge IL_{PCBmin}(f) = 0.086(0.0694 + 0.4248\sqrt{f} + 0.9322f)$$

(dB)

for 0.01 GHz  $\leq f \leq$  19 GHz.

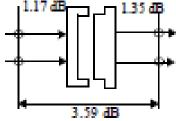

| IL @ 12.89 GHz = <sup>2</sup> | 1.17 dB |

|-------------------------------|---------|

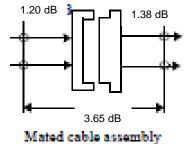

| IL @ 13.28 GHz = <sup>2</sup> | 1.20 dB |

where

$f \\ IL_{PCB}(f) \\ IL_{PCBmin}(f)$

is the frequency in GHz is the insertion loss for the transmitter and receiver PCB is the minimum insertion loss for the transmitter and receiver PCB

## **Test fixtures PCB insertion loss**

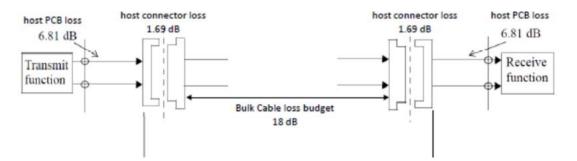

## **Host Channel – Baseline Proposal**

NOTE—The connector insertion loss is 1.07 dB for the mated test fixture. The host connector is allocated 0.62 dB of additional margin. IL host connector @ 12.89 GHz = 9.85-6.81-1.35= 1.69 dB

### http://www.ieee802.org/3/bj/public/may12/diminico\_01a\_0512.pdf

### Host Tx and Rx PCB losses

•Transmitter and receiver differential printed circuit board trace loss

|                                                                               |          |  | Attenuation* (dB/in) at: | 1 GHz  | 6.5 GHz              | 7 GHz  | 12.89 GHz | 14 GHz | S -            |        |     |

|-------------------------------------------------------------------------------|----------|--|--------------------------|--------|----------------------|--------|-----------|--------|----------------|--------|-----|

| GHz                                                                           | dB/in    |  | Meg6_LowSR - Wide        | 0.0951 | 0.4159               | 0.4433 | 0.7562    | 0.8127 | PROPO<br>RAPHS |        |     |

| 1                                                                             | 0.1856   |  | Meg6_LowSR - Narrow      | 0.1466 | 0.5849               | 0.6205 | 1.0152    | 1.0847 | POS            |        |     |

| 0.5                                                                           |          |  | Meg6_HighSR – Wide       | 0.1175 | 0.5960               | 0.6367 | 1.0891    | 1.1688 | ON SED         |        |     |

| 6.5                                                                           | 0.8971   |  |                          | [      | Meg6_HighSR - Narrow | 0.1856 | 0.8971    | 0.9557 | 1.5924         | 1.7020 | PRE |

| 7                                                                             | 0.9557   |  | ImpFR4_LowSR – Wide      | 0.1202 | 0.6096               | 0.6541 | 1.1772    | 1.2734 | RAN            |        |     |

| 12.89                                                                         | 1.5924 / |  | ImpFR4_LowSR - Narrow    | 0.1717 | 0.7794               | 0.8323 | 1.4410    | 1.5512 | AMET           |        |     |

| 12.03                                                                         | 1.5524   |  | ImpFR4_HighSR Wide       | 0.1427 | 0.7904               | 0.8484 | 1.5158    | 1.6367 | S 1            |        |     |

| 14                                                                            | 1.702    |  | ImpFR4_HighSR - Narrow   | 0.2106 | 1.0930               | 1.1692 | 2.0283    | 2.1813 | DE S           |        |     |

| *using Algebraic Model v2.02a - see backup slides for values entered in Model |          |  |                          |        |                      |        |           |        |                |        |     |

Proposal for Defining Material Loss 26-Jan 12 Elizabeth Kochuparambil Joel Goergen

http://www.ieee802.org/3/bj/public/jan12/kochuparambil\_01a\_0112.pdf

Cisco

802.3bj Cu specifications

802.3 NGOATH Study Group

12

# **Channel Insertion Loss**

Table 110A-1—Cable insertion loss budget values at 12.8906 GHz

| Parameter            | CA-25G-L                  | CA-25G-S | CA-25G-N | Units |  |

|----------------------|---------------------------|----------|----------|-------|--|

| II. <sub>Chmax</sub> | IL <sub>Chmax</sub> 35 29 |          | 28.02    | dB    |  |

| III <sub>Camax</sub> | 22.48                     | 16.48    | 15.50    | dB    |  |

| IL <sub>Ch0.5m</sub> |                           | 20.52    |          |       |  |

| III <sub>Camin</sub> |                           | 8        |          |       |  |

| II_Host              |                           | 9.85     |          |       |  |

| III_MatedTF          |                           | 3.59     |          |       |  |

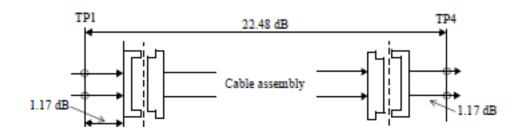

Channel IL @12.89 GHz = Cable assembly IL-(2\*9.85)+(2\*3.59)

.17 dB\_\_\_\_\_ 1.35 dB

IL @ 12.89 GHz

Mated cable assembly and test point test fixture

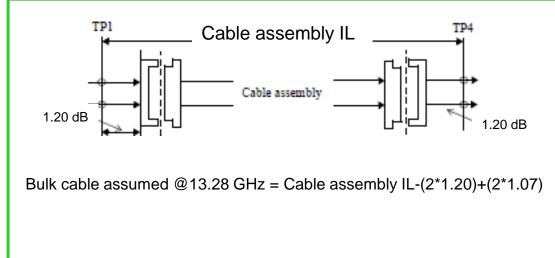

IL @ 13.28 GHz

and test point test fixture

# **Cable Assembly Insertion Loss**

Bulk cable assumed = Cable assembly IL-(2\*1.17)+(2\*1.07)

Bulk cable assumed = Channel IL- (2\*6.81)+(2\*1.69)

NOTE—The connector insertion loss is 1.07 dB for the mated test fixture. The host connector is allocated 0.62 dB of additional margin.

802.3 NGOATH Study Group

|                  | Cable assembly |               |

|------------------|----------------|---------------|

| Channel IL (dB)@ | IL (db)@ 12.89 | Bulk cable dB |

| 12.98 GHz        | GHz            | @ 12.89 GHz   |

| 27.0             | 14.48          | 10.00         |

| 27.5             | 14.98          | 10.50         |

| 28.0             | 15.48          | 11.00         |

| 28.02            | 15.50          | 11.02         |

| 28.5             | 15.98          | 11.50         |

| 29.0             | 16.48          | 12.00         |

| 29.5             | 16.98          | 12.50         |

| 30.0             | 17.48          | 13.00         |

| 30.5             | 17.98          | 13.50         |

| 31.0             | 18.48          | 14.00         |

| 31.5             | 18.98          | 14.50         |

| 32.0             | 19.48          | 15.00         |

| 32.5             | 19.98          | 15.50         |

| 33.0             | 20.48          | 16.00         |

| 33.5             | 20.98          | 16.50         |

| 34.0             | 21.48          | 17.00         |

| 34.5             | 21.98          | 17.50         |

| 35.0             | 22.48          | 18.00         |

#### Table 110A-1-Cable insertion loss budget values at 12.8906 GHz

| Parameter            | CA-25G-L | CA-25G-S | CA-25G-N | Units |  |  |

|----------------------|----------|----------|----------|-------|--|--|

| IL <sub>Chmax</sub>  | 35       | 35 29    |          | dB    |  |  |

| III <sub>Camax</sub> | 22.48    | 16.48    | 15.50    | dB    |  |  |

| IL <sub>Ch0.5m</sub> |          | 20.52    |          |       |  |  |

| III <sub>Camin</sub> |          | dB       |          |       |  |  |

| III <sub>Host</sub>  |          | 9.85     |          |       |  |  |

| III_MatedTF          |          | 3.59     |          |       |  |  |

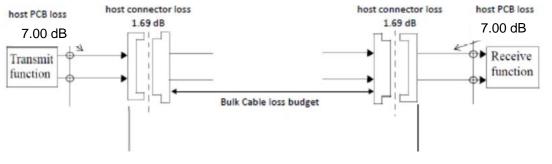

### **Baseline Proposal - starting point (3 m cable assembly)**

Bulk cable assumed @13.28 GHz = Channel IL- (2\*7)+(2\*1.69)

NOTE—The connector insertion loss is 1.07 dB for the mated test fixture. The host connector is allocated 0.62 dB of additional margin.

| Channel IL (dB) | Cable assembly IL | Bulk cable dB |

|-----------------|-------------------|---------------|

| @ 13.28 GHz     | (db) @ 13.28 GHz  | @ 13.28 GHz   |

| 27.0            | 14.16             | 9.62          |

| 27.5            | 14.66             | 10.12         |

| 28.0            | 15.16             | 10.62         |

| 28.5            | 15.66             | 11.12         |

| 29.0            | 16.16             | 11.62         |

| 29.5            | 16.66             | 12.12         |

| 30.0            | 17.16             | 12.62         |

| 30.5            | 17.66             | 13.12         |

| 31.0            | 18.16             | 13.62         |

| 31.5            | 18.66             | 14.12         |

| 32.0            | 19.16             | 14.62         |

| 32.5            | 19.66             | 15.12         |

| 33.0            | 20.16             | 15.62         |

| 33.5            | 20.66             | 16.12         |

| 34.0            | 21.16             | 16.62         |

| 34.5            | 21.66             | 17.12         |

| 35.0            | 22.16             | 17.62         |

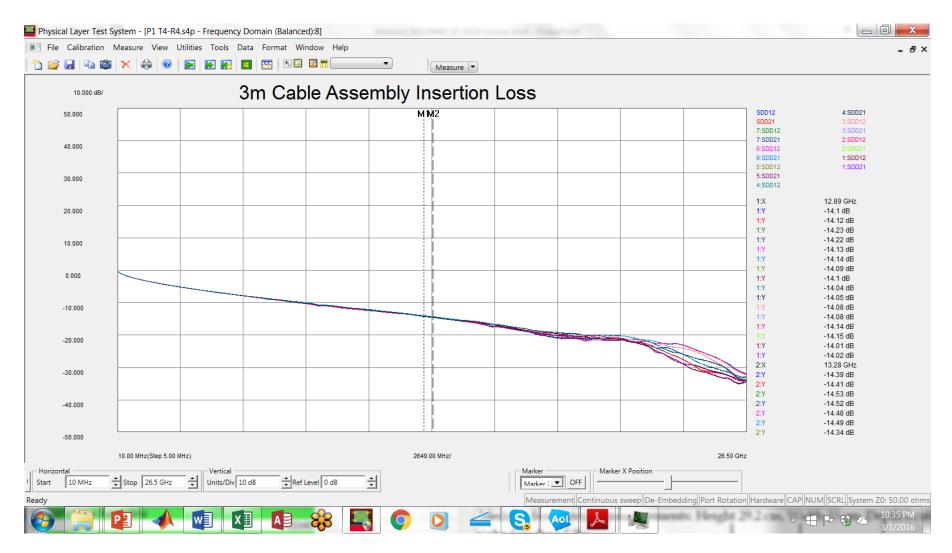

# **NGOATH Contributed Channel Data**

http://www.ieee802.org/3/50G/public/channel/index.html

*Molex\_zQSFP-zQSFP\_3m\_26awg*

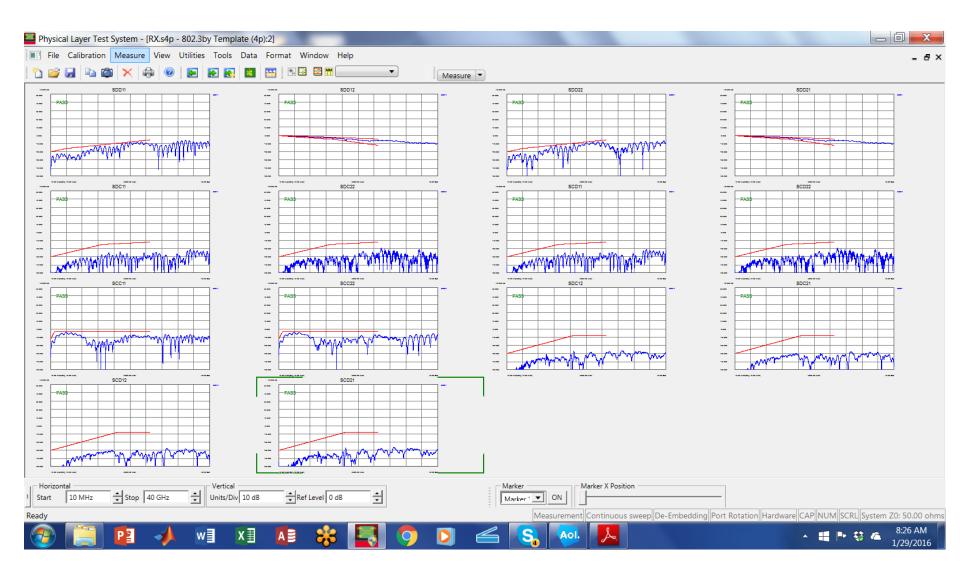

### **Cable Assembly – Baseline Proposal**

• Cable assembly - consistent with CL92 and CL110 – referenced parameters @ 13.28 GHz

Table 92–10—Cable assembly differential characteristics summary

| Description                                 | Reference | Value            | Unit |

|---------------------------------------------|-----------|------------------|------|

| Maximum insertion loss at 12.8906 GHz       | 92.10.2   | 22.48            | dB   |

| Minimum insertion loss at 12.8906 GHz       | 92.10.2   | 8                | dB   |

| Minimum return loss at 12.8906 GHz          | 92.10.3   | 6                | dB   |

| Differential to common-mode return loss     | 92.10.4   | Equation (92–28) | dB   |

| Differential to common-mode conversion loss | 92.10.5   | Equation (92-29) | dB   |

| Common-mode to common-mode return loss      | 92.10.6   | Equation (92-30) | dB   |

Table 110-10-Cable assembly characteristics summary

| Description                                     | Reference | CA-25G-L         | CA-25G-S | CA-25G-N | Unit |

|-------------------------------------------------|-----------|------------------|----------|----------|------|

| Maximum insertion loss at 12.8906 GHz           | 110.10.2  | 22.48            | 16.48    | 15.5     | dB   |

| Minimum insertion loss at 12.8906 GHz           | 110.10.2  | 8                |          | dB       |      |

| Minimum differential return loss at 12.8906 GHz | 110.10.3  | 6                |          |          | dB   |

| Differential to common-mode return loss         | 110.10.4  | Equation (92-28) |          | 8)       | dB   |

| Differential to common-mode conversion loss     | 110.10.5  | Equation (92-29) |          | 9)       | dB   |

| Common-mode to common-mode return loss          | 110.10.6  | Equation (92-30) |          | dB       |      |

| COM                                             | 110.10.7  | See Table 110-11 |          | 1        | dB   |

from [0.01/0.05/0.2] ≤ f ≤ 19 GHz

# **COM-** Baseline Proposal

- COM consistent with methodology CL92 and CL110

- COM parameter values TBD

#### Table 110–11—COM parameter values

| Parameter                                                                                                                                                       | Symbol                  | CA-25G-N                           | CA-25G-8           | CA-25G-L <sup>a</sup> | Units |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------|--------------------|-----------------------|-------|

| Signaling rate                                                                                                                                                  | ſb                      |                                    | 25.78125           |                       | GBd   |

| Maximum start frequency                                                                                                                                         | ſmin                    |                                    | 0.05               |                       | GHz   |

| Maximum frequency step <sup>b</sup>                                                                                                                             | Δf                      | 0.01                               |                    | GHz                   |       |

| Device package model<br>Single-ended device capacitance<br>Transmission line length, Test 1<br>Transmission line length, Test 2<br>Single-ended package capacit | $C_d$<br>$z_p$<br>$z_p$ | 2.5 × 10 <sup>-4</sup><br>12<br>30 |                    | nF<br>HH<br>HH        |       |

| board interface                                                                                                                                                 | P                       |                                    | 1.5 10-4           |                       | nF    |

| Single-ended reference resistance                                                                                                                               | θ.                      |                                    | 50                 |                       | Ω     |

| Single-ended termination resistance                                                                                                                             | Ra                      | 57                                 |                    | Ω                     |       |

| Receiver 3 dB bandwidth                                                                                                                                         |                         | ~ <i>f</i> b                       |                    | GHz                   |       |

| Transmitter equalizer, minimum cursor coefficient                                                                                                               | c(0)                    | 0.62                               |                    |                       |       |

| Transmitter equalizer, pre-cursor coefficient<br>Minimum value<br>Muximum value<br>Step size                                                                    | c(-1)                   |                                    | -0.18<br>0<br>0.02 |                       |       |

| Transmitter equalizer, post-cursor coefficient<br>Minimum value<br>Maximum value<br>Step size                                                                   | c(1)                    |                                    | -0.38<br>0<br>0.02 |                       |       |

| Continuous time filter, DC gain<br>Minimum value<br>Maximum value<br>Step size                                                                                  | 8 <sub>DC</sub>         | -16<br>0<br>1                      | -12<br>0<br>1      | -12<br>0<br>1         | 888   |

| Continuous time filter, zero frequency                                                                                                                          | fz.                     |                                    | $f_{b}/4$          |                       | GHz   |

| Continuous time filter, pole frequencies                                                                                                                        | $\int_{\mathbb{P}^2}$   | 56/4<br>56                         |                    | GHz                   |       |

#### Table 110–11—COM parameter values (continued)

| Parameter                                                                                         | Symbol               | CA-25G-N               | CA-25G-5 | CA-25G-L <sup>a</sup> | Units |

|---------------------------------------------------------------------------------------------------|----------------------|------------------------|----------|-----------------------|-------|

| Transmitter differential peak output voltage<br>Victim<br>Far-end aggressor<br>Near-end aggressor | Ay<br>Age<br>Age     | 0.4<br>0.6<br>0.6      |          | v<br>v<br>v           |       |

| Number of signal levels                                                                           | L                    | 2                      |          |                       |       |

| Level separation mismatch ratio                                                                   | RIM                  | 1                      |          |                       |       |

| Transmitter signal-to-noise ratio                                                                 | SNR <sub>TX</sub>    | 21                     |          | 27                    | dB    |

| Number of samples per unit interval                                                               |                      |                        |          |                       |       |

| Decision feedback equalizer (DFE) lengt                                                           | Nb                   |                        |          |                       |       |

| Normalized DFE coefficient magnitude limit, for $n = 1$ to $N_b$                                  | b <sub>max</sub> (n) | 0.35                   | 0.5      | 1                     | -     |

| Random jitter, RMS                                                                                | $\sigma_{RJ}$        | 0.01                   |          | UI                    |       |

| Dual-Dirac jitter, peak                                                                           | ADD                  | 0.05                   |          | UI                    |       |

| One-sided noise spectral density                                                                  | ηο                   | 5.2 × 10 <sup>-8</sup> |          | V <sup>2</sup> /GHz   |       |

| Target detector error ratio                                                                       | DER <sub>0</sub>     | 10-12                  | 10-8     | 10-5                  | -     |

| Channel Operating Margin (min.)                                                                   | СОМ                  | 3°                     | 3        | 3                     | dB    |

The parameters for CA-25G-L are the same as those for 100GBASE-CR4 (Table 93-8), except for Ag.

<sup>b</sup>For cable lengths greater than 4 m, a frequency step (Λ/) no larger than 5 MHz is recommended. <sup>c</sup>For CA-25G-N cable assemblies with insertion loss at 12.8906 GHz greater than 12 dB, the minimum COM is relaxed.

Consider: config\_com\_ieee8023\_93a=CDAUI-8-C2C\_D1p1\_mellitz\_01\_0116.xls

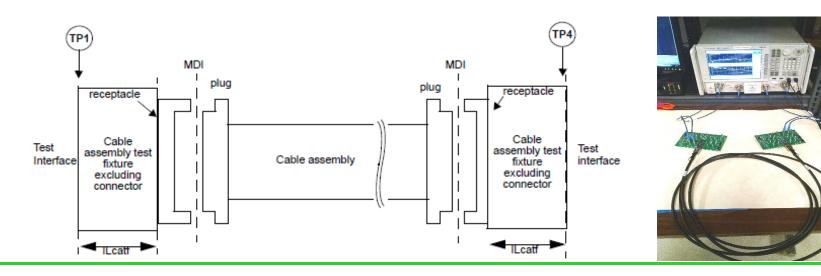

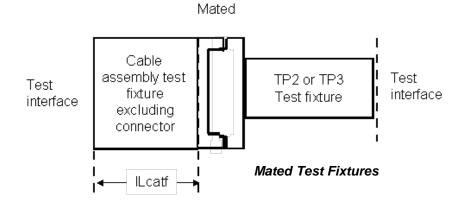

## **Test Fixtures**

- Test Fixture specifications consistent with CL92 and CL110

- Test fixtures specified in a mated state used for testing the transmitter, the receiver and cable assembly measurements

- The TP2/TP3 test fixture also known in the industry as Host Compliance Board (HCB) is required for measuring the transmitter specifications at TP2 and the receiver return loss at TP3.

- The cable assembly test fixture also known in the industry as Module Compliance Board (MCB) is required for measuring the cable assembly specifications at TP1 and TP4.

## **Test Fixtures - Baseline Proposal**

• Test Fixture specifications - consistent with CL92 and CL110

| Parameter description                         | f(GHz)    | Unit |

|-----------------------------------------------|-----------|------|

| Maximum insertion Loss                        | 0.01≤f≤25 | dB   |

| Minimum Insertion Loss                        | 0.01≤f≤25 | dB   |

| Minimum Return Loss                           | 0.01≤f≤25 | dB   |

| Common-mode conversion insertion loss         | 0.01≤f≤25 | dB   |

| Common-mode return loss                       | 0.01≤f≤25 | dB   |

| Common-mode to differential –mode return loss | 0.01≤f≤25 | dB   |

| Integrated crosstalk noise                    |           |      |

### Mated test fixtures parameters

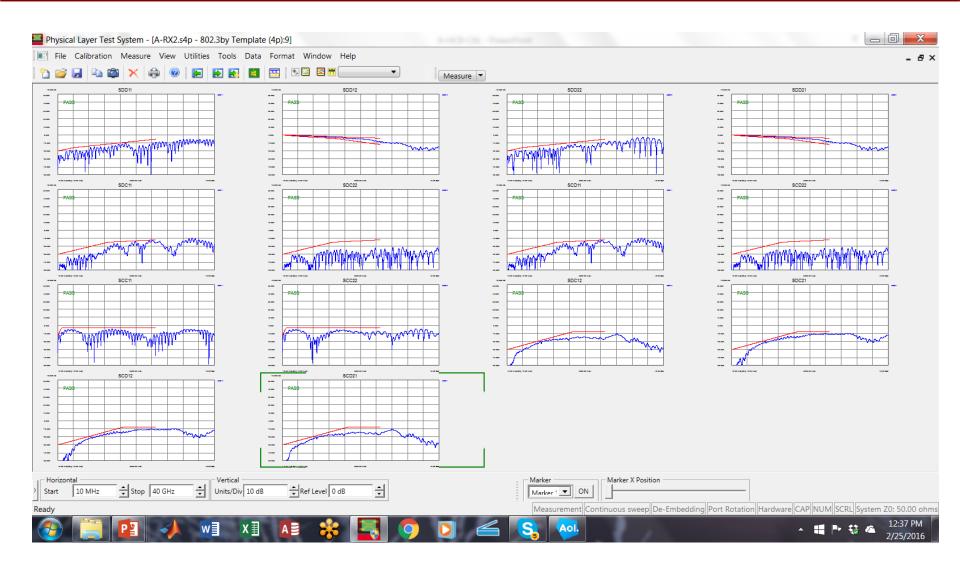

### SFP28-Mated Test Fixture – 802.3bj/802.3by Specification

### QSFP28-Mated Test Fixture – 802.3bj/802.3by Specification

# BACKUP

## CAUI-4/CDAUI-10 chip-to-module interfaces

• CAUI-4 signaling rate for each lane is 25.78125 GBd<sup>1</sup>.

$$Insertion\_loss(f) \leq \left\{ \begin{array}{cc} 1.076(0.075 + 0.537\sqrt{f} + 0.566f) & 0.01 \leq f < 14 \\ 1.076(-18 + 2f) & 14 \leq f < 18.75 \end{array} \right\} (dB)$$

(83E-1)

where

fis the frequency in GHzInsertion\_loss(f)is the CAUI-4 chip-to-module insertion loss

• CDAUI-8 signaling rate for each lane is 26.5625 GBd<sup>2</sup>

```

Insertion\_loss(f) \le 1.076(0.0801 + 0.5736\sqrt{f} + 0.6046f) \quad (dB)for 0.01 \le f \le 28.05 (120E-1)

```

where

fis the frequency in GHzInsertion\_loss(f)is the CDAUI-8 chip-to-module insertion loss

[1] using spec similar to CEI-28G-VSR, [2] using spec similar to CEI-56G-VSR-PAM

### CAUI-4/CDAUI-10 chip-to-module interfaces