### PCS and AUI Considerations for 50 GbE and NG 100 GbE

Ali Ghiasi Ghiasi Quantum LLC

**NGOATH Adhoc**

April 27, 2016

### Compatibility, Synergy, and Interaction with FEC

- During the study group need to investigate ideally a common FEC addressing all 50 GbE PMDs with likely choices:

- RS-FEC (528,514)

- RS-FEC (544,514)

- During the study phase need to investigate if RS-FEC (528,514) can meet NGOATH 100 GbE PMDs requirements:

- If RS-FEC (528,514) can meet NG PMDs requirements preferable for backward compatibility otherwise KP4 should be considered

- Legacy 100 GbE PMD use all of the KR4 FEC gain unless CAUI-2 can operate error free similar to CAUI-4 (1E-15) compatibility with legacy PMDs may not be feasible

- **50G/lane Cu and optical PMDs should drive the FEC choice and coding gain**

- Bit mux would be preferable but may have a penalty under burst error

- Symbol mux advantage is that data could come from two logical lanes without penalty

- Transition to 50G/lane optics may happen faster than migration to ASICs with 50G IO

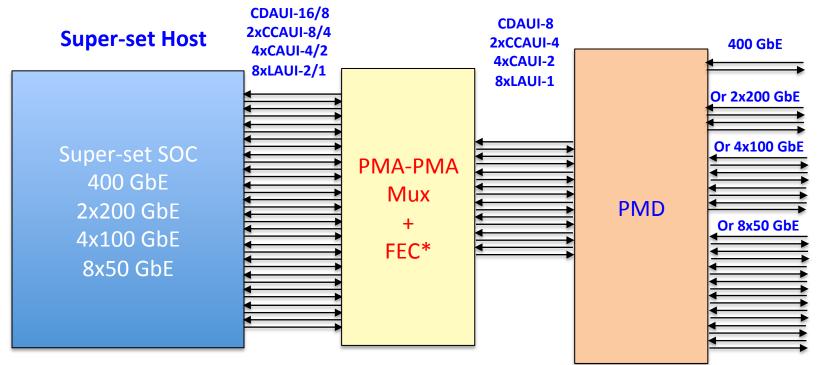

- 50 GbE or NG 100 GbE implementation may take advantage of 400 GbE hardware which supports 16x25G electrical but 50G/lane or 100G/lane optics

- To support flexible migration the 50 GbE PCS and NG 100 GbE PCSs should support respectively 50AUI-2/1 and CAUI-4/2 PMAs

- It assumed that 50GAUI-2 and CAUI-4 are based on 2 and 4 lanes NRZ respectively

- It assumed that 50GAUI-1 and CAUI-2 are based on 2 and 4 lanes PAM4 respectively

- Application overlay should be key consideration to allow building common ports supporting overlay/breakout ports

- 1x400GbE, 2x200GbE, 4x100GbE, 8x50GbE.

000000

000000

-^^/-

#### 000000 Option I: 50 GbE and NG 100GbE Base on Clean $\neg \land \land \land \rightarrow$ Sheet of Paper Based on 25G PCS Lane 000000 **Bases for** 25G PCS lanes builds on synergy with 400 GbE PCS format 50 GbE PCS http://www.ieee802.org/3/bs/public/adhoc/logic/feb9 16/gustlin 01 0216 logic.pdf Bits 60-69 70-79 80-89 90-99 100-109 110-119 120-129 0-9 10-19 20-29 30-39 40-49 50-59 Lane Common marker (2\*24) Unique markers (2\*24) Pad (3\*64+68 bits) Next 257-bit block 3 **Bases for 100 GbE** 5 **PCS**

- 50 GbE can be based on 1x257b blocks, pad is filled with free running PRBS9

- 100 GbE can be based on 2x257b blocks, pad is filled with free running PRBS9

- To provide backward compatibility with 100 GbE per CL82 require more complex PMA-PMA chip

- Implementation will support 50GAUI-2/1 and CAUI-4/2

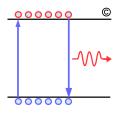

#### Option IIA: 50 GbE and NG 100GbE Based on 5G PCS Lane Per CL82 with 100GbE having 20 PCS lanes

- For 50 GbE use half number of PCS lanes as was proposed:

- http://www.ieee802.org/3/50G/public/adhoc/archive/gustlin\_020316\_50GE\_NGOATH\_adhoc.pdf

- May support 25 GbE MSA implementation with simpler PMA chip

- Implementation will support 50GAUI-2/1 and CAUI-4/2

- If RS-FEC (544,514) is required is there value to preserve 5G PCS lane over synergy with .bs PCS?

Bases for 50

A. Ghiasi

IEEE 802.3 NGOATH Study Group

4

Option IIB: Leverage CL82 PCS for 50 GbE with 4 PCS lanes and NG 100GbE Based on 20 PCS Lanes

Based on CL82 100 GbE lanes and 50 GbE based on speed up version of 40 GbE 10G PCS lane

Table 82–3—40GBASE-R Alignment marker encodings

| PCS lane<br>number | Encoding <sup>a</sup><br>{M <sub>0</sub> , M <sub>1</sub> , M <sub>2</sub> , BIP <sub>3</sub> , M <sub>4</sub> , M <sub>5</sub> , M <sub>6</sub> , BIP <sub>7</sub> } |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                  | $0x90, 0x76, 0x47, BIP_3, 0x6F, 0x89, 0xB8, BIP_7$                                                                                                                    |

| 1                  | 0xF0, 0xC4, 0xE6, BIP <sub>3</sub> , 0x0F, 0x3B, 0x19, BIP <sub>7</sub>                                                                                               |

| 2                  | 0xC5, 0x65, 0x9B, BIP <sub>3</sub> , 0x3A, 0x9A, 0x64, BIP <sub>7</sub>                                                                                               |

| 3                  | 0xA2, 0x79, 0x3D, BIP <sub>3</sub> , 0x5D, 0x86, 0xC2, BIP <sub>7</sub>                                                                                               |

<sup>&</sup>lt;sup>a</sup>Each octet is transmitted LSB to MSB.

- 50 GbE based on CL82 speed up 10G (12.5G) PCS lanes and could be made compatible with the 25 GbE MSA implementation of 50 GbE based on two lanes

- Implementation will support 50GAUI-2/1

- PMD under consideration should determine if KR4 FEC is sufficient otherwise KP4 FEC

- Options for forming the FEC lanes

- If KR4 FEC sufficient then FEC lanes could be formed by bit/symbol mux of 2 lanes 50 GbE MSA

- If KP4 FEC is necessary then FEC gets bolted on top of 2 lanes 50 GbE MSA PCS bit/symbol mux to be determined based on FEC study.

### Option III: Possible 50 and 100 GbE PCS Format

#### Follow CL49 10GBase-R PCS without any AM

- No clear advantage

- No synergy with 100GbE, 200GbE, 400 GbE

- Will only support CAUI-1 where there is no PMD objective for it

- Will not support LAUI-2

#### CL49 does not offer viable PCS solution!

### **Application Overlay**

A key consideration of the 50 GbE and NG 100 GbE is application overlay with 200 GbE/400 GbE in support of break out from common port

- Supporting both 50GAUI-2/1 is required for 50 GbE application overlay

- CAUI-4 already exist

- 25G/lane early implementation as well as providing transition for 50 GbE MSA and 100 GbE.

\* In some implementation FEC may be part of the PMA-PMA otherwise in the super-set host.

A. Ghiasi

IEEE 802.3 NGOATH Study Group

# Example NIC/NPU with No Immediate Benefit from 50G I/O

#### 50G I/O does not offer benefit in low port count applications

- Limited availability of 50G SerDes can be costly and/or not available

- The ASIC may already have 50 GbE based on two lanes MSA

- Not having the option of 50GAUI-2 may force a new ASIC development with costly 50G SerDes

- The standard should offer flexibility and choice to either use 50GAUI-2 or 50GAUI-1.

http://www.ieee802.org/3/50G/public/Mar16/booth\_50GE\_NGOATH\_01a\_0316.pdf

## Why 50GAUI-2 Is Needed

25 GbE 1<sup>st</sup> task force meeting was Jan 2015 where products (switches, NIC, Phys, CFP2, CFP4, and QSFP28) already available in the market place based on 25G/lane

- 25GbE was based on the definition of the 25G MSA which happened to leverage CL49 instead of the MLD PCS

- Today the maturity of the 50G/lane IO is not at the same level as 25G IO was 2014/2015 time frame

- Following class of product do not benefit from migration to 50G/ lane IO

- Core limited

- NIC/NPU applications with just a few ports

- Unless application can benefit from 50G not having the option of the 50GAUI-2 forces the eco-system to higher risk and cost 50G IO over commodity 25G IO!

### **Summary**

#### PCS/FEC options for 50 GbE

- Clean sheet of paper based on 25G PCS lane is forward compatible with 400 GbE

- Speed up CL82 with 4 PCS lanes (12.5G) offers backward compatible 50 GbE MSA

- Either of the above options supports 50GAUI-2/50GAUI-1

- Both RS-FEC(528,514) and (544,514) need to be further studied in conjunction with baseline PMDs under consideration

#### **PCS/FEC** options for NG 100 GbE

- Ease of full backward compatibility should not come at expense of sacrificing NG 100 GbE PMD performance as the backward compatibility can always be solved with the PMA-PMA device

- Clean sheet of paper assumes 25G PCS lane forward compatible with 400 GbE

- Use CL82 100GbE PCS base on 5G PCS lane offering backward compatibility

- Either of the above options supports CAUI-4/CAUI-2

- Both RS-FEC(528,514) and (544,514) need to be further studied in conjunction with baseline PMDs under consideration

With 50 GbE MSA and 100 GbE already existing in the market place ease of backward compatibility offers greater value than forward compatibility to 400 GbE.