#### **Challenges in Designing 10 GB/S Backplanes**

IEEE 802.3ae Task Force JULY, 2000 San Diego, Ca JIM\_TAVACOLI@ACCELERANT.NET

IEEE 802.3ae Task Force

JULY, 2000 PAGE 1

### Share information on design issues in 10 GB/S backplane interconnects

#### Make recommendations

### Provide an implementation perspective

IEEE 802.3ae Task Force

## **Parameters**

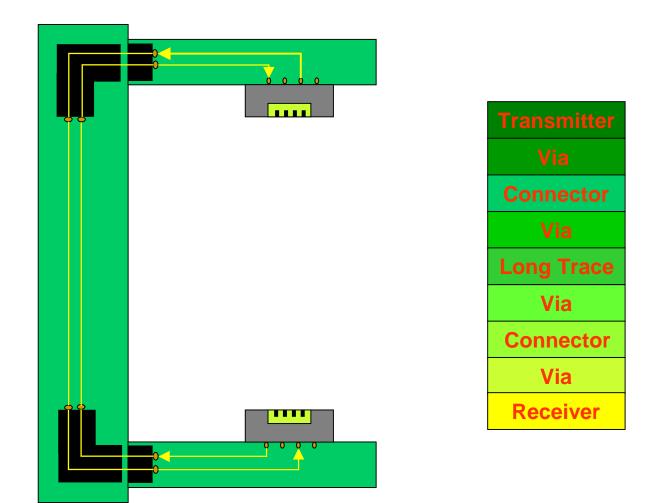

- Aggregate Reflection due to Vias, Connectors, Terminations

- Crosstalk

- Due to vias, Connectors

- Capacitive and inductive mismatches between differential signals

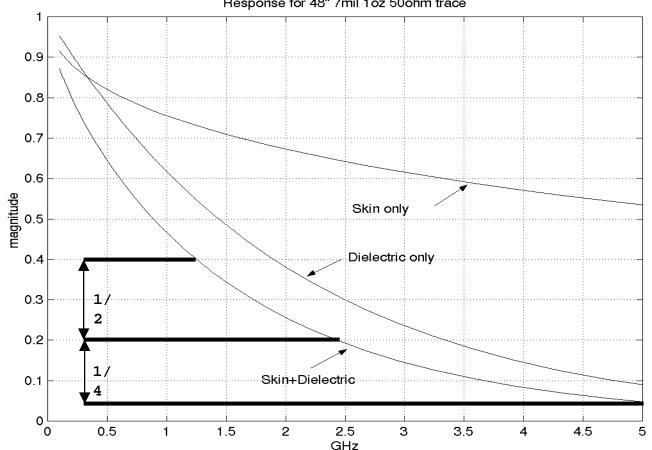

- High Frequency Loss

- Differential trace impedance

- Loss may be a good thing (when alleviating short run reflections)

- EMI

- Trace configuration will not stop radiation

- Density

- How close can the traces be packed determines cost, aggregate bandwidth

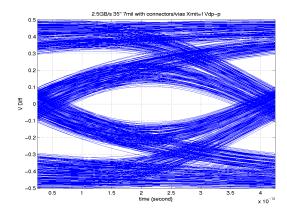

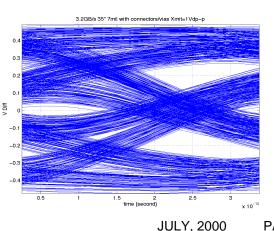

## Problem

- As symbol rates increase,

- Amplitude decreases, crosstalk increases

- Better PCB material solve one problem, create another

- Variations in dispersion cause a myriad of channel conditions

- How to define, identify and compensate for weakest link

IEEE 802.3ae Task Force

PAGE 5

## From 1.25GB/S to 5GB/S

Response for 48" 7mil 1 oz 50 ohm trace

IEEE 802.3ae Task Force

JULY, 2000 PAGE 6

# **Possible Solutions**

- New strategies for system design offer incremental improvements

- Utilize new PCB material, connectors

- Challenge the via culprit

- Optimize trace structures

#### • New 2.5G or 3.125G SERDES

- Offering pre-emphasis, post-emphasis

- Effectiveness in backplanes remains to be seen

- SERDES are getting better than ever

#### Optical backplanes

- Flexible, high performance but

- Cost issues are limiting deployment

## Recommendation

- View Backplane channel as a communication system

- Exploit the transmission media with targeted solutions

- Robust backplane design requires a targeted solution

- Lower line rate and increase # bits per symbol

- Reduce number of pins per GB/S

- Reduce signal integrity problems

- Increase reach

# **A Targeted Solution**

- A targeted backplane transceiver should:

- Optimize for performance & density within any backplane construct

- Work on standard FR4 PCB material and connectors

- Adapt to most existing serial backplanes

- Alleviate Signal integrity problems: Crosstalk, Reflections, Dispersion

- Complement enhancements made to PCB, vias & connectors

# **Problems and Solutions**

- Reflection

- Crosstalk

- Dispersion

- EMI

- Density

- Adaptive equalization

- Adaptive transmit levels

- Lower line rate

- Scrambler

- Adaptive transmit levels