# 45. Management Data Input/Output (MDIO) Interface

#### 45.1 Overview

This clause defines the logical and electrical characteristics of an extension to the two signal Management Data Input/Output (MDIO) Interface specified in Clause 22.

The purpose of this extension is to provide the ability to access more device registers while still retaining logical compatibility with the MDIO interface defined in Clause 22. Clause 22 specifies the MDIO frame format and uses an ST code of 01 to access registers. In this clause, additional registers are added to the address space by defining MDIO frames that use an ST code of 00.

This extension to the MDIO interface is applicable to Ethernet implementations that operate at speeds of 10 Gb/s and above.

The MDIO electrical interface is optional. Where no physical embodiment of the MDIO exists, provision of an equivalent mechanism to access the registers is recommended.

Throughout this clause, an "a.b.c" format is used to identify register bits, where "a" is the device address, "b" is the register address, and "c" is the bit number within the register.

# 45.1.1 Summary of major concepts

The following are major concepts of the MDIO Interface:

- a) Preserve the management frame structure defined in 22.2.4.5.

- b) Define a mechanism to address more registers than specified in 22.2.4.5.

- c) Define ST and OP codes to identify and control the extended access functions.

- d) Provide an electrical interface specification that is compatible with common digital CMOS ASIC processes.

#### 45.1.2 Application

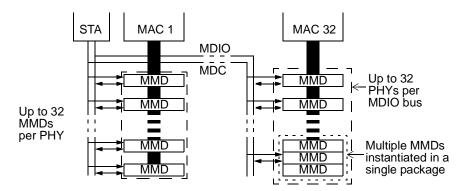

This clause defines a management interface between Station Management (STA) and the sublayers that form a 10 Gb/s Physical Layer device (PHY) entity. Where a sublayer, or grouping of sublayers, is an individually manageable entity, it is known as an MDIO Manageable Device (MMD). This clause allows a single STA, through a single MDIO interface, to access up to 32 PHYs (defined as PRTAD in the frame format defined in 45.3) consisting of up to 32 MMDs as shown in Figure 45–1. The MDIO interface can support up to a maximum of 65 536 registers in each MMD.

page 1 / 88

Figure 45–1—DTE and MMD devices

# **45.2 MDIO Interface Registers**

The management interface specified in Clause 22 provides a simple, two signal, serial interface to connect a Station Management entity and a managed PHY for providing access to management parameters and services. The interface is referred to as the MII management interface.

The MDIO interface is based on the MII management interface, but differs from it in several ways. The MDIO interface uses indirect addressing to create an extended address space allowing a much larger number of registers to be accessed within each MMD. The MDIO address space is orthogonal to the MII management interface address space. The mechanism for the addressing is defined in 45.3. The MDIO electrical interface operates at lower voltages than those specified for the MII management interface. The electrical interface is specified in 45.4. For cases where a single entity combines Clause 45 MMDs with Clause 22 registers, then the Clause 22 registers may be accessed using the Clause 45 electrical interface and the Clause 22 management frame structure. The list of possible MMDs is shown in Table 45–1. The PHY XS and DTE XS devices are the two partner devices used to extend the interface that sits immediately below the Reconciliation Sublayer. For 10 Gigabit Ethernet, the interface extenders are defined as the XGXS devices.

If a device supports the MDIO interface it shall respond to all possible register addresses for the device and return a value of zero for undefined and unsupported registers. Writes to undefined registers and read-only registers shall have no effect. The operation of an MMD shall not be affected by writes to reserved and unsupported register bits, and such register bits shall return a value of zero when read.

To ensure compatibility with future use of reserved bits and registers, the Management Entity should write to reserved bits with a value of zero and ignore reserved bits on read.

Some of the bits within MMD registers are defined as latching low (LL) or latching high (LH). When a bit is defined as latching low and the condition for the bit to be low has occurred, the bit shall remain low until after it has been read via the management interface. Once such a read has occurred, the bit shall assume a value based on the current state of the condition it monitors. When a bit is defined as latching high and the condition for the bit to be high has occurred, the bit shall remain high until after it has been read via the management interface. Once such a read has occurred, the bit shall assume a value based on the current state of the condition it monitors.

page 2 / 88

Table 45-1-MDIO Manageable Device addresses

| Device address | MMD name          |

|----------------|-------------------|

| 0              | Reserved          |

| 1              | PMA/PMD           |

| 2              | WIS               |

| 3              | PCS               |

| 4              | PHY XS            |

| 5              | DTE XS            |

| 6 through 29   | Reserved          |

| 30             | Vendor specific 1 |

| 31             | Vendor specific 2 |

For multi-bit fields, the lowest numbered bit of the field in the register corresponds to the least significant bit of the field.

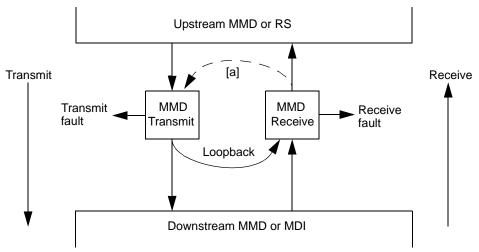

Figure 45–2 describes the signal terminology used for the MMDs.

Figure 45-2—MMD signal terminology

[a] Direction of the optional PHY XS loopback

# 45.2.1 PMA/PMD registers

The assignment of registers in the PMA/PMD is shown in Table 45–2.

Table 45-2—PMA/PMD registers

| Register address          | Register name                 |

|---------------------------|-------------------------------|

| 1.0                       | PMA/PMD control 1             |

| 1.1                       | PMA/PMD status 1              |

| 1.2, 1.3                  | PMA/PMD device identifier     |

| 1.4                       | PMA/PMD speed ability         |

| 1.5, 1.6                  | PMA/PMD devices in package    |

| 1.7                       | 10G PMA/PMD control 2         |

| 1.8                       | 10G PMA/PMD status 2          |

| 1.9                       | 10G PMD transmit disable      |

| 1.10                      | 10G PMD receive signal detect |

| 1.11 through 1.13         | Reserved                      |

| 1.14, 1.15                | PMA/PMD package identifier    |

| 1.16 through 1.32 767     | Reserved                      |

| 1.32 768 through 1.65 535 | Vendor specific               |

#### 45.2.1.1 PMA/PMD control 1 register (Register 1.0)

The assignment of bits in the PMA/PMD control 1 register is shown in Table 45–3. The default value for each bit of the PMA/PMD control 1 register has been chosen so that the initial state of the device upon power up or completion of reset is a normal operational state without management intervention.

Table 45–3—PMA/PMD control 1 register bit definitions

| Bit(s)   | Name            | Description                                                                                                          | R/W <sup>a</sup> |

|----------|-----------------|----------------------------------------------------------------------------------------------------------------------|------------------|

| 1.0.15   | Reset           | 1 = PMA/PMD reset<br>0 = Normal operation                                                                            | R/W<br>SC        |

| 1.0.14   | Reserved        | Value always 0, writes ignored                                                                                       | R/W              |

| 1.0.13   | Speed selection | 1 = Operation at 10 Gb/s and above<br>0 = Unspecified                                                                | R/W              |

| 1.0.12   | Reserved        | Value always 0, writes ignored                                                                                       | R/W              |

| 1.0.11   | Low power       | 1 = Low-power mode<br>0 = Normal operation                                                                           | R/W              |

| 1.0.10:7 | Reserved        | Value always 0, writes ignored                                                                                       | R/W              |

| 1.0.6    | Speed selection | 1 = Operation at 10 Gb/s and above<br>0 = Unspecified                                                                | R/W              |

| 1.0.5:2  | Speed selection | 5 4 3 2<br>1 x x x = Reserved<br>x 1 x x = Reserved<br>x x 1 x = Reserved<br>0 0 0 1 = Reserved<br>0 0 0 0 = 10 Gb/s | R/W              |

| 1.0.1    | Reserved        | Value always 0, writes ignored                                                                                       | R/W              |

| 1.0.0    | PMA loopback    | 1 = Enable PMA Loopback mode<br>0 = Disable PMA Loopback mode                                                        | R/W              |

<sup>&</sup>lt;sup>a</sup>R/W = Read/Write, SC = Self Clearing

#### 45.2.1.1.1 Reset (1.0.15)

Resetting a PMA/PMD is accomplished by setting bit 1.0.15 to a one. This action shall set all PMA/PMD registers to their default states. As a consequence, this action may change the internal state of the PMA/PMD and the state of the physical link. This action may also initiate a reset in any other MMDs that are instantiated in the same package. This bit is self-clearing, and a PMA/PMD shall return a value of one in bit 1.0.15 when a reset is in progress; otherwise, it shall return a value of zero. A PMA/PMD is not required to accept a write transaction to any of its registers until the reset process is completed. The control and management interface shall be restored to operation within 0.5 s from the setting of bit 1.0.15. During a reset, a PMD/PMA shall respond to reads from register bits 1.0.15 and 1.8.15:14. All other register bits should be ignored.

NOTE—This operation may interrupt data communication. The data path of a PMD, depending on type and temperature, may take many seconds to run at optimum error rate after exiting from reset or low-power mode.

low-power mode. The default value of bit 1.0.11 is zero.

1 2

8 9 10

11

16

17 18 19

20

21

22 23 24

25 26

27 28

30 31 32

29

41

42

43 44 45

46 47 48

53 54

7

may take many seconds to run at optimum error rate after exiting from reset or low-power mode. 45.2.1.1.3 Speed selection (1.0.13,1.0.6, 1.0.5:2)

45.2.1.1.2 Low power (1.0.11)

Speed selection bits 1.0.13 and 1.0.6 shall both be written as a one. Any attempt to change the bits to an invalid setting shall be ignored. These two bits are set to one in order to make them compatible with Clause 22.

A PMA/PMD may be placed into a low-power mode by setting bit 1.0.11 to a one. This action may also ini-

tiate a low-power mode in any other MMDs that are instantiated in the same package. The low-power mode is exited by resetting the PMA/PMD. The behavior of the PMA/PMD in transition to and from the low-

power mode is implementation specific and any interface signals should not be relied upon. While in the

low-power mode, the device shall, as a minimum, respond to management transactions necessary to exit the

NOTE—This operation will interrupt data communication. The data path of a PMD, depending on type and temperature,

The speed of the PMA/PMD may be selected using bits 5 through 2. The speed abilities of the PMA/PMD are advertised in the PMA/PMD speed ability register. A PMA/PMD may ignore writes to the PMA/PMD speed selection bits that select speeds it has not advertised in the PMA/PMD speed ability register. It is the responsibility of the STA entity to ensure that mutually acceptable speeds are applied consistently across all the MMDs on a particular PHY.

The PMA/PMD speed selection defaults to a supported ability.

#### 45.2.1.1.4 PMA loopback (1.0.0)

The PMA shall be placed in a Loopback mode of operation when bit 1.0.0 is set to a one. When bit 1.0.0 is set to a one, the PMA shall accept data on the transmit path and return it on the receive path.

The loopback function is mandatory for the 10GBASE-X port type and optional for all other port types. A device's ability to perform the loopback function is advertised in the loopback ability bit of the related speed-dependent status register. A PMA that is unable to perform the loopback function shall ignore writes to this bit and shall return a value of zero when read. For 10 Gb/s operation, the loopback functionality is detailed in 48.3.3 and 51.8, and the loopback ability bit is specified in the 10G PMA/PMD status 2 register.

The default value of bit 1.0.0 is zero.

NOTE—The signal path through the PMA that is exercised in the Loopback mode of operation is implementation specific, but it is recommended that the signal path encompass as much of the PMA circuitry as is practical. The intention of providing this Loopback mode of operation is to permit a diagnostic or self-test function to perform the transmission and reception of a PDU, thus testing the transmit and receive data paths. Other loopback signal paths may be enabled using loopback controls within other MMDs.

I

#### 45.2.1.2 PMA/PMD status 1 register (Register 1.1)

The assignment of bits in the status 1 register is shown in Table 45–4. All the bits in the status 1 register are read only; therefore, a write to the status 1 register shall have no effect.

Table 45-4—PMA/PMD status 1 register bit definitions

| Bit(s)   | Name                | Description                                                                        | R/W <sup>a</sup> |

|----------|---------------------|------------------------------------------------------------------------------------|------------------|

| 1.1.15:8 | Reserved            | Ignore when read                                                                   | RO               |

| 1.1.7    | Fault               | 1 = Fault condition detected<br>0 = Fault condition not detected                   | RO               |

| 1.1.6:3  | Reserved            | Ignore when read                                                                   | RO               |

| 1.1.2    | Receive link status | 1 = PMA/PMD receive link up<br>0 = PMA/PMD receive link down                       | RO/LL            |

| 1.1.1    | Low-power ability   | 1 = PMA/PMD supports low-power mode<br>0 = PMA/PMD does not support low-power mode | RO               |

| 1.1.0    | Reserved            | Ignore when read                                                                   | RO               |

<sup>&</sup>lt;sup>a</sup>RO = Read Only, LL = Latching Low

### 45.2.1.2.1 Fault (1.1.7)

Fault is a global PMA/PMD variable. When read as a one, bit 1.1.7 indicates that either (or both) the PMA or the PMD has detected a fault condition on either the transmit or receive paths. When read as a zero, bit 1.1.7 indicates that neither the PMA nor the PMD has detected a fault condition. For 10 Gb/s operation, bit 1.1.7 is set to a one when either of the fault bits (1.8.11, 1.8.10) located in register 1.8 are set to a one.

#### 45.2.1.2.2 Receive link status (1.1.2)

When read as a one, bit 1.1.2 indicates that the PMA/PMD receive link is up. When read as a zero, bit 1.1.2 indicates that the PMA/PMD receive link is down. The receive link status bit shall be implemented with latching low behavior.

#### 45.2.1.2.3 Low-power ability (1.1.1)

When read as a one, bit 1.1.1 indicates that the PMA/PMD supports the low-power feature. When read as a zero, bit 1.1.1 indicates that the PMA/PMD does not support the low-power feature. If a PMA/PMD supports the low-power feature, then it is controlled using the low-power bit 1.0.11.

#### 45.2.1.3 PMA/PMD device identifier (Registers 1.2 and 1.3)

Registers 1.2 and 1.3 provide a 32-bit value, which may constitute a unique identifier for a particular type of PMA/PMD. The identifier shall be composed of the 3rd through 24th bits of the Organizationally Unique Identifier (OUI) assigned to the device manufacturer by the IEEE, plus a six-bit model number, plus a four-bit revision number. A PMA/PMD may return a value of zero in each of the 32 bits of the PMA/PMD device identifier.

I

The format of the PMA/PMD device identifier is specified in 22.2.4.3.1.

# 45.2.1.4 PMA/PMD speed ability (Register 1.4)

The assignment of bits in the PMA/PMD speed ability register is shown in Table 45–5.

Table 45-5—PMA/PMD speed ability register bit definitions

| Bit(s)   | Name                       | Description                                                                                          | R/W <sup>a</sup> |

|----------|----------------------------|------------------------------------------------------------------------------------------------------|------------------|

| 1.4.15:1 | Reserved for future speeds | Value always 0, writes ignored                                                                       | RO               |

| 1.4.0    | 10G capable                | 1 = PMA/PMD is capable of operating at 10 Gb/s<br>0 = PMA/PMD is not capable of operating at 10 Gb/s | RO               |

$<sup>^{</sup>a}RO = Read Only$

# 45.2.1.4.1 10G capable (1.4.0)

When read as a one, bit 1.4.0 indicates that the PMA/PMD is able to operate at a data rate of 10 Gb/s. When read as a zero, bit 1.4.0 indicates that the PMA/PMD is not able to operate at a data rate of 10 Gb/s.

#### 45.2.1.5 PMA/PMD devices in package (Registers 1.5 and 1.6)

The assignment of bits in the PMA/PMD devices in package registers is shown in Table 45-6.

When read as a one, a bit in the PMA/PMD devices in package registers indicates that the associated MMD has been instantiated within the same package as other MMDs whose associated bits have been set to a one within the PMA/PMD devices in package registers. Bit 1.5.0 is used to indicate that Clause 22 functionality has been implemented within a Clause 45 electrical interface device. The definition of the term package is vendor specific and could be a chip, module, or other similar entity.

#### 45.2.1.6 10G PMA/PMD control 2 register (Register 1.7)

The assignment of bits in the 10G PMA/PMD control 2 register is shown in Table 45–7.

# 45.2.1.6.1 PMA/PMD type selection (1.7.3:0)

The PMA/PMD type of the 10G PMA/PMD shall be selected using bits 3 through 0. The PMA/PMD type abilities of the 10G PMA/PMD are advertised in bits 7 through 0 of the 10G PMA/PMD status 2 register. A 10G PMA/PMD shall ignore writes to the PMA/PMD type selection bits that select PMA/PMD types it has not advertised in the status register. It is the responsibility of the STA entity to ensure that mutually acceptable MMD types are applied consistently across all the MMDs on a particular PHY.

The PMA/PMD type selection defaults to a supported ability.

Table 45-6— PMA/PMD devices in package registers bit definitions

| Bit(s)   | Name                             | Description                                                                                            | R/W <sup>a</sup> |

|----------|----------------------------------|--------------------------------------------------------------------------------------------------------|------------------|

| 1.6.15   | Vendor specific device 2 present | 1 = Vendor specific device 2 present in package<br>0 = Vendor specific device 2 not present in package | RO               |

| 1.6.14   | Vendor specific device 1 present | 1 = Vendor specific device 1 present in package<br>0 = Vendor specific device 1 not present in package | RO               |

| 1.6.13:0 | Reserved                         | Ignore on read                                                                                         | RO               |

| 1.5.15:6 | Reserved                         | Ignore on read                                                                                         | RO               |

| 1.5.5    | DTE XS present                   | 1 = DTE XS present in package<br>0 = DTE XS not present in package                                     | RO               |

| 1.5.4    | PHY XS present                   | 1 = PHY XS present in package<br>0 = PHY XS not present in package                                     | RO               |

| 1.5.3    | PCS present                      | 1 = PCS present in package<br>0 = PCS not present in package                                           | RO               |

| 1.5.2    | WIS present                      | 1 = WIS present in package<br>0 = WIS not present in package                                           | RO               |

| 1.5.1    | PMD/PMA present                  | 1 = PMA/PMD present in package<br>0 = PMA/PMD not present in package                                   | RO               |

| 1.5.0    | Clause 22 registers present      | 1 = Clause 22 registers present in package<br>0 = Clause 22 registers not present in package           | RO               |

<sup>a</sup>RO = Read Only

Table 45-7—10G PMA/PMD control 2 register bit definitions

| Bit(s)   | Name                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W <sup>a</sup> |

|----------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 1.7.15:4 | Reserved               | Value always 0, writes ignored                                                                                                                                                                                                                                                                                                                                                                                                               | R/W              |

| 1.7.3:0  | PMA/PMD type selection | 3 2 1 0 1 1 1 x = Reserved 1 1 0 1 = Reserved 1 1 0 0 = 10GBASE-CX4 PMA/PMD type 1 0 x x = Reserved 0 1 1 1 = 10GBASE-SR PMA/PMD type 0 1 1 0 = 10GBASE-LR PMA/PMD type 0 1 0 1 = 10GBASE-ER PMA/PMD type 0 1 0 0 = 10GBASE-LX4 PMA/PMD type 0 1 0 0 = 10GBASE-LX4 PMA/PMD type 0 0 1 1 = 10GBASE-SW PMA/PMD type 0 0 1 0 = 10GBASE-LW PMA/PMD type 0 0 1 0 = 10GBASE-LW PMA/PMD type 0 0 0 1 = 10GBASE-EW PMA/PMD type 0 0 0 0 0 = Reserved | R/W              |

<sup>a</sup>R/W = Read/Write

I

# 45.2.1.7 10G PMA/PMD status 2 register (Register 1.8)

The assignment of bits in the 10G PMA/PMD status 2 register is shown in Table 45–8. All the bits in the 10G PMA/PMD status 2 register are read only; a write to the 10G PMA/PMD status 2 register shall have no effect.

Table 45–8—10G PMA/PMD status 2 register bit definitions

| Bit(s)    | Name                         | Description                                                                                                                                                                    | R/W <sup>a</sup> |

|-----------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 1.8.15:14 | Device present               | 15 14 1 0 = Device responding at this address 1 1 = No device responding at this address 0 1 = No device responding at this address 0 0 = No device responding at this address | RO               |

| 1.8.13    | Transmit fault ability       | 1 = PMA/PMD has the ability to detect a fault condition on the transmit path 0 = PMA/PMD does not have the ability to detect a fault condition on the transmit path            | RO               |

| 1.8.12    | Receive fault ability        | 1 = PMA/PMD has the ability to detect a fault condition on the receive path 0 = PMA/PMD does not have the ability to detect a fault condition on the receive path              | RO               |

| 1.8.11    | Transmit fault               | 1 = Fault condition on transmit path<br>0 = No fault condition on transmit path                                                                                                | RO/LH            |

| 1.8.10    | Receive fault                | 1 = Fault condition on receive path<br>0 = No fault condition on receive path                                                                                                  | RO/LH            |

| 1.8.9     | 10GBASE-CX4 ability          | 1 = PMA/PMD is able to perform 10GBASE-CX4<br>0 = PMA/PMD is not able to perform 10GBASE-CX4                                                                                   | RO               |

| 1.8.8     | PMD transmit disable ability | 1 = PMD has the ability to disable the transmit path<br>0 = PMD does not have the ability to disable the transmit<br>path                                                      | RO               |

| 1.8.7     | 10GBASE-SR ability           | 1 = PMA/PMD is able to perform 10GBASE-SR<br>0 = PMA/PMD is not able to perform 10GBASE-SR                                                                                     | RO               |

| 1.8.6     | 10GBASE-LR ability           | 1 = PMA/PMD is able to perform 10GBASE-LR<br>0 = PMA/PMD is not able to perform 10GBASE-LR                                                                                     | RO               |

| 1.8.5     | 10GBASE-ER ability           | 1 = PMA/PMD is able to perform 10GBASE-ER<br>0 = PMA/PMD is not able to perform 10GBASE-ER                                                                                     | RO               |

| 1.8.4     | 10GBASE-LX4 ability          | 1 = PMA/PMD is able to perform 10GBASE-LX4<br>0 = PMA/PMD is not able to perform 10GBASE-LX4                                                                                   | RO               |

| 1.8.3     | 10GBASE-SW ability           | 1 = PMA/PMD is able to perform 10GBASE-SW<br>0 = PMA/PMD is not able to perform 10GBASE-SW                                                                                     | RO               |

| 1.8.2     | 10GBASE-LW ability           | 1 = PMA/PMD is able to perform 10GBASE-LW<br>0 = PMA/PMD is not able to perform 10GBASE-LW                                                                                     | RO               |

Table 45–8—10G PMA/PMD status 2 register bit definitions (continued)

| Bit(s) | Name                 | Description                                                                                                             | R/W <sup>a</sup> |

|--------|----------------------|-------------------------------------------------------------------------------------------------------------------------|------------------|

| 1.8.1  | 10GBASE-EW ability   | 1 = PMA/PMD is able to perform 10GBASE-EW<br>0 = PMA/PMD is not able to perform 10GBASE-EW                              | RO               |

| 1.8.0  | PMA loopback ability | 1 = PMA has the ability to perform a loopback function 0 = PMA does not have the ability to perform a loopback function | RO               |

<sup>a</sup>RO = Read Only, LH = Latching High

# 45.2.1.7.1 Device present (1.8.15:14)

When read as <10>, bits 1.8.15:14 indicate that a device is present and responding at this register address. When read as anything other than <10>, bits 1.8.15:14 indicate that no device is present at this register address or that the device is not functioning properly.

# 45.2.1.7.2 Transmit fault ability (1.8.13)

When read as a one, bit 1.8.13 indicates that the PMA/PMD has the ability to detect a fault condition on the transmit path. When read as a zero, bit 1.8.13 indicates that the PMA/PMD does not have the ability to detect a fault condition on the transmit path.

# 45.2.1.7.3 Receive fault ability (1.8.12)

When read as a one, bit 1.8.12 indicates that the PMA/PMD has the ability to detect a fault condition on the receive path. When read as a zero, bit 1.8.12 indicates that the PMA/PMD does not have the ability to detect a fault condition on the receive path.

#### 45.2.1.7.4 Transmit fault (1.8.11)

When read as a one, bit 1.8.11 indicates that the PMA/PMD has detected a fault condition on the transmit path. When read as a zero, bit 1.8.11 indicates that the PMA/PMD has not detected a fault condition on the transmit path. Detection of a fault condition on the transmit path is optional and the ability to detect such a condition is advertised by bit 1.8.13. A PMA/PMD that is unable to detect a fault condition on the transmit path shall return a value of zero for this bit. The description of the transmit fault function for serial PMDs is given in 52.4.8. The description of the transmit fault function for WWDM PMDs is given in 53.4.10. The transmit fault bit shall be implemented with latching high behavior.

The default value of bit 1.8.11 is zero.

# 45.2.1.7.5 Receive fault (1.8.10)

When read as a one, bit 1.8.10 indicates that the PMA/PMD has detected a fault condition on the receive path. When read as a zero, bit 1.8.10 indicates that the PMA/PMD has not detected a fault condition on the receive path. Detection of a fault condition on the receive path is optional and the ability to detect such a condition is advertised by bit 1.8.12. A PMA/PMD that is unable to detect a fault condition on the receive path shall return a value of zero for this bit. The description of the receive fault function for serial PMDs is given in 52.4.9. The description of the receive fault function for WWDM PMDs is given in 53.4.11. The receive fault bit shall be implemented with latching high behavior.

The default value of bit 1.8.10 is zero.

6

7 8

9 10

11 12

13 14 15

16 17 18

19 20

21 22

23 24 25

> 26 27

> > 28 29 30

31 32

33 34 35

36 37 38

39

40 41 42

43 44 45

46 47 48

49

50

51

52 53 54

# 45.2.1.7.6 10GBASE-CX4 ability (1.8.9)

When read as a one, bit 1.8.4 indicates that the PMA/PMD is able to support a 10GBASE-CX4 PMA/PMD type. When read as a zero, bit 1.8.4 indicates that the PMA/PMD is not able to support a 10GBASE-CX4 PMA/PMD type.

# 45.2.1.7.7 PMD transmit disable ability (1.8.8)

When read as a one, bit 1.8.8 indicates that the PMD is able to perform the transmit disable function. When read as a zero, bit 1.8.8 indicates that the PMD is not able to perform the transmit disable function. If a PMD is able to perform the transmit disable function, then it is controlled using the PMD transmit disable register.

# 45.2.1.7.8 10GBASE-SR ability (1.8.7)

When read as a one, bit 1.8.7 indicates that the PMA/PMD is able to support a 10GBASE-SR PMA/PMD type. When read as a zero, bit 1.8.7 indicates that the PMA/PMD is not able to support a 10GBASE-SR PMA/PMD type.

## 45.2.1.7.9 10GBASE-LR ability (1.8.6)

When read as a one, bit 1.8.6 indicates that the PMA/PMD is able to support a 10GBASE-LR PMA/PMD type. When read as a zero, bit 1.8.6 indicates that the PMA/PMD is not able to support a 10GBASE-LR PMA/PMD type.

# 45.2.1.7.10 10GBASE-ER ability (1.8.5)

When read as a one, bit 1.8.5 indicates that the PMA/PMD is able to support a 10GBASE-ER PMA/PMD type. When read as a zero, bit 1.8.5 indicates that the PMA/PMD is not able to support a 10GBASE-ER PMA/PMD type.

# 45.2.1.7.11 10GBASE-LX4 ability (1.8.4)

When read as a one, bit 1.8.4 indicates that the PMA/PMD is able to support a 10GBASE-LX4 PMA/PMD type. When read as a zero, bit 1.8.4 indicates that the PMA/PMD is not able to support a 10GBASE-LX4 PMA/PMD type.

# 45.2.1.7.12 10GBASE-SW ability (1.8.3)

When read as a one, bit 1.8.3 indicates that the PMA/PMD is able to support a 10GBASE-SW PMA/PMD type. When read as a zero, bit 1.8.3 indicates that the PMA/PMD is not able to support a 10GBASE-SW PMA/PMD type.

### 45.2.1.7.13 10GBASE-LW ability (1.8.2)

When read as a one, bit 1.8.2 indicates that the PMA/PMD is able to support a 10GBASE-LW PMA/PMD type. When read as a zero, bit 1.8.2 indicates that the PMA/PMD is not able to support a 10GBASE-LW PMA/PMD type.

# 45.2.1.7.14 10GBASE-EW ability (1.8.1)

When read as a one, bit 1.8.1 indicates that the PMA/PMD is able to support a 10GBASE-EW PMA/PMD type. When read as a zero, bit 1.8.1 indicates that the PMA/PMD is not able to support a 10GBASE-EW PMA/PMD type.

# 45.2.1.7.15 PMA loopback ability (1.8.0)

When read as a one, bit 1.8.0 indicates that the PMA is able to perform the loopback function. When read as a zero, bit 1.8.0 indicates that the PMA is not able to perform the loopback function. If a PMA is able to perform the loopback function, then it is controlled using the PMA loopback bit 1.0.0.

#### 45.2.1.8 10G PMD transmit disable register (Register 1.9)

The assignment of bits in the 10G PMD transmit disable register is shown in Table 45–9. The transmit disable functionality is optional and a PMD's ability to perform the transmit disable functionality is advertised in the PMD transmit disable ability bit 1.8.8. A PMD that does not implement the transmit disable functionality shall ignore writes to the 10G PMD transmit disable register and may return a value of zero for all bits. A PMD device that operates using a single wavelength and has implemented the transmit disable function shall use bit 1.9.0 to control the function. Such devices shall ignore writes to bits 1.9.4:1 and return a value of zero for those bits when they are read. The transmit disable function for serial PMDs is described in 52.4.7. The transmit disable function for wide wavelength division multiplexing (WWDM) PMDs is described in 53.4.7.

Table 45-9—10G PMD transmit disable register bit definitions

| Bit(s)   | Name                        | Description                                                                   | R/W <sup>a</sup> |

|----------|-----------------------------|-------------------------------------------------------------------------------|------------------|

| 1.9.15:5 | Reserved                    | Value always 0, writes ignored                                                | R/W              |

| 1.9.4    | PMD transmit disable 3      | 1 = Disable output on transmit lane 3<br>0 = Enable output on transmit lane 3 | R/W              |

| 1.9.3    | PMD transmit disable 2      | 1 = Disable output on transmit lane 2<br>0 = Enable output on transmit lane 2 | R/W              |

| 1.9.2    | PMD transmit disable 1      | 1 = Disable output on transmit lane 1<br>0 = Enable output on transmit lane 1 | R/W              |

| 1.9.1    | PMD transmit disable 0      | 1 = Disable output on transmit lane 0<br>0 = Enable output on transmit lane 0 | R/W              |

| 1.9.0    | Global PMD transmit disable | 1 = Disable transmitter output<br>0 = Enable transmitter output               | R/W              |

<sup>&</sup>lt;sup>a</sup>R/W = Read/Write

#### 45.2.1.8.1 PMD transmit disable 3 (1.9.4)

When bit 1.9.4 is set to a one, the PMD shall disable output on lane 3 of the transmit path. When bit 1.9.4 is set to a zero, the PMD shall enable output on lane 3 of the transmit path.

The default value for bit 1.9.4 is zero.

NOTE—Transmission will not be enabled when this bit is set to a zero unless the global PMD transmit disable bit is also zero.

# 45.2.1.8.2 PMD transmit disable 2 (1.9.3)

I

When bit 1.9.3 is set to a one, the PMD shall disable output on lane 2 of the transmit path. When bit 1.9.3 is set to a zero, the PMD shall enable output on lane 2 of the transmit path.

The default value for bit 1.9.3 is zero.

NOTE—Transmission will not be enabled when this bit is set to a zero unless the global PMD transmit disable bit is also zero.

# 45.2.1.8.3 PMD transmit disable 1 (1.9.2)

When bit 1.9.2 is set to a one, the PMD shall disable output on lane 1 of the transmit path. When bit 1.9.2 is set to a zero, the PMD shall enable output on lane 1 of the transmit path.

The default value for bit 1.9.2 is zero.

NOTE—Transmission will not be enabled when this bit is set to a zero unless the global PMD transmit disable bit is also zero.

# 45.2.1.8.4 PMD transmit disable 0 (1.9.1)

When bit 1.9.1 is set to a one, the PMD shall disable output on lane 0 of the transmit path. When bit 1.9.1 is set to a zero, the PMD shall enable output on lane 0 of the transmit path.

The default value for bit 1.9.1 is zero.

NOTE—Transmission will not be enabled when this bit is set to a zero unless the global PMD transmit disable bit is also zero.

#### 45.2.1.8.5 Global PMD transmit disable (1.9.0)

When bit 1.9.0 is set to a one, the PMD shall disable output on the transmit path. When bit 1.9.0 is set to a zero, the PMD shall enable output on the transmit path.

For single wavelength PMD types, transmission will be disabled when this bit is set to one. When this bit is set to zero, transmission is enabled.

For multiple wavelength PMD types, transmission will be disabled on all lanes when this bit is set to one. When this bit is set to zero, the lanes are individually controlled by their corresponding transmit disable bits 1.9.4:1.

The default value for bit 1.9.0 is zero.

# 45.2.1.9 10G PMD receive signal detect register (Register 1.10)

The assignment of bits in the 10G PMD receive signal detect register is shown in Table 45–10. The 10G PMD receive signal detect register is mandatory. PMD types that use only a single wavelength indicate the status of the receive signal detect using bit 1.10.0 and return a value of zero for bits 1.10.4:1. PMD types that use multiple wavelengths indicate the status of each lane in bits 1.10.4:1 and the logical AND of those bits in bit 1.10.0.

Table 45–10—10G PMD receive signal detect register bit definitions

| Bit(s)    | Name                             | Description                                                                        | R/W <sup>a</sup> |

|-----------|----------------------------------|------------------------------------------------------------------------------------|------------------|

| 1.10.15:5 | Reserved                         | Value always 0, writes ignored                                                     | RO               |

| 1.10.4    | PMD receive signal detect 3      | 1 = Signal detected on receive lane 3<br>0 = Signal not detected on receive lane 3 | RO               |

| 1.10.3    | PMD receive signal detect 2      | 1 = Signal detected on receive lane 2<br>0 = Signal not detected on receive lane 2 | RO               |

| 1.10.2    | PMD receive signal detect 1      | 1 = Signal detected on receive lane 1<br>0 = Signal not detected on receive lane 1 | RO               |

| 1.10.1    | PMD receive signal detect 0      | 1 = Signal detected on receive lane 0<br>0 = Signal not detected on receive lane 0 | RO               |

| 1.10.0    | Global PMD receive signal detect | 1 = Signal detected on receive<br>0 = Signal not detected on receive               | RO               |

<sup>a</sup>RO = Read Only

#### 45.2.1.9.1 PMD receive signal detect 3 (1.10.4)

When bit 1.10.4 is read as a one, a signal has been detected on lane 3 of the PMD receive path. When bit 1.10.4 is read as a zero, a signal has not been detected on lane 3 of the PMD receive path.

### 45.2.1.9.2 PMD receive signal detect 2 (1.10.3)

When bit 1.10.3 is read as a one, a signal has been detected on lane 2 of the PMD receive path. When bit 1.10.3 is read as a zero, a signal has not been detected on lane 2 of the PMD receive path.

#### 45.2.1.9.3 PMD receive signal detect 1 (1.10.2)

When bit 1.10.2 is read as a one, a signal has been detected on lane 1 of the PMD receive path. When bit 1.10.2 is read as a zero, a signal has not been detected on lane 1 of the PMD receive path.

#### 45.2.1.9.4 PMD receive signal detect 0 (1.10.1)

When bit 1.10.1 is read as a one, a signal has been detected on lane 0 of the PMD receive path. When bit 1.10.1 is read as a zero, a signal has not been detected on lane 0 of the PMD receive path.

#### 45.2.1.9.5 Global PMD receive signal detect (1.10.0)

When bit 1.10.0 is read as a one, a signal has been detected on all the PMD receive paths. When bit 1.10.0 is read as a zero, a signal has not been detected on at least one of the PMD receive paths.

Single wavelength PMD types indicate the status of their receive path signal using this bit.

Multiple wavelength PMD types indicate the global status of the lane-by-lane signal detect indications using this bit. This bit is read as a one when all the lane signal detect indications are one; otherwise, this bit is read as a zero.

page 15 / 88

ı

# 45.2.1.10 PMA/PMD package identifier (Registers 1.14 and 1.15)

Registers 1.14 and 1.15 provide a 32-bit value, which may constitute a unique identifier for a particular type of package that the PMA/PMD is instantiated within. The identifier shall be composed of the 3rd through 24th bits of the Organizationally Unique Identifier (OUI) assigned to the package manufacturer by the IEEE, plus a six-bit model number, plus a four-bit revision number. A PMA/PMD may return a value of zero in each of the 32 bits of the package identifier.

A non-zero package identifier may be returned by one or more MMDs in the same package. The package identifier may be the same as the device identifier.

The format of the package identifier is specified in 22.2.4.3.1.

# 45.2.2 WIS registers

The assignment of registers in the WIS is shown in Table 45-11. For the WIS octet fields, bit 8 of the corresponding field in the WIS frame maps to the lowest numbered bit of the field in the register.

Table 45-11-WIS registers

| Register address  | Register name                          |

|-------------------|----------------------------------------|

| 2.0               | WIS control 1                          |

| 2.1               | WIS status 1                           |

| 2.2, 2.3          | WIS device identifier                  |

| 2.4               | WIS speed ability                      |

| 2.5, 2.6          | WIS devices in package                 |

| 2.7               | 10G WIS control 2                      |

| 2.8               | 10G WIS status 2                       |

| 2.9               | 10G WIS test-pattern error counter     |

| 2.10 through 2.13 | Reserved                               |

| 2.14, 2.15        | WIS package identifier                 |

| 2.16 through 2.32 | Reserved                               |

| 2.33              | 10G WIS status 3                       |

| 2.34 through 2.36 | Reserved                               |

| 2.37              | 10G WIS far end path block error count |

| 2.38              | Reserved                               |

| 2.39 through 2.46 | 10G WIS J1 transmit                    |

| 2.47 through 2.54 | 10G WIS J1 receive                     |

Table 45–11—WIS registers (continued)

| Register address          | Register name                   |

|---------------------------|---------------------------------|

| 2.55, 2.56                | 10G WIS far end line BIP errors |

| 2.57, 2.58                | 10G WIS line BIP errors         |

| 2.59                      | 10G WIS path block error count  |

| 2.60                      | 10G WIS section BIP error count |

| 2.61 through 2.63         | Reserved                        |

| 2.64 through 2.71         | 10G WIS J0 transmit             |

| 2.72 through 2.79         | 10G WIS J0 receive              |

| 2.80 through 2.32 767     | Reserved                        |

| 2.32 768 through 2.65 535 | Vendor specific                 |

#### 45.2.2.1 WIS control 1 register (Register 2.0)

The assignment of bits in the WIS control 1 register is shown in Table 45–12. The default value for each bit of the WIS control 1 register should be chosen so that the initial state of the device upon power up or reset is a normal operational state without management intervention.

#### 45.2.2.1.1 Reset (2.0.15)

Resetting a WIS is accomplished by setting bit 2.0.15 to a one. This action shall set all WIS registers to their default states. As a consequence, this action may change the internal state of the WIS and the state of the physical link. This action may also initiate a reset in any other MMDs that are instantiated in the same package. This bit is self-clearing, and a WIS shall return a value of one in bit 2.0.15 when a reset is in progress and a value of zero otherwise. A WIS is not required to accept a write transaction to any of its registers until the reset process is completed. The reset process shall be completed within 0.5 s from the setting of bit 2.0.15. During a reset, a WIS shall respond to reads from register bits 2.0.15 and 2.8.15:14. All other register bits should be ignored.

NOTE—This operation may interrupt data communication.

### 45.2.2.1.2 Loopback (2.0.14)

The WIS shall be placed in a Loopback mode of operation when bit 2.0.14 is set to a one. When bit 2.0.14 is set to a one, the WIS shall ignore all data presented to it by the PMA sublayer. When bit 2.0.14 is set to a one, the WIS shall accept data on the transmit path and return it on the receive path. For 10 Gb/s operation, the detailed behavior of the WIS during loopback is specified in 50.3.9

The default value of bit 2.0.14 is zero.

NOTE—The signal path through the WIS that is exercised in the Loopback mode of operation is implementation specific, but it is recommended that the signal path encompass as much of the WIS circuitry as is practical. The intention of providing this Loopback mode of operation is to permit a diagnostic or self-test function to perform the transmission and

Table 45–12— WIS control 1 register bit definitions

| Bit(s)   | Name            | Description                                                                                                          | R/W <sup>a</sup> |

|----------|-----------------|----------------------------------------------------------------------------------------------------------------------|------------------|

| 2.0.15   | Reset           | 1 = WIS reset<br>0 = Normal operation                                                                                | R/W<br>SC        |

| 2.0.14   | Loopback        | 1 = Enable Loopback mode<br>0 = Disable Loopback mode                                                                | R/W              |

| 2.0.13   | Speed selection | 1 = Operation at 10 Gb/s and above<br>0 = Unspecified                                                                | R/W              |

| 2.0.12   | Reserved        | Value always 0, writes ignored                                                                                       | R/W              |

| 2.0.11   | Low power       | 1 = Low-power mode<br>0 = Normal operation                                                                           | R/W              |

| 2.0.10:7 | Reserved        | Value always 0, writes ignored                                                                                       | R/W              |

| 2.0.6    | Speed selection | 1 = Operation at 10 Gb/s and above<br>0 = Unspecified                                                                | R/W              |

| 2.0.5:2  | Speed selection | 5 4 3 2<br>1 x x x = Reserved<br>x 1 x x = Reserved<br>x x 1 x = Reserved<br>0 0 0 1 = Reserved<br>0 0 0 0 = 10 Gb/s | R/W              |

| 2.0.1:0  | Reserved        | Value always 0, writes ignored                                                                                       | R/W              |

<sup>&</sup>lt;sup>a</sup>R/W = Read/Write, SC = Self Clearing

reception of a PDU, thus testing the transmit and receive data paths. Other loopback signal paths may be enabled using loopback controls within other MMDs.

# 45.2.2.1.3 Low power (2.0.11)

A WIS may be placed into a low-power mode by setting bit 2.0.11 to a one. This action may also initiate a low-power mode in any other MMDs that are instantiated in the same package. The low-power mode is exited by resetting the WIS. The behavior of the WIS in transition to and from the low-power mode is implementation specific and any interface signals should not be relied upon. While in the low-power mode, the device shall, as a minimum, respond to management transactions necessary to exit the low-power mode. The default value of bit 2.0.11 is zero.

### 45.2.2.1.4 Speed selection (2.0.13, 2.0.6, and 2.0.5:2)

Speed selection bits 2.0.13 and 2.0.6 shall both be written as a one. Any attempt to change the bits to an invalid setting shall be ignored. These two bits are set to one in order to make them compatible with Clause

The speed of the WIS may be selected using bits 5 through 2. The speed abilities of the WIS are advertised in the WIS speed ability register. A WIS may ignore writes to the WIS speed selection bits that select speeds it has not advertised in the WIS speed ability register. It is the responsibility of the STA entity to ensure that mutually acceptable speeds are applied consistently across all the MMDs on a particular PHY.

The WIS speed selection defaults to a supported ability.

# 45.2.2.2 WIS status 1 register (Register 2.1)

The assignment of bits in the WIS status 1 register is shown in Table 45–13. All the bits in the WIS status 1 register are read only; a write to the WIS status 1 register shall have no effect.

Table 45-13-WIS status 1 register bit definitions

| Bit(s)   | Name              | Description                                                                | R/W <sup>a</sup> |

|----------|-------------------|----------------------------------------------------------------------------|------------------|

| 2.1.15:8 | Reserved          | Ignore when read                                                           | RO               |

| 2.1.7    | Fault             | 1 = Fault condition<br>0 = No fault condition                              | RO/LH            |

| 2.1.6:3  | Reserved          | Ignore when read                                                           | RO               |

| 2.1.2    | Link status       | 1 = WIS link up<br>0 = WIS link down                                       | RO/LL            |

| 2.1.1    | Low-power ability | 1 = WIS supports low-power mode<br>0 = WIS does not support low-power mode | RO               |

| 2.1.1:0  | Reserved          | Ignore when read                                                           | RO               |

<sup>&</sup>lt;sup>a</sup>RO = Read Only, LH = Latching High, LL = Latching Low

#### 45.2.2.2.1 Fault (2.1.7)

When read as a one, bit 2.1.7 indicates that the WIS has detected a fault condition. When read as a zero, bit 2.1.7 indicates that the WIS has not detected a fault condition. The fault bit shall be implemented with latching high behavior.

The default value of bit 2.1.7 is zero.

### 45.2.2.2.2 Link status (2.1.2)

When read as a one, bit 2.1.2 indicates that the WIS receive link is up. When read as a zero, bit 2.1.2 indicates that the WIS receive link is down. The link status bit shall be implemented with latching low behavior.

### 45.2.2.3 Low-power ability (2.1.1)

When read as a one, bit 2.1.1 indicates that the WIS supports the low-power feature. When read as a zero, bit 2.1.1 indicates that the WIS does not support the low-power feature. If a WIS supports the low-power feature, then it is controlled using the low-power bit in the WIS control register.

# 45.2.2.3 WIS device identifier (Registers 2.2 and 2.3)

Registers 2.2 and 2.3 provide a 32-bit value, which may constitute a unique identifier for a particular type of WIS. The identifier shall be composed of the 3rd through 24th bits of the Organizationally Unique Identifier (OUI) assigned to the device manufacturer by the IEEE, plus a six-bit model number, plus a four-bit revision number. A WIS may return a value of zero in each of the 32 bits of the WIS device identifier.

The format of the WIS device identifier is specified in 22.2.4.3.1.

# 45.2.2.4 WIS speed ability (Register 2.4)

The assignment of bits in the WIS speed ability register is shown in Table 45–14.

Table 45-14— WIS speed ability register bit definitions

| Bit(s)   | Name                       | Description                                                                                  | R/W <sup>a</sup> |

|----------|----------------------------|----------------------------------------------------------------------------------------------|------------------|

| 2.4.15:1 | Reserved for future speeds | Value always 0, writes ignored                                                               | RO               |

| 2.4.0    | 10G capable                | 1 = WIS is capable of operating at 10 Gb/s<br>0 = WIS is not capable of operating at 10 Gb/s | RO               |

$<sup>^{</sup>a}RO = Read Only$

# 45.2.2.4.1 10G capable (2.4.0)

When read as a one, bit 2.4.0 indicates that the WIS is able to operate at a data rate of 10 Gb/s (9.58 Gb/s payload rate). When read as a zero, bit 2.4.0 indicates that the WIS is not able to operate at a data rate of 10 Gb/s (9.58 Gb/s payload rate).

# 45.2.2.5 WIS devices in package (Registers 2.5 and 2.6)

The assignment of bits in the WIS devices in package registers is shown in Table 45–15.

When read as a one, a bit in the WIS devices in package registers indicates that the associated MMD has been instantiated within the same package as other MMDs whose associated bits have been set to a one within the WIS devices in package registers. Bit 2.5.0 is used to indicate that Clause 22 functionality has been implemented within a Clause 45 electrical interface device. The definition of the term package is vendor specific and could be a chip, module, or other similar entity.

#### 45.2.2.6 10G WIS control 2 register (Register 2.7)

The assignment of bits in the 10G WIS control 2 register is shown in Table 45–16. The default value for each bit of the 10G WIS control 2 register should be chosen so that the initial state of the device upon power up or reset is a normal operational state without management intervention.

# 45.2.2.6.1 PRBS31 receive test-pattern enable (2.7.5)

If the WIS supports the optional PRBS31 (see 49.2.8) pattern testing advertised in bit 2.8.1 and the mandatory receive test-pattern enable bit (2.7.2) is not one, setting bit 2.7.5 to a one shall set the receive path of the WIS into the PRBS31 test-pattern mode. Setting bit 2.7.5 to a zero shall disable the PRBS31 test-pattern mode on the receive path of the WIS. The behavior of the WIS when in PRBS31 test-pattern mode is specified in 50.3.8.2

#### 45.2.2.6.2 PRBS31 transmit test-pattern enable (2.7.4)

If the WIS supports the optional PRBS31 pattern testing advertised in bit 2.8.1 and the mandatory transmit test-pattern enable bit (2.7.1) is not one, then setting bit 2.7.4 to a one shall set the transmit path of the WIS into the PRBS31 test-pattern mode. Setting bit 2.7.4 to a zero shall disable the PRBS31 test-pattern mode on

Table 45–15— WIS devices in package registers bit definitions

| Bit(s)   | Name                             | Description                                                                                            | R/W <sup>a</sup> |

|----------|----------------------------------|--------------------------------------------------------------------------------------------------------|------------------|

| 2.6.15   | Vendor specific device 2 present | 1 = Vendor specific device 2 present in package<br>0 = Vendor specific device 2 not present in package | RO               |

| 2.6.14   | Vendor specific device 1 present | 1 = Vendor specific device 1 present in package<br>0 = Vendor specific device 1 not present in package | RO               |

| 2.6.13:0 | Reserved                         | Ignore on read                                                                                         | RO               |

| 2.5.15:6 | Reserved                         | Ignore on read                                                                                         | RO               |

| 2.5.5    | DTE XS present                   | 1 = DTE XS present in package<br>0 = DTE XS not present in package                                     | RO               |

| 2.5.4    | PHY XS present                   | 1 = PHY XS present in package<br>0 = PHY XS not present in package                                     | RO               |

| 2.5.3    | PCS present                      | 1 = PCS present in package<br>0 = PCS not present in package                                           | RO               |

| 2.5.2    | WIS present                      | 1 = WIS present in package<br>0 = WIS not present in package                                           | RO               |

| 2.5.1    | PMD/PMA present                  | 1 = PMA/PMD present in package<br>0 = PMA/PMD not present in package                                   | RO               |

| 2.5.0    | Clause 22 registers present      | 1 = Clause 22 registers present in package<br>0 = Clause 22 registers not present in package           | RO               |

$^{a}RO = Read Only$

Table 45-16—10G WIS control 2 register bit definitions

| Bit(s)   | Name                                     | Description                                                                                                         | R/W <sup>a</sup> |

|----------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------|

| 2.7.15:6 | Reserved                                 | Value always 0, writes ignored                                                                                      | R/W              |

| 2.7.5    | PRBS31 receive test-pat-<br>tern enable  | 1 = Enable PRBS31 test-pattern mode on the receive path<br>0 = Disable PRBS31 test-pattern mode on the receive path | R/W              |

| 2.7.4    | PRBS31 transmit test-pat-<br>tern enable | 1 = Enable PRBS31 test-pattern mode on the transmit path 0 = Disable PRBS31 test-pattern mode on the transmit path  | R/W              |

| 2.7.3    | Test-pattern selection                   | 1 = Select square wave test pattern 0 = Select mixed-frequency test pattern                                         | R/W              |

| 2.7.2    | Receive test-pattern enable              | 1 = Enable test-pattern mode on the receive path 0 = Disable test-pattern mode on the receive path                  | R/W              |

| 2.7.1    | Transmit test-pattern enable             | 1 = Enable test-pattern mode on the transmit path 0 = Disable test-pattern mode on the transmit path                | R/W              |

| 2.7.0    | PCS type selection                       | 1 = Select 10GBASE-W PCS type<br>0 = Select 10GBASE-R PCS type                                                      | R/W              |

${}^{a}R/W = Read/Write$

I

the transmit path of the WIS. The behavior of the WIS when in PRBS31 test-pattern mode is specified in 50.3.8.2

# 45.2.2.6.3 Test-pattern selection (2.7.3)

Bit 2.7.3 controls the type of pattern sent by the transmitter when in test-pattern mode. Setting bit 2.7.3 to a one shall select the square wave test pattern. Setting bit 2.7.3 to a zero shall select the mixed-frequency test pattern. The details of the test patterns are specified in Clause 50.

#### 45.2.2.6.4 Receive test-pattern enable (2.7.2)

Setting bit 2.7.2 to a one shall set the receive path of the WIS into the test-pattern mode. Setting bit 2.7.2 to a zero shall disable the test-pattern mode on the receive path of the WIS. The behavior of the WIS when in test-pattern mode is specified in Clause 50.

#### 45.2.2.6.5 Transmit test-pattern enable (2.7.1)

Setting bit 2.7.1 to a one shall set the transmit path of the WIS into the test-pattern mode. Setting bit 2.7.1 to a zero shall disable the test-pattern mode on the transmit path of the WIS. The behavior of the WIS when in test-pattern mode is specified in Clause 50.

#### 45.2.2.6.6 PCS type selection (2.7.0)

Setting bit 2.7.0 to a one shall enable the 10GBASE-W logic and set the speed of the WIS-PMA interface to 9.95328 Gb/s. Setting bit 2.7.0 to a zero shall disable the 10GBASE-W logic, set the speed of the PCS-PMA interface to 10.3125 Gb/s and bypass the data around the 10GBASE-W logic. A WIS that is only capable of supporting 10GBASE-W operation and is unable to support 10GBASE-R operation shall ignore values written to this bit and shall return a value of one when read. It is the responsibility of the STA entity to ensure that mutually acceptable MMD types are applied consistently across all the MMDs on a particular PHY.

#### 45.2.2.7 10G WIS status 2 register (Register 2.8)

The assignment of bits in the 10G WIS status 2 register is shown in Table 45–17. All the bits in the 10G WIS status 2 register are read only; a write to the 10G WIS status 2 register shall have no effect.

Table 45-17-10G WIS status 2 register bit definitions

| Bit(s)    | Name                           | Description                                                                                                                                                                    | R/W <sup>a</sup> |

|-----------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 2.8.15:14 | Device present                 | 15 14 1 0 = Device responding at this address 1 1 = No device responding at this address 0 1 = No device responding at this address 0 0 = No device responding at this address | RO               |

| 2.8.13:2  | Reserved                       | Ignore when read                                                                                                                                                               | RO               |

| 2.8.1     | PRBS31 pattern testing ability | 1 = WIS is able to support PRBS31 pattern testing<br>0 = WIS is not able to support PRBS31 pattern testing                                                                     | RO               |

| 2.8.0     | 10GBASE-R ability              | 1 = WIS is able to support 10GBASE-R port types<br>0 = WIS is not able to support 10GBASE-R port types                                                                         | RO               |

$<sup>^{</sup>a}RO = Read Only$

#

45.2.2.7.1 Device present (2.8.15:14)

When read as <10>, bits 2.8.15:14 indicate that a device is present and responding at this register address. When read as anything other than <10>, bits 2.8.15:14 indicate that no device is present at this address or that the device is not functioning properly.

#### 45.2.2.7.2 PRBS31 pattern testing ability (2.8.1)

When read as a one, bit 2.8.1 indicates that the WIS is able to support PRBS31 pattern testing. When read as a zero, bit 2.8.1 indicates that the WIS is not able to support PRBS31 pattern testing. If the WIS is able to support PRBS31 pattern testing, then the pattern generation and checking is controlled using bits 2.7.5:4.

# 45.2.2.7.3 10GBASE-R ability (2.8.0)

When read as a one, bit 2.8.0 indicates that the WIS is able to bypass the WIS logic and adjust the XSBI interface speed to support 10GBASE-R port types. When read as a zero, bit 2.8.0 indicates that the WIS is not able to bypass the WIS logic and cannot support 10GBASE-R port types.

# 45.2.2.8 10G WIS test-pattern error counter register (Register 2.9)

The assignment of bits in the 10G WIS test-pattern error counter register is shown in Table 45–18. This register is only required when the PRBS31 pattern generation capability is supported.

Table 45–18—10G WIS test-pattern error counter register bit definitions

| Bit(s)   | Name                       | Description   | R/W <sup>a</sup> |

|----------|----------------------------|---------------|------------------|

| 2.9.15:0 | Test-pattern error counter | Error counter | RO               |

$^{a}RO = Read Only$

The test-pattern error counter is a sixteen bit counter that contains the number of errors received during a pattern test. These bits shall be reset to all zeros when the test-pattern error counter is read by the management function or upon execution of the WIS reset. These bits shall be held at all ones in the case of overflow. The test-pattern methodology is described in 49.2.8.

# 45.2.2.9 WIS package identifier (Registers 2.14 and 2.15)

Registers 2.14 and 2.15 provide a 32-bit value, which may constitute a unique identifier for a particular type of package that the WIS is instantiated within. The identifier shall be composed of the 3rd through 24th bits of the Organizationally Unique Identifier (OUI) assigned to the package manufacturer by the IEEE, plus a six-bit model number, plus a four-bit revision number. A WIS may return a value of zero in each of the 32 bits of the WIS package identifier.

A non-zero package identifier may be returned by one or more MMDs in the same package. The package identifier may be the same as the device identifier.

The format of the WIS package identifier is specified in 22.2.4.3.1.

# 45.2.2.10 10G WIS status 3 register (Register 2.33)

The assignment of bits in the 10G WIS status 3 register is shown in Table 45–19. All the bits in the 10G WIS status 3 register are read only; a write to the 10G WIS status 3 register shall have no effect.

Table 45-19-10G WIS status 3 register bit definitions

| Bit(s)     | Name                | Description                                                                                                                         | R/W <sup>a</sup> |

|------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 2.33.15:12 | Reserved            | Ignore when read                                                                                                                    | RO               |

| 2.33.11    | SEF                 | Severely errored frame                                                                                                              | RO/LH            |

| 2.33.10    | Far end PLM-P/LCD-P | 1 = Far end path label mismatch / Loss of codegroup delineation 0 = No far end path label mismatch / Loss of code-group delineation | RO/LH            |

| 2.33.9     | Far end AIS-P/LOP-P | 1 = Far end path alarm indication signal / Path loss of pointer 0 = No far end path alarm indication signal / Path loss of pointer  | RO/LH            |

| 2.33.8     | Reserved            | Ignore when read                                                                                                                    | RO               |

| 2.33.7     | LOF                 | 1 = Loss of frame flag raised<br>0 = Loss of frame flag lowered                                                                     | RO/LH            |

| 2.33.6     | LOS                 | 1 = Loss of signal flag raised<br>0 = Loss of signal flag lowered                                                                   | RO/LH            |

| 2.33.5     | RDI-L               | 1 = Line remote defect flag raised<br>0 = Line remote defect flag lowered                                                           | RO/LH            |

| 2.33.4     | AIS-L               | 1 = Line alarm indication flag raised<br>0 = Line alarm indication flag lowered                                                     | RO/LH            |

| 2.33.3     | LCD-P               | 1 = Path loss of code-group delineation flag raised 0 = Path loss of code-group delineation flag lowered                            | RO/LH            |

| 2.33.2     | PLM-P               | 1 = Path label mismatch flag raised<br>0 = Path label mismatch flag lowered                                                         | RO/LH            |

| 2.33.1     | AIS-P               | 1 = Path alarm indication signal raised<br>0 = Path alarm indication signal lowered                                                 | RO/LH            |

| 2.33.0     | LOP-P               | 1 = Loss of pointer flag raised<br>0 = Loss of pointer flag lowered                                                                 | RO/LH            |

<sup>&</sup>lt;sup>a</sup>RO = Read Only, LH = Latching High

# 45.2.2.10.1 SEF (2.33.11)

When read as a one, bit 2.33.11 indicates that the SEF flag has been raised by the WIS. When read as a zero, bit 2.33.11 indicates that the SEF flag is lowered. The SEF bit shall be implemented with latching high behavior.

5 6

The SEF functionality implemented by the WIS is described in 50.3.2.5.

7 8

# 45.2.2.10.2 Far end PLM-P/LCD-P (2.33.10)

9 10 11

12

13

When read as a one, bit 2.33.10 indicates that the far end path label mismatch/loss of code-group delineation flag has been raised. When read as a zero, bit 2.33.10 indicates that the far end path label mismatch/loss of code-group delineation flag is lowered. The far end PLM-P/LCD-P bit shall be implemented with latching high behavior.

14 15 16

The far end path label mismatch/loss of code-group delineation functionality implemented by the WIS is described in 50.3.2.5.

17 18 19

## 45.2.2.10.3 Far end AIS-P/LOP-P (2.33.9)

20 21

22

23

When read as a one, bit 2.33.9 indicates that the far end path alarm indication signal/path loss of pointer flag has been raised by the WIS. When read as a zero, bit 2.33.9 indicates that the far end path alarm indication signal/path loss of pointer flag is lowered. The far end AIS-P/LOP-P bit shall be implemented with latching high behavior.

24 25 26

The far end path alarm indication signal/path loss of pointer functionality implemented by the WIS is described in 50.3.2.5.

27 28 29

#### 45.2.2.10.4 LOF (2.33.7)

30 31

32

When read as a one, bit 2.33.7 indicates that the loss of frame flag has been raised. When read as a zero, bit 2.33.7 indicates that the loss of frame flag is lowered. The LOF bit shall be implemented with latching high behavior.

33 34

The LOF functionality implemented by the WIS is described in 50.3.2.5.

35 36

### 45.2.2.10.5 LOS (2.33.6)

37 38 39

40

When read as a one, bit 2.33.6 indicates that the loss of signal flag has been raised. When read as a zero, bit 2.33.6 indicates that the loss of signal flag is lowered. The LOS bit shall be implemented with latching high behavior.

41 42 43

The LOS functionality implemented by the WIS is described in 50.3.2.5.

44 45

#### 45.2.2.10.6 RDI-L (2.33.5)

46 47

48

When read as a one, bit 2.33.5 indicates that the line remote defect flag has been raised. When read as a zero, bit 2.33.5 indicates that the line remote defect flag is lowered. The RDI-L bit shall be implemented with latching high behavior.

49 50 51

The RDI-L functionality implemented by the WIS is described in 50.3.2.5.

52

53 54

#### 45.2.2.10.7 AIS-L (2.33.4)

I

When read as a one, bit 2.33.4 indicates that the line alarm indication flag has been raised. When read as a zero, bit 2.33.4 indicates that the line alarm indication flag is lowered. The AIS-L bit shall be implemented with latching high behavior.

The AIS-L functionality implemented by the WIS is described in 50.3.2.5.

# 45.2.2.10.8 LCD-P (2.33.3)

When read as a one, bit 2.33.3 indicates that the loss of code-group delineation flag has been raised. When read as a zero, bit 2.33.3 indicates that the loss of code-group delineation flag is lowered. The LCD-P bit shall be implemented with latching high behavior.

The loss of code-group delineation functionality implemented by the WIS is described in 50.3.2.5.

# 45.2.2.10.9 PLM-P (2.33.2)

When read as a one, bit 2.33.2 indicates that the path label mismatch flag has been raised. When read as a zero, bit 2.33.2 indicates that the path label mismatch flag is lowered. The PLM-P bit shall be implemented with latching high behavior.

The PLM-P functionality implemented by the WIS is described in 50.3.2.5.

# 45.2.2.10.10 AIS-P (2.33.1)

When read as a one, bit 2.33.1 indicates that the path alarm indication signal has been raised. When read as a zero, bit 2.33.1 indicates that the path alarm indication signal is lowered. The AIS-P bit shall be implemented with latching high behavior.

The path alarm indication signal functionality implemented by the WIS is described in 50.3.2.5.

### 45.2.2.10.11 LOP-P (2.33.0)

When read as a one, bit 2.33.0 indicates that the loss of pointer flag has been raised. When read as a zero, bit 2.33.0 indicates that the loss of pointer flag is lowered. The LOP-P bit shall be implemented with latching high behavior.

The LOP-P functionality implemented by the WIS is described in 50.3.2.5.

### 45.2.2.11 10G WIS far end path block error count (Register 2.37)

The assignment of bits in the 10G WIS far end path block error count register is shown in Table 45–20.

#### Table 45-20-10G WIS far end path block error count register bit definitions

| 47 |

|----|

| 48 |

| 49 |

| 50 |

| Bit(s)    | Name                           | Description                    | R/W <sup>a</sup> |

|-----------|--------------------------------|--------------------------------|------------------|

| 2.37.15:0 | Far end path block error count | Far end path block error count | RO               |

$^{a}RO = Read Only,$

The 10G WIS far end path block error count is incremented by one whenever a far end path block error, defined in Annex 50A, is detected as described in 50.3.2.5. The counter wraps around to zero when it is incremented beyond its maximum value of 65 535. It is cleared to zero when the WIS is reset.

# 45.2.2.12 10G WIS J1 transmit (Registers 2.39 through 2.46)

The assignment of octets in the 10G WIS J1 transmit registers is shown in Table 45–21.

Table 45-21—10G WIS J1 transmit 0-15 register bit definitions

| Bit(s)    | Name           | Description                     | R/W <sup>a</sup> |

|-----------|----------------|---------------------------------|------------------|

| 2.46.15:8 | J1 transmit 15 | Transmitted path trace octet 15 | R/W              |

| 2.46.7:0  | J1 transmit 14 | Transmitted path trace octet 14 | R/W              |

| 2.45.15:8 | J1 transmit 13 | Transmitted path trace octet 13 | R/W              |

| 2.45.7:0  | J1 transmit 12 | Transmitted path trace octet 12 | R/W              |

| 2.44.15:8 | J1 transmit 11 | Transmitted path trace octet 11 | R/W              |

| 2.44.7:0  | J1 transmit 10 | Transmitted path trace octet 10 | R/W              |

| 2.43.15:8 | J1 transmit 9  | Transmitted path trace octet 9  | R/W              |

| 2.43.7:0  | J1 transmit 8  | Transmitted path trace octet 8  | R/W              |

| 2.42.15:8 | J1 transmit 7  | Transmitted path trace octet 7  | R/W              |

| 2.42.7:0  | J1 transmit 6  | Transmitted path trace octet 6  | R/W              |

| 2.41.15:8 | J1 transmit 5  | Transmitted path trace octet 5  | R/W              |

| 2.41.7:0  | J1 transmit 4  | Transmitted path trace octet 4  | R/W              |

| 2.40.15:8 | J1 transmit 3  | Transmitted path trace octet 3  | R/W              |

| 2.40.7:0  | J1 transmit 2  | Transmitted path trace octet 2  | R/W              |

| 2.39.15:8 | J1 transmit 1  | Transmitted path trace octet 1  | R/W              |

| 2.39.7:0  | J1 transmit 0  | Transmitted path trace octet 0  | R/W              |

${}^{a}R/W = Read/Write$

The first transmitted path trace octet is J1 transmit 15, which contains the delineation octet. The default value for the J1 transmit 15 octet is 137 (hexadecimal 89). The last transmitted path trace octet is J1 transmit 0. The default value for the J1 transmit 0 through 14 octets is 0. The transmitted path trace is described in 50.3.2.1.

I

# 45.2.2.13 10G WIS J1 receive (Registers 2.47 through 2.54)

The assignment of octets in the 10G WIS J1 receive registers is shown in Table 45–22.

Table 45–22—10G WIS J1 receive 0–15 register bit definitions

| Bit(s)    | Name          | Description                  | R/W <sup>a</sup> |