### Status Update - SDD21 & SDD11/22 Model Development

### John DAmbrosia, Tyco Electronics Matt Hendrick, Intel

# Acknowedgements

- Rich Mellitz, Intel

- Steve Krooswyk, Intel

- Mike Altmann, Intel

- Yves Braem, Tyco Electronics

- Mike Resso, Agilent

- Joe Abler, IBM

# Introduction

#### Reference dambrosia\_c1\_0105

- Recommended using proposed informative TP1 TP4 SDD21 Channel Model Mask

- Recommended eliminating informative TP1 TP4 SDD11 / 22 model masks

- Concern regarding this recommendation expressed

- Recommended eliminating informative TP1 TP4 SDD21 Group Delay Variation Mask

- Reference Rx models as defined in http://ieee802.org/3/ap/public/channel\_mode l/mellitz\_m1\_0105.pdf

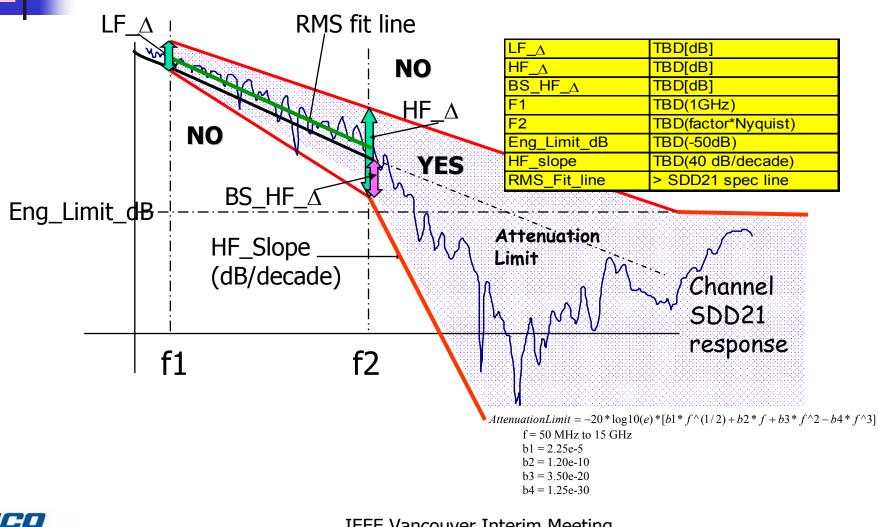

### Proposed Informative Model SDD21, TP1 – TP4

intel

| Parameter |       | Correlation |

|-----------|-------|-------------|

| . –       |       |             |

| LFmax     | Intel |             |

|           | Тусо  |             |

| LFmin     | Intel |             |

|           | Тусо  |             |

| HFmax     | Intel |             |

|           | Тусо  |             |

| HEmin     | Intel |             |

|           | Тусо  |             |

|           |       |             |

| BS LF     | Intel |             |

| _         | Тусо  |             |

|           |       |             |

| BS HF     | Intel |             |

| _         | Тусо  |             |

|           |       |             |

| FITabove  | Intel |             |

|           | Тусо  |             |

|           |       |             |

| FITbelow  | Intel |             |

|           | Тусо  |             |

| GD min    | Intel |             |

| _         |       |             |

|           | Тусо  |             |

|           | .,    |             |

| Parameter    |       | Correlation |

|--------------|-------|-------------|

| GD_max       | Intel |             |

|              | Тусо  |             |

| GDslope      | Intel |             |

|              | Тусо  |             |

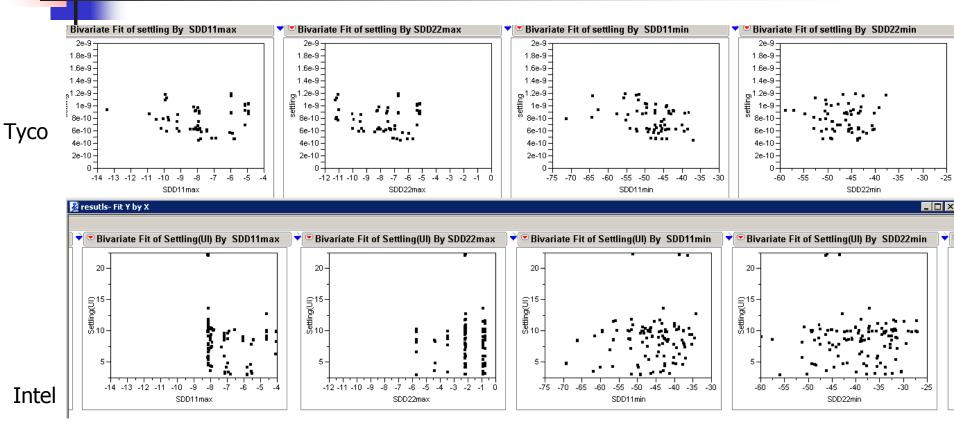

| SDD11max     | Intel |             |

|              | Тусо  |             |

| SDD22max     | Intel |             |

|              | Тусо  |             |

| SDD11min     | Intel |             |

|              | Тусо  |             |

| SDD22min     | Intel |             |

|              | Тусо  |             |

| peak         | Intel |             |

|              | Тусо  |             |

| n(TP)        | Intel |             |

|              | Тусо  |             |

| m(TN)        | Intel |             |

|              | Тусо  |             |

| TP(-1)       | Intel |             |

|              | Тусо  |             |

| TP(1)        | Intel |             |

|              | Тусо  |             |

| Total Length | Intel |             |

|              | Тусо  |             |

- dambrosia\_c1\_0105

recommended

eliminating TP1 TP4

Informative masks for

SDD11/22 and Group

Delay Variation.

- Concern expressed to deletion of informative TP1 - TP4 SDD11 /22 mask.

| Legend        |  |

|---------------|--|

| Strong        |  |

| Medium        |  |

| None          |  |

| Not Available |  |

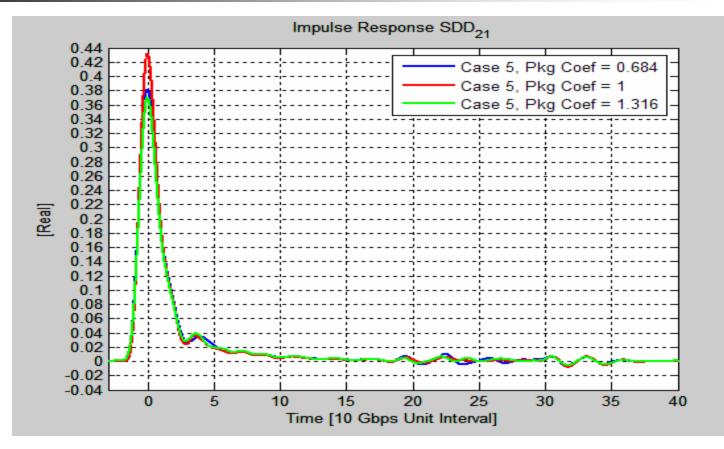

# SDD11 / SDD22

#### No correlation

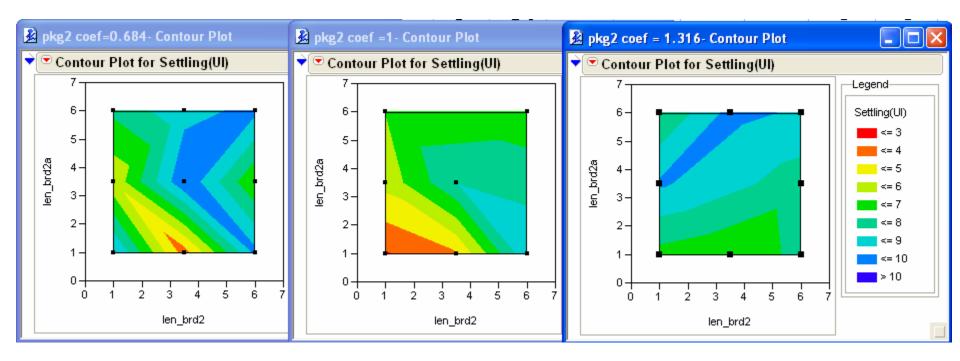

# Effect due to 10dB packages

- len\_brd2 length from connector on Rx line card to AC coupling Cap

- len\_brd2a length from AC coupling cap to Rx

- Update from dambrosia\_c1\_0105.pdf

- 10 dB packages had an impact.

- Reference http://ieee802.org/3/ap/public/channel\_model/mellitz\_m1\_0105.pdf

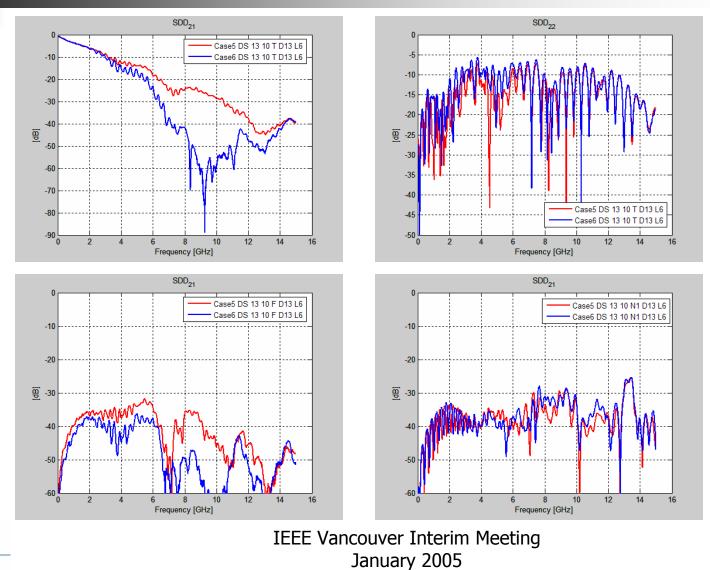

# Cases #5 and #6 Frequency Characterization (dambrosia\_02\_0105)

tyco

intel

8

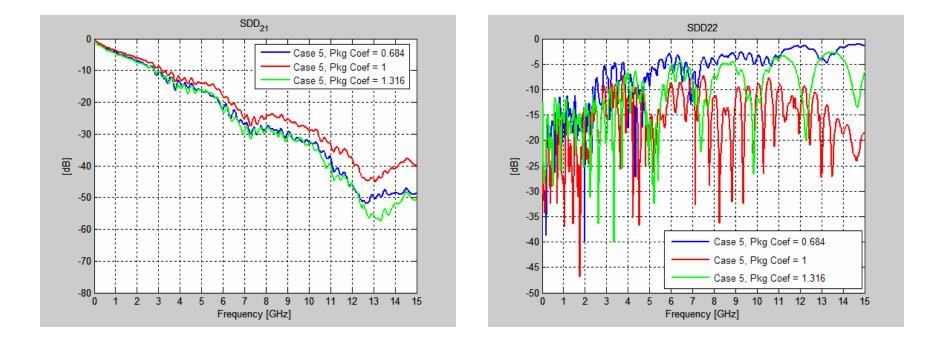

### Frequency Characterization – Case #5 Cascaded with Rx Packaging

Rx models as defined in http://ieee802.org/3/ap/public/channel\_model/mellitz\_m1\_0105.pdf

### Frequency Characterization – Case #6 Cascaded with Rx Packaging

Rx models as defined in http://ieee802.org/3/ap/public/channel\_model/mellitz\_m1\_0105.pdf

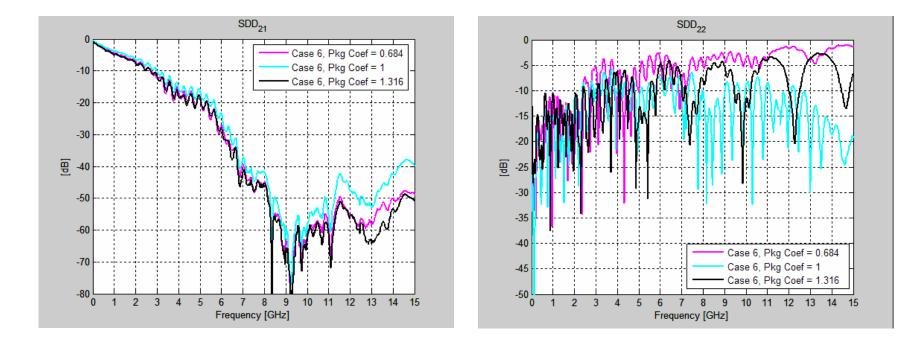

Reference – "PAM-4 Link Analysis, "http://grouper.ieee.org/groups/802/3/ap/public/may04/dambrosia\_01\_0504.pdf"

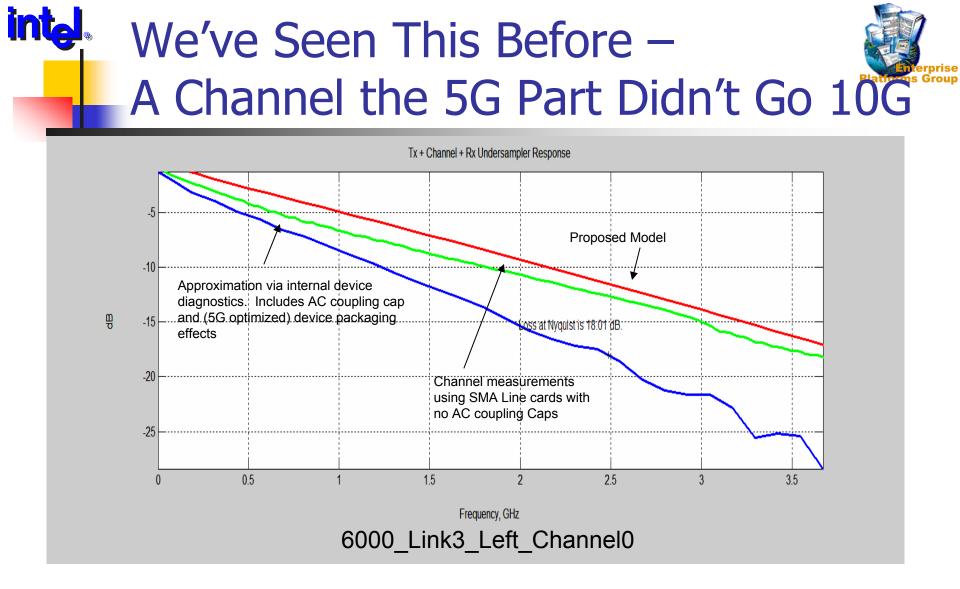

#### 10 Gbps Pulse Response Characterization -Case #5 Cascaded with Rx Packaging

Rx models as defined in http://ieee802.org/3/ap/public/channel\_model/mellitz\_m1\_0105.pdf

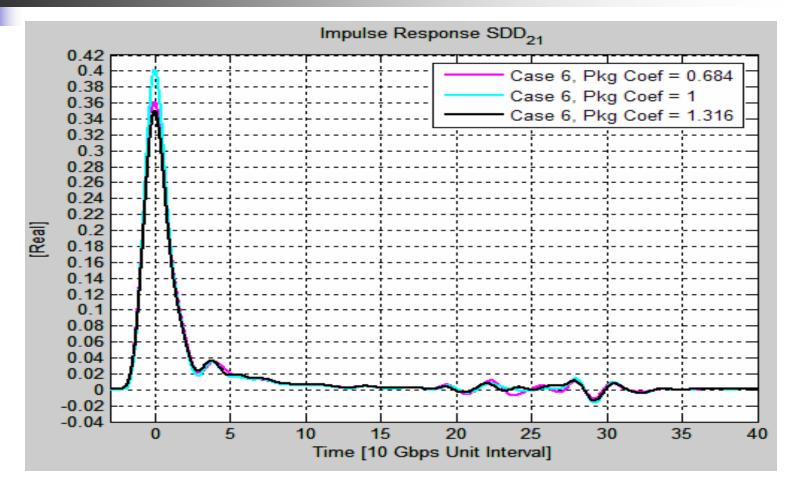

#### 10 Gbps Pulse Response Characterization -Case #6 Cascaded with Rx Packaging

Rx models as defined in http://ieee802.org/3/ap/public/channel\_model/mellitz\_m1\_0105.pdf

#### Per IBM - Additional Simulations for Cases #5 and #6 (dambrosia\_02\_0105)

|                                  | Case 5<br>FFE3/DFE3 | Case 5<br>FFE3/DFE5 | Case 6<br>FFE3/DFE3    | Case 6<br>FFE3/DFE5    |

|----------------------------------|---------------------|---------------------|------------------------|------------------------|

| 1. Original results              | 18.9%               | 22.2%               | 0% (BER floor at E-12) | 5.5%                   |

| 2. No Packaging                  | 15.7%               | 17.1%               | <0 (BER floor at E-8)  | <0 (BER floor at E-11) |

| 3. No Packaging, No IC           | 27.4%               | 27.0%               | 16.5%                  | 19.9%                  |

| 4. No Packaging, No IC, No Xtalk | 32.9%               | 33.0%               | 20.8%                  | 22.1%                  |

Simulation 1 – Original simulations, as specified in abler\_01\_00904.pdf

Simulation 2 – As stated in Simulation #1, except packaging removed

Simulation 3 – As stated in Simulation #2, except IC Model (ESD and load structures) replaced with perfect  $50\Omega$  terminations.

Simulation 4 – As stated in Simulation #3, except all crosstalk removed

Electronics

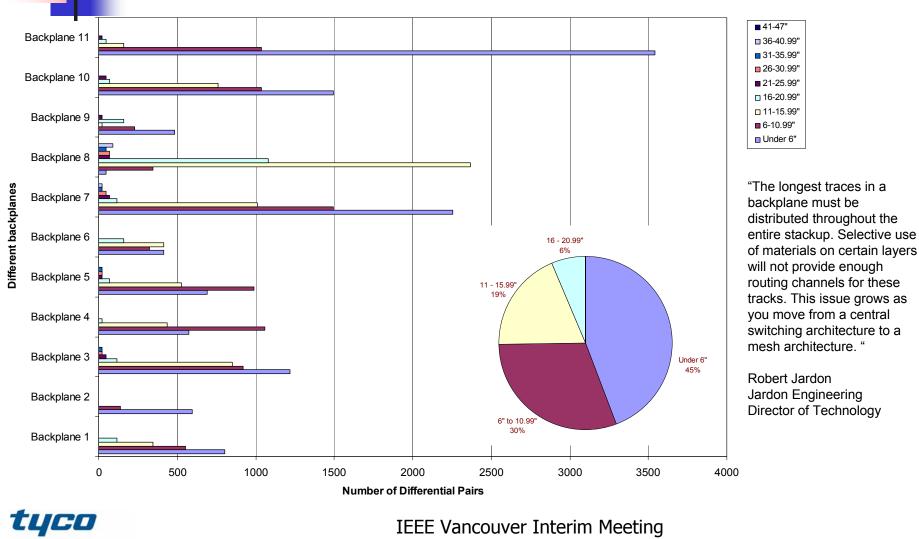

### Length Analysis in Real Backplanes

January 2005

15

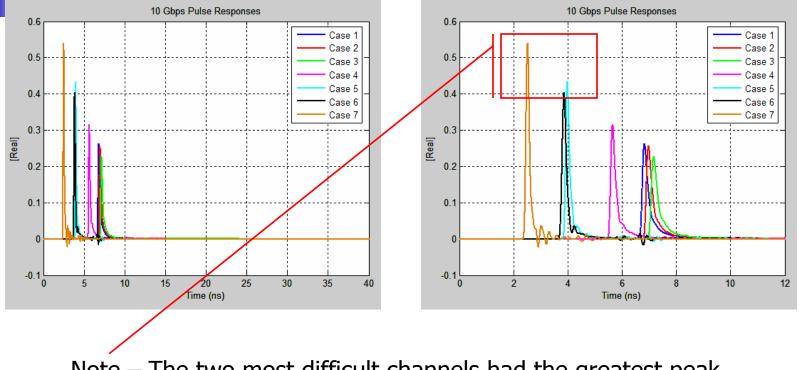

### Pulse Reponse of All Tyco Channels

Note – The two most difficult channels had the greatest peak Let's look at Cases #5 and #6

# Conclusions

- Parameters used in analysis based on proposed informative TP1 – TP4 SDD21 model are strong indicators of settling time.

- Need to review parameters in relation to efforts of Signaling Ad Hoc

- TP1 TP4 SDD11 / 22 is meaningful, but not by itself. It works in conjunction with -

- Tx Launched Signal

- Channel (TP1 / TP4) throughput

- Channel (TP1 / TP4) return loss

- Device return loss

- Package and IC (ESD / termination) effects

- Different channels exist in a backplane environment and each results in different frequency content delivery to the receiver resulting in different reflection characteristics.

# Recommendations

- Adopt proposed TP1/TP4 Informative SDD21 model template

- Specific recommendations for each value needs to be completed upon Signal Ad Hoc analysis

- Eliminate proposed TP1/TP4 Informative SDD11 / 22 mask

- Leave to normative analysis with inclusion of packaging effects

- Eliminate TP1/TP4 Informative Group Delay template