# XX.1 Forward Error Correction for 10GBASE-KR PHY

#### 1 2 3

10

11

#### 4 XX.1.1 Overview

5 This subclause specifies a Forward Error Correction (FEC) mechanism for the 10GBASE-KR PHY to provide 6 additional gain to increase the link budget and BER performance on a broader set of back plane channels as 7 defined in clause 69.

#### 8 XX.1.2 Objectives

9 The following are the objectives for the FEC:

- 1. To support Forward Error Correction mechanism for 10GBASE-KR PHYs.

- 12 2. To support the full duplex mode of operation of the Ethernet MAC.

- 13 3. To support the PCS, PMA and PMD sublayers defined for 10GBASE-KR.

- 14 4. To provide a 10.3125 Gb/s effective data rate at the service interface presented by the PMA sublayer.

- Support operations over links consistent with differential, controlled impedance traces on a printed circuit

board with 2 connectors and total length up to at least 1m meeting the requirements of 69.3.

- 17 6. Support a BER objective of  $10^{-12}$  or better.

# 18 XX.1.2 Functional Block Diagram

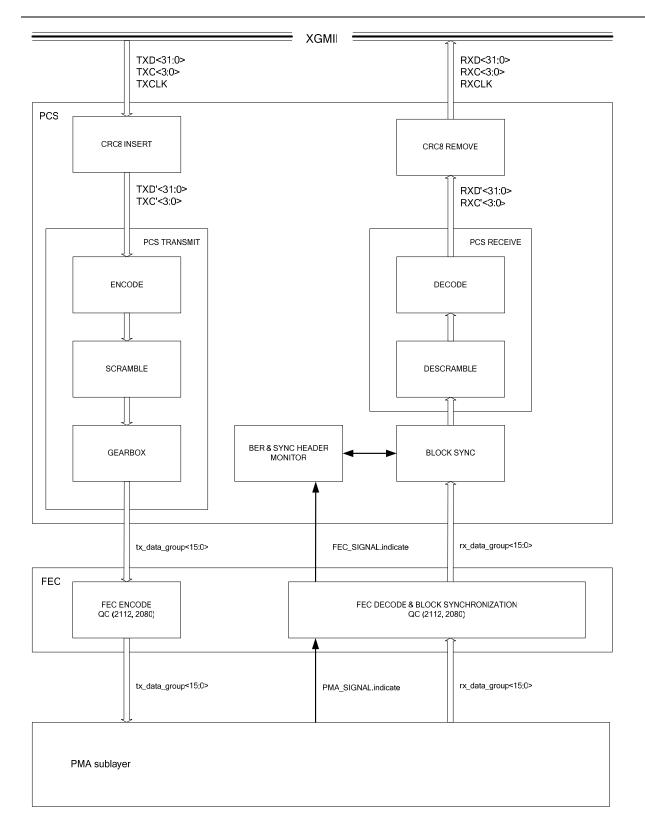

19 Figure XX-1 shows the functional block diagram of FEC for 10GBASE-KR PHY and the relationship between

- 20 the PCS and PMA sublayers.

- 21

# Figure XX-1 FEC Functional block diagram

#### 1 XX.1.3 FEC Service Interface

- 2 The FEC Service Interface is provided to allow the 10GBASE-KR PCS to transfer information to and from the

- 3 FEC. These services are defined in an abstract manner and do not imply any particular implementation. The FEC

- 4 Service Interface supports exchange of data-units between PCS entities on either side of a 10GBASE-KR link

- 5 using request and indication primitives. Data-units are mapped into FEC frames by the FEC and passed to the

- 6 PMA, and vice versa. 7

- 8 The following primitives are defined within the FEC Service Interface:

- 9 FEC\_UNITDATA.request(tx\_data-group<15:0>)

- 10 FEC\_UNITDATA.indication(rx\_data-group<15:0>)

- 11 FEC\_SIGNAL.indication(SIGNAL\_OK)12

# 13 XX.1.3.1 FEC\_UNITDATA.request

- This primitive defines the transfer of data in the form of constant-width data-units from the PCS to the FEC. The data supplied via FEC\_UNITDATA.request mapped by the FEC Transmit process into the payload capacity of the outgoing FEC frame stream.

- 18 XX.1.3.2 Semantics of the service primitive

- 20 FEC\_UNITDATA.request(tx\_data-group<15:0>)

The data conveyed by FEC\_UNITDATA.request is a 16-bit vector representing a single data-unit that has been

prepared for transmission by the 10GBASE-KR PCS Transmit process.

# 25 XX.1.3.3 When generated

The 10GBASE-KR PCS sends tx\_data-group<15:0> to the FEC at a nominal rate of 644.53125MHz.

# 28 XX.1.3.4 Effect of receipt

Upon receipt of this primitive, the FEC Transmit process maps the data conveyed by the tx\_data unit<15:0> parameter into the payload of the transmitted FEC frame block stream, adds FEC overhead as required, scrambles the data, and transfers the result to the PMA via the PMA\_UNITDATA.request primitives.

# 33 XX.1.4 FEC\_UNITDATA.indication

This primitive defines the transfer of received data in the form of constant-width data-units from the FEC to the PCS. FEC\_UNITDATA.indication is generated by the FEC Receive process in response to FEC frame block data received from the PMA.

# 38 XX.1.4.1 Semantics of the service primitive

39

37

32

17

19

21

- 40 FEC\_UNITDATA.indication(rx\_data-unit<15:0>)

- 41

The rx\_data-unit<15:0> parameter is a 16-bit vector that represents the data-unit transferred by the FEC to the

10GBASE-KR PCS.

44

#### 45 XX.1.4.2 When generated

46 The FEC sends one rx\_data-unit<15:0> to the 10GBASE-KR PCS whenever it has delineated exactly 16 bits of

- 47 valid payload information from the incoming FEC data stream received from the PMA sublayer. The nominal rate

- 48 of generation of the FEC\_UNITDATA.indication primitive is 644.53125 Mtransfers/s.

49

# 50 XX.1.4.3 Effect of receipt

51 The effect of receipt of this primitive by the FEC client is unspecified by the FEC.

7

9

16

20

1

#### XX.1.5 FEC\_SIGNAL.indication

This primitive is sent by the FEC to the PCS to indicate the status of the Receive process. FEC\_SIGNAL.indication is generated by the FEC Receive process in order to propagate the detection of severe error conditions (e.g., no valid signal being received from the PMA sublayer) to the PCS.

### 6 XX.1.5.1 Semantics of the service primitive

8 FEC\_SIGNAL.indication(SIGNAL\_OK)

The SIGNAL\_OK parameter can take one of two values: OK or FAIL. A value of OK denotes that the FEC Receive process is successfully delineating valid payload information from the incoming data stream received from the PMA sublayer, and this payload information is being presented to the PCS via the FEC\_UNITDATA.indication primitive. A value of FAIL denotes that errors have been detected by the Receive process that prevent valid data from being presented to the PCS, in this case the FEC\_UNITDATA.indication primitive and its associated rx\_data-unit<15:0> parameter are meaningless.

#### 17 XX.1.5.2 When generated

18 The FEC generates the FEC\_SIGNAL.indication primitive to the 10GBASE-KR PCS whenever there is a change 19 in the value of the SIGNAL\_OK parameter.

#### 21 XX.1.5.3 Effect of receipt

22 The effect of receipt of this primitive by the FEC client is unspecified by the FEC.

23

#### 24 XX.2.1 FEC Principle of Operation

25

The FEC module uses Quasi Cyclic (QC) binary burst error correction code QC(2112, 2080) for error checking and forward error correction. The FEC block length of 2112 bits consists of 2080 bits of payload and 32 bits of overhead.

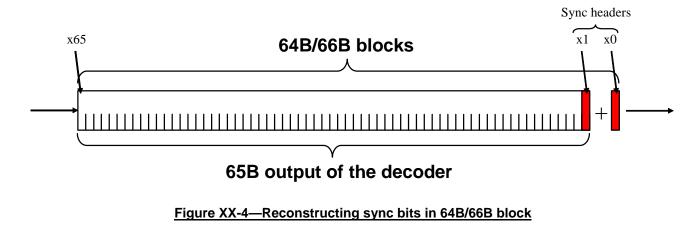

30 The FEC module uses 32 compressed sync bits from the 64b/66b encoded data of the PCS sublayer to add the parity check bits. The 10GBASE-KR 64b/66b PCS maps 64 bits of scrambled payload and 2 bits of unscrambled 31 32 sync header into 66-bit encoded blocks. The 2-bit sync header allows establishment of 64b/66b block boundaries by the PCS sync process. The sync header is 01 for data blocks and 10 for control blocks and always ensures 33 34 transition between the blocks to establish 64b/66b block boundaries. The FEC module compresses the 2 bits of 35 the sync header to 1 transcode bit. The transcode bit carries the state of 10GBASE-KR sync bits for the 36 associated payload. This is achieved by eliminating the 1st bit in 64b/66b block, which is also the first sync bit, and preserving the 2nd bit. The value of the 2nd bit defines the value of the removed 1st bit uniquely, since it is 37 38 always an inversion of the 1st bit on TX side. The transcode bits are further scrambled to ensure DC balance. The 39 error detection property of the binary burst code is used to establish block syncronization at FEC block boundaries 40 at the receiver. If decoding passes successfuly, the decoder produces 65 bits, the first decoded bit being the transcode bit. Then the 1st sync bit in 64b/66b code is constructed by the inversion of the transcode bit, and the 41 42 value of the 2nd sync bit is equal to the transcode bit.

43

44 The 16-bit data transmitted from the PCS gearbox function is FEC encoded and sent to the PMA sublayer, 45 similarly the 16-bit data received from the PMA sublayer is decoded back to 64b/66b blocks and sent to the PCS 46 block sync/receive function.

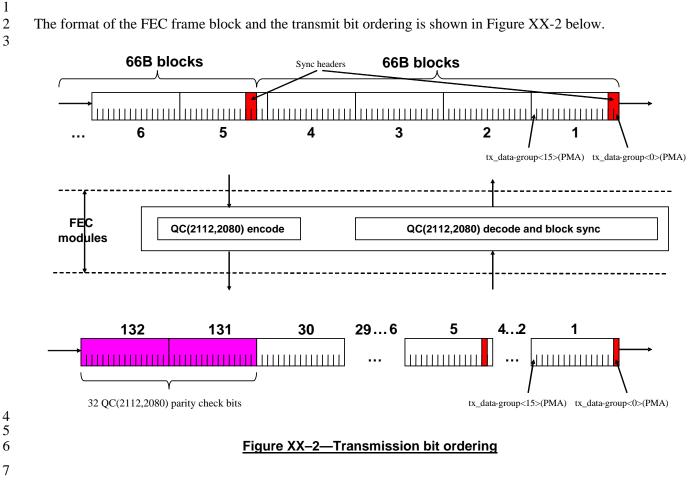

#### 48 XX.2.1.1 FEC block Format

49 The frame format for the FEC block is shown in table XX-1. The length of the FEC frame block is 2112 bits.

Each FEC frame block contains 32 rows of 65 bits each; 64 bits of payload and 1 bit transcoding overhead (T bits)

At the end of each frame block there is 32-bit overhead or parity check bits.

> 34 56 7

8 9

10

11

16

#### Table XX-1—FEC block frame format

| To                     | 64 Bit Payload Word O  | <b>T</b> <sub>1</sub>  | 64 Bit Payload Word 1  | T <sub>2</sub>         | 64 Bit Payload Word 2  | T <sub>3</sub>         | 64 Bit Payload Word 3  |

|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| T <sub>4</sub>         | 64 Bit Payload Word 4  | <b>T</b> <sub>5</sub>  | 64 Bit Payload Word 5  | <b>T</b> <sub>6</sub>  | 64 Bit Payload Word 6  | <b>T</b> <sub>7</sub>  | 64 Bit Payload Word 7  |

| <b>T</b> <sub>8</sub>  | 64 Bit Payload Word 8  | T,                     | 64 Bit Payload Word 9  | <b>T</b> <sub>10</sub> | 64 Bit Payload Word 10 | <b>T</b> <sub>11</sub> | 64 Bit Payload Word 11 |

| <b>T</b> <sub>12</sub> | 64 Bit Payload Word 12 | <b>T</b> <sub>13</sub> | 64 Bit Payload Word 13 | T <sub>14</sub>        | 64 Bit Payload Word 14 | <b>T</b> <sub>15</sub> | 64 Bit Payload Word 15 |

| <b>T</b> <sub>16</sub> | 64 Bit Payload Word 16 | T <sub>17</sub>        | 64 Bit Payload Word 17 | T <sub>18</sub>        | 64 Bit Payload Word 18 | <b>T</b> <sub>19</sub> | 64 Bit Payload Word 19 |

| T <sub>20</sub>        | 64 Bit Payload Word 20 | <b>T</b> <sub>21</sub> | 64 Bit Payload Word 21 | <b>T</b> <sub>22</sub> | 64 Bit Payload Word 22 | T <sub>23</sub>        | 64 Bit Payload Word 23 |

| T <sub>24</sub>        | 64 Bit Payload Word 24 | T <sub>25</sub>        | 64 Bit Payload Word 25 | T <sub>26</sub>        | 64 Bit Payload Word 26 | T <sub>27</sub>        | 64 Bit Payload Word 27 |

| T <sub>28</sub>        | 64 Bit Payload Word 28 | T <sub>29</sub>        | 64 Bit Payload Word 29 | T <sub>30</sub>        | 64 Bit Payload Word 30 | <b>T</b> <sub>31</sub> | 64 Bit Payload Word 31 |

32 parity bits

Total Block length =  $(32 \times 65) + 32 = 2112$  bits

# XX 2.1.2 Functions within FEC Module

The FEC comprises the FEC Encode block, Reverse Gearbox block, FEC decode block and FEC block synchronization.

12 The transmit data-units are sent from the FEC encoder to the PMA service interface via the 13 PMA\_UNITDATA.request primitive. When the transmit channel is in test-pattern mode, a test pattern is packed 14 into the transmit data-units that are sent to the PMA service interface via the PMA\_UNITDATA.request 15 primitive.

# 17 XX.2.1.2.1 FEC Encoder

The FEC encoder connects to the PCS Gearbox functions using the 16-bit tx\_data\_goup. The FEC encoder takes 32 64b/66b blocks from PCS and encodes it into single FEC block of 2112 bits, QC(2112, 2080). The FEC Encoder takes only one sync bit as a part of the message to encode and the second bit is removed. The sync bit sequence of 10 is encoded into 1 and sync bit sequence of 01 is encoded into 0. The resulting 32x65 = 2080 bits with the frame format as shown in Table XX-1 are fed to the encoder, which produces 32 parity-check bits and is appended at the end of the FEC frame block.

#### 25 XX.2.1.2.1.1 Reverse Gearbox function

The reverse gearbox adapts between the 66-bit width of the blocks and the 16-bit width of the PCS interface. It receives the 16-bit stream from the PCS interface and converts them back to 66-bit encoded blocks for the FCS Encoder to process. The reverse gerabox function operates in the same manner as the block sync function as defined in 49.2.9.

30

When the transmit channel is operating in normal mode, the reverse gearbox function receives data via

16-bit FEC\_UNITDATA.request primitive. It will form a bit stream from the primitives by concatenating

requests with the bits of each primitive in order to form tx\_data-group<0> to tx\_data-group<15> (see Figure 49–

6). It obtains lock to the 66-bit blocks in the bit stream using the sync headers and outputs 66-bit blocks. Lock is

obtained as specified in the block lock state machine shown in Figure 49–12.

36

37 The reverse gearbox functionality is necessary only when the optional PMA compatibility interface named XSBI

38 is implemented between the PCS and FEC functions, since that interface passes data via a 16-bit wide path.

39 When the XSBI is not implemented the internal data-path width between the PCS and PMA is an implementation 40 choice. Depending on the path width, the gearbox and reverse gearbox functionalities may not be necessary.

41

# 42 XX.2.1.2.1.2 FEC transmission bit ordering

- 6

- 7

- 8

- 9

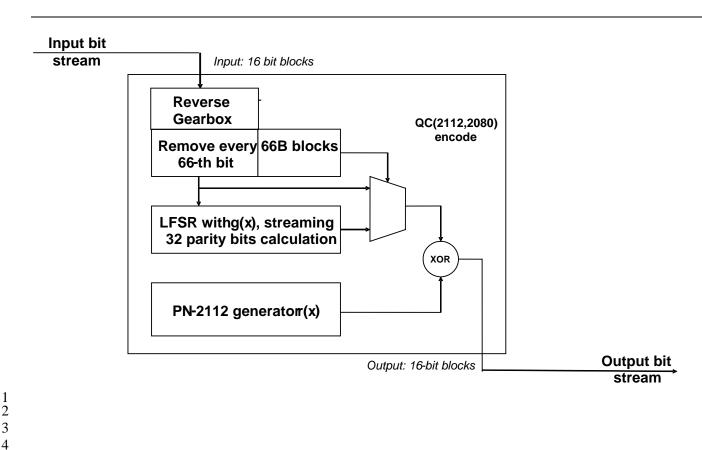

#### XX.2.1.2.1.3 FEC QC(2112,2080) Encoder 10

12 The block diagram of the FEC Encoder is illustrated in figure XX-3. The 32 x 65 bit payload blocks are encoded 13 by the QC(2112,2080) code. This code is linear quasi-cyclic code that can be encoded by generator polynomial g(x). The resulting payload block including the T bits is scrambled using the PN-2112 pseudo-noise sequence as 14 described in XX.2.1.2.1.3. 15

17 The generator polynomial g(x) for the QC(2112, 2080) parity-check bits is defined as given below.

20

16

$$g(x) = x^{32} + x^{23} + x^{21} + x^{11} + x^2 + 1,$$

21 then, if the polynomial representation of information bits is m(x), the codeword c(x) can be calculated in 22 systematic form as

$$r(x) = x^{32}m(x) \mod g(x),$$

$c(x) = r(x) + x^{32}m(x).$

25

24

(Multiplication on  $x^{32}$  is performed using shifts). Systematic form of the codeword means that first 2080 bits of 26 27 the codeword are information bits that can be extracted directly.

#### Figure XX-3-QC(2112,2080) encoding

# 7 8

10

17

19

21

25

5 6

# 9 XX.2.1.2.1.4 PN-2112 pseudo-noise sequence

The PN-2112 is the pseudo-noise sequence of length 2112 generated by the polynomial r(x) that is equal to the scrambler polynomial as defined in clause 49.2.6 with initial state  $S_{57}=1$ ,  $S_{i-1}=S_i$  XOR 1 or simply the binary sequence of 101010.... Before each codeword processing (encoding or decoding) the PN-2112 generator is initialized with this state of 101010..... The scrambling with PN-2112 sequence at the FEC codeword boundary is necessary for establishing FEC block syncronization (to ensure that any shifted input bit sequence will not be equal to another FEC codeword) and to ensure DC balance.

18

$$r(x) = 1 + x^{-39} + x^{-58}$$

(49-1)

# 20 XX.2.1.2.2 FEC Decoder

The FEC decoder establishes synchronization basing on repeated decoding of the received sequence. Decoding and error correction is performed after synchronization is achieved. There is a configuration option for the FEC decoder to indicate any decoding errors to the upper layer.

The FEC decoder recovers and extracts the information bits using the parity-check data. In case of successful decoding the decoder restores the sync bits in each of the 64B/66B blocks sent to the PCS function. When the decoder is configured to indicate decoding error, the decoder indicates error to the PCS by means of setting both sync bits in each of the 64B/66B block to the same value (11), thus forcing the above sublayer to consider this block as invalid.

3

4

5

6

When the receive channel is in normal mode of operation the FEC Synchronization process continuously monitors PMA\_SIGNAL.indicate(SIGNAL\_OK). When SIGNAL\_OK indicates OK the FCS Synchronization process accepts data-units via the PMA\_UNITDATA.indicate primitive. It attains block sychronization based on the decoding of FEC frame blocks and conveys received blocks to the PCS Receive process. The FEC Synchronization process sets the sync\_status flag to the PCS function to indicate whether the FEC has obtained synchronization.

- 7 8

- 9

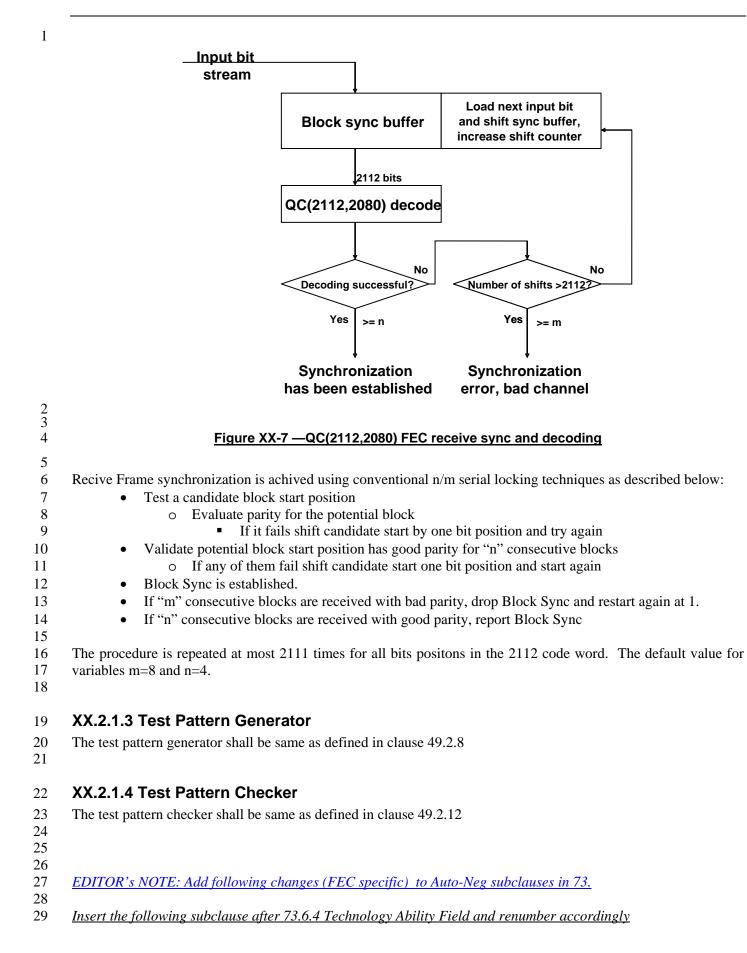

# 10 XX.2.1.2.2.1 QC(2112,2080) decoding

11

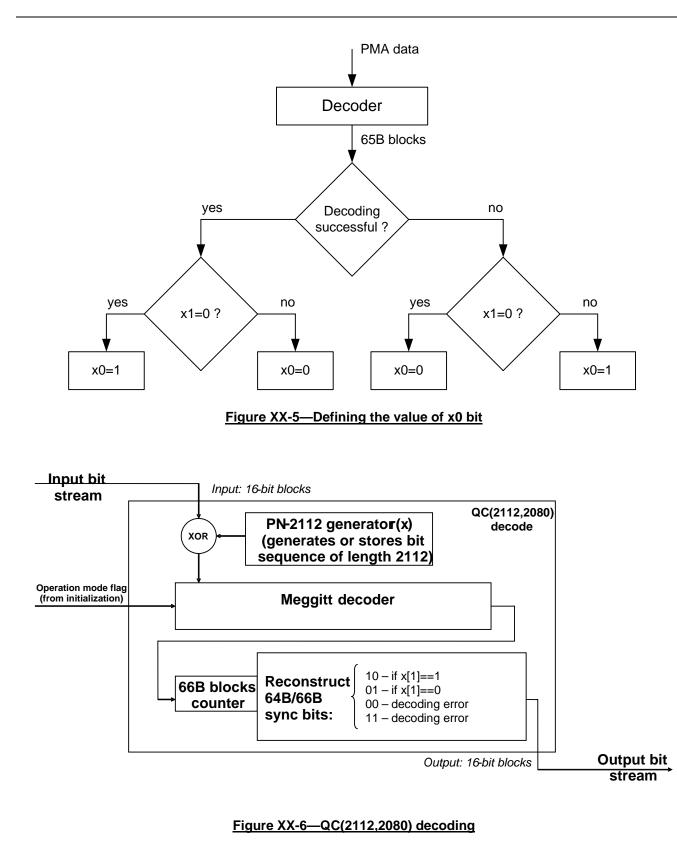

The FEC decoding scheme is shown in Figure XX-6. The decoder processes the 16-bit rx\_data\_group stream received from the PMA sublayer and descrambles the data using the PN-2112 pseudo-noise sequence as described in XX.2.1.2.1.4. The synchronization of 2112 bit FEC frame blocks is established using FEC decoding as describled in the flow diagram XX-4. Each row of the 32 65-bit data is extracted from the recovered FEC block and the 2 bit frame sync is reconstructed for the 64b/66b codes from the 1<sup>st</sup> bit as shown in Figures XX-4 and XX-5. Configuration option for FEC decoder is available to indicate error while reconstructing the removed sync bits based on normal condition or error condition:

reconstruct sync bits to be one of the possible combinations: "01" or "10", if decoding successful.

reconstruct sync bits to additional codes "00" and "11" if decoding error occurred.

This information corresponds to one complete (2112,2080) FEC frame block that is equal to 32 64B/66B code

blocks.

25

26 27 28

29

19

20

# 10 XX.2.1.2.2.2 FEC Block synchronization

11

12 The receive synchronization of FEC frame blocks is illustrated by the flow diagram in figure XX-7.

9

11

13

18

20

24

### 2 **73.6.6 FEC capability**

FEC (F0) is encoded in bit D47 of the base Link Code Word. The default value is logic zero. When the FEC capability bit F0 is set to logic one, it indicates that the FEC function is enabled for 10GBASE-KR PHY.

Since the Local Device and the Link Partner may have enabled the FEC bits differently the priority resolution

function is used to select the FEC modes in the device. The FEC is enabled on the link only if both ends advertise

the same status on the F0 bits.

- 10 EDITOR's NOTE: Add following changes (FEC specific) to subclauses in 45.

- 12 Insert the following row to table 45-53 in subclause 45.2.1.75 and renumber reserved bits as shown

- 14 Bit 1.150.15:24 Reserved Value always zero, writes ignored R/W

15

Bit 1.150.2 Enable FEC Error Indication

A write of 1 to this bit configures FEC decoder to indicate Error to the

16

upper layer

R/W

17 Bit 1.150.2 Enable FEC A write of 1 to this bit enables FEC in the 10GBASE-KR PHY R/W

19 Insert the following subclauses after 45.2.1.75.2 and renumber accordingly

# 21 45.2.1.75.3 Enable FEC (1.150.2) 22

23 This bit enables FEC for the 10GBASE-KR PHY in the Local Device

# 25 **45.2.1.75.4 Enable FEC Error Indication (1.150.2)**

26

27 <u>This bit enables the FEC decoder to indicate decoding errors to the upper layers (PCS) through the sync bits for</u>

28 the 10GBASE-KR PHY in the Local Device.