Thong Huynh Maxim Integrated Products

Thong Huynh IEEE802.3at Interim - Geneva May '07

### • Design Targets:

- Keep PSE switch (MOSFET) power dissipation to within its SOA

- Allows PSE to sustain port power (at reduced current) during transient over load condition

### • **PSE Requirements:**

- PSE port voltage range: 50V 57V

- PSE lport<sub>MAX</sub> = 720mA at 50V

- PSE Ilim<sub>MAX</sub> = 720mA x 400/350 = 823mA at 50V

- $\rightarrow$  PSE must provide at least 823mA at Vport = 50V

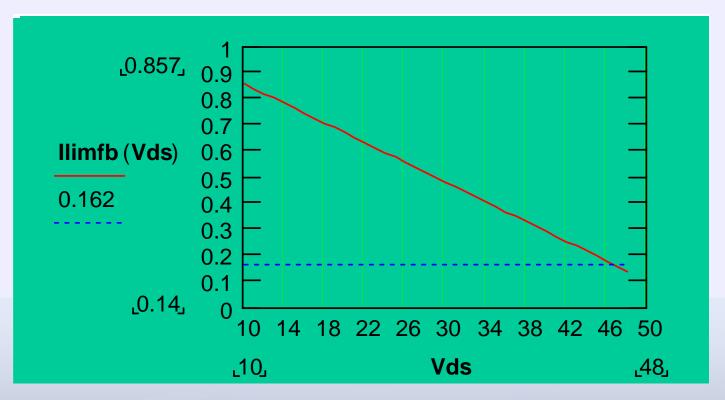

- $\rightarrow$  PSE can reduce its current limit (foldback) when Vport < 50V

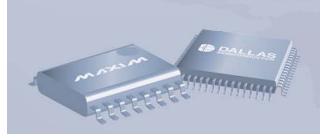

- → To control precisely the power dissipation in the MOSFET, it's better to specified the current limit foldback as a function of Vds.

Vds = Vps - Vport (neglect voltage drop across Rs) Vps = 57V maximum Vport = 50V minimum →Vds = 57V - 50V = 7V minimum before the controller can start folding back

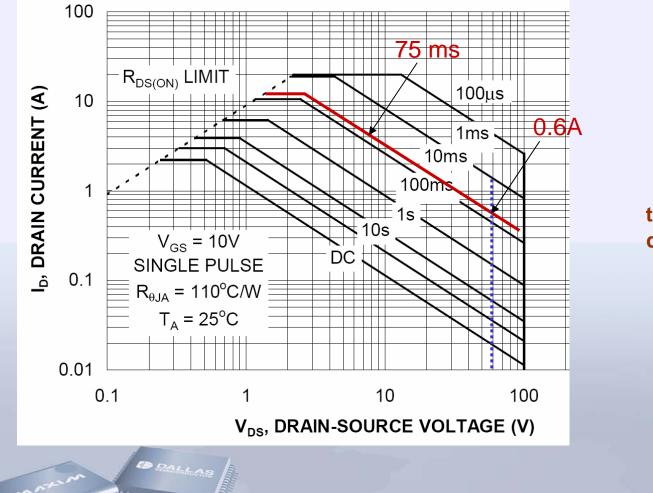

#### Maximum Safe Operation Area – 100V, 120m $\Omega$ MOSFET

This is roughly a constant power curve which limit this MOSFET power dissipation to ~30W for 75ms

**Example: PSE current limit as a linear function of Vds**

Thong Huynh IEEE802.3at Interim - Geneva May '07

DALLAS

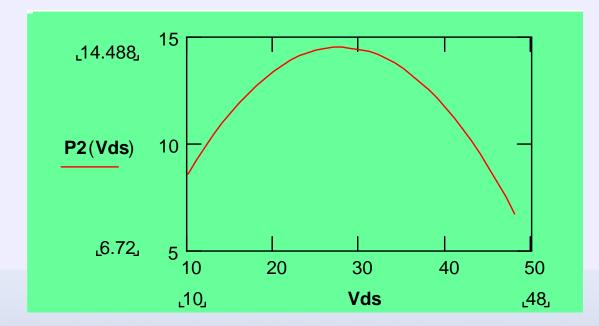

MOSFET power dissipation as a function of Vds. Peak power dissipation is 14.5W at Vds = 28V

Thong Huynh IEEE802.3at Interim - Geneva May '07

DALLAS

### • Summary:

- In a type 2 PSE, A simple current foldback implementation can help maintain the PSE MOSFET in its safe operating area.

- Current foldback allows the PSE to sustain port power during transient condition.

Thong Huynh IEEE802.3at Interim - Geneva May '07