# Vport ad hoc Current Limits May 2007

# Fred Schindler Cisco Systems

Andrew Smith Anoop Vetteth Bill Delveaux Brian Buckmeir Chad Jones **Christen Beia** Clay Stanford Dan Dove **Daniel Feldman** David Law David Lucia Derick Koonce Ferdinando Lari Frank Yung Fred Schindler Geoff Thompson Gianluca Sanità Helen Kastner Hugh Barrass James Blanc Jean Picard

**Power Integration Cisco Systems** Cisco Systems Bel Cisco Systems ST Microelectronics Linear Technology **HP Procurve Networking** Microsemi 3COM SIFOS Independent ST Microelectronics SystemX **Cisco Systems** Nortel Networks Nokia Siemens Network Cisco Systems **Cisco Systems** Indep. VC investigation **Texas Instruments**

Jeff Heath John Jetzt Keith Hopwood Ken Bennett Martin Patoka Matthew Landry Michael Altmann Pavlick Rimboim Ramesh Sastry Raul Lozano Riccardo Russo Sajol Ghoshal **Taufique Ahmed** Thong Nguyen Thuven Dinh Tim Parker Val Rybinski Wael Diab Yair Darshan Youhoa Xi

Linear Technology Avaya Phihong SIFOS Texas Instruments Silicon Labs Akros Silicon Microsemi Cisco Systems Pulse ST Microelectronics Akros Silicon Akros Silicon Maxim Pulse Nortel Networks Siemon Broadcom Microsemi National Semiconductor

Four ad hocs with an average attendance of 16 people since the last IEEE meeting. People that attended since the last IEEE meeting are shown in **bold**.

# Agenda

- SELV correction.

- Current limits.

- Next step.

#### **SELV** Correction

#### • IEC 60950, 3rd edition, 1999-04

1.2.13.4 DC VOLTAGE: The average value of a voltage (as measured by a moving coil meter) having a peak-to-peak ripple not exceeding 10 % of the average value.

#### • IEEE 802.3-2005, Table 33-6 PSE PI parameters

V\_open; Vpp; Min: 1.9 V; Max: 10% of the average value of  $V_{Port}$ , 44V <  $V_{Port}$  < 60V.

$57 + 2.85 = 59.85 \text{ V}, \sim 60 \text{ V}_{\text{peak}_{\text{value}}}$

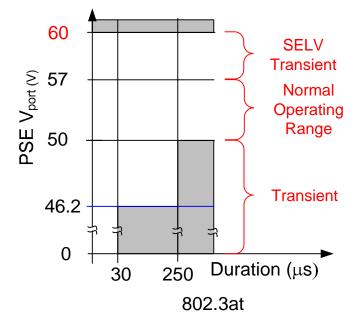

#### **Proposal corrected for SELV**

Propose a PSE PI voltage limit, for transients present more than 30 μS, of 7.6% below the PSE V<sub>port\_min</sub> level for less than a period of 250 μs and 10% above the V<sub>port\_max</sub> level.

Remove this text and continue using existing SELV guidance.

### **Motion**

#### Move that:

The IEEE 802.3at Task Force adopt presentation schindler\_5\_28\_07.pdf slides 4 to be incorporated in the next P802.3at draft.

- **M: Fred Schindler**

- S: Yair Darshan

| All Present | 802.3 Voters |  |

|-------------|--------------|--|

| For:        | For:         |  |

| Against:    | Against:     |  |

| Abstain:    | Abstain:     |  |

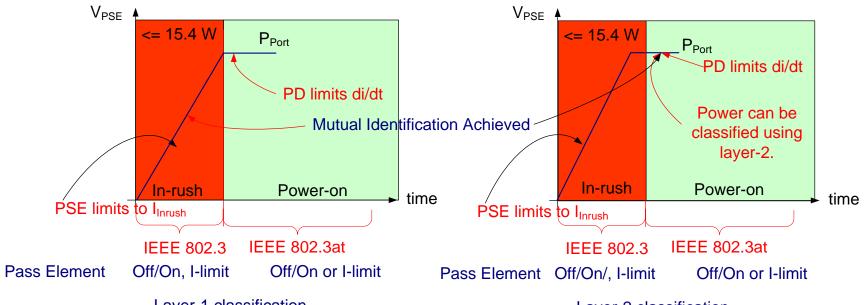

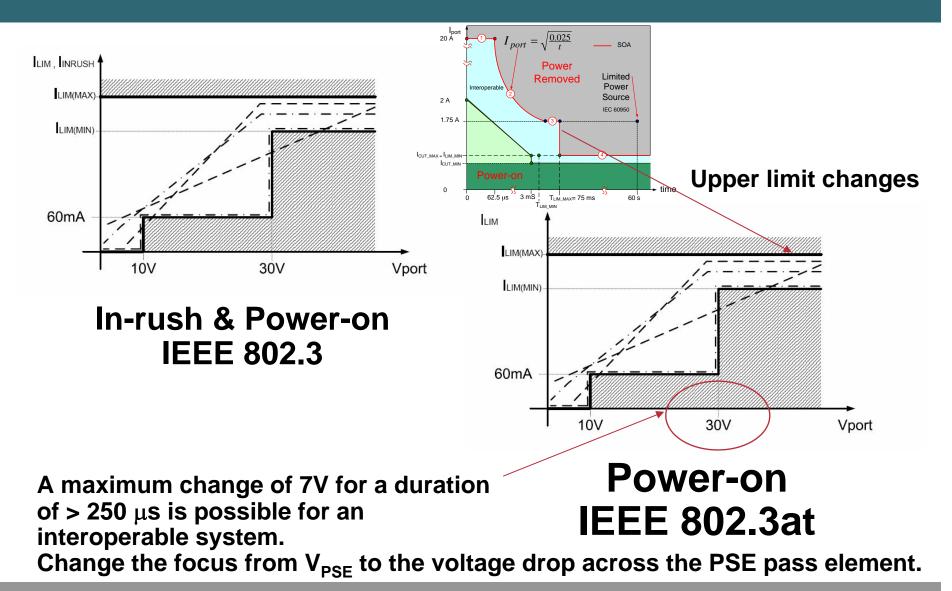

### **IEEE 802.3 vs IEEE 802.3at**

- The legacy standard reused the in-rush current limits to address the power-on current limits.

- The proposed IEEE 802.3at standard:

**Reuses the legacy in-rush current limits.**

Raises power-on currents.

Limits PD di/dt rates during power-on.

**Opens up the design space to allow:**

Scaled legacy current thresholds

Aggressive fold back

An energy based limit

#### **System In-rush and Power-on**

| Layer-1 | l classification |  |

|---------|------------------|--|

|---------|------------------|--|

Layer-2 classification

| Parameter        |      | 802.3                                                       | 802.3at |

|------------------|------|-------------------------------------------------------------|---------|

| I <sub>LIM</sub> | max. | $\frac{450}{400} \frac{400}{350} \frac{P_{Port}}{V_{Port}}$ |         |

|                  | min. | $\frac{400}{350} \frac{P_{Port}}{V_{Port}}$                 | New     |

|                  | max. | 350 V <sub>Port</sub>                                       |         |

| I <sub>CUT</sub> | min. | $rac{P_{Port}}{V_{Port}}$                                  |         |

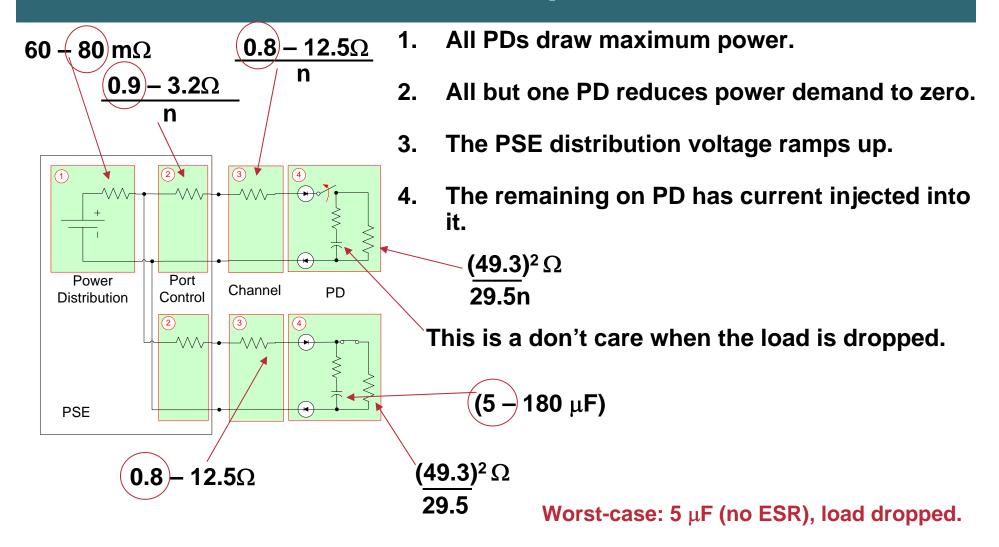

# System Concerns being addressed by I<sub>LIM</sub>

Situations that lead to a PSE dv/dt rate that causes excess PD current demand.

Multiple PDs reducing their load.

A PSE supply voltage change. ex/ Switching in a new power supply to deal with a power supply failure.

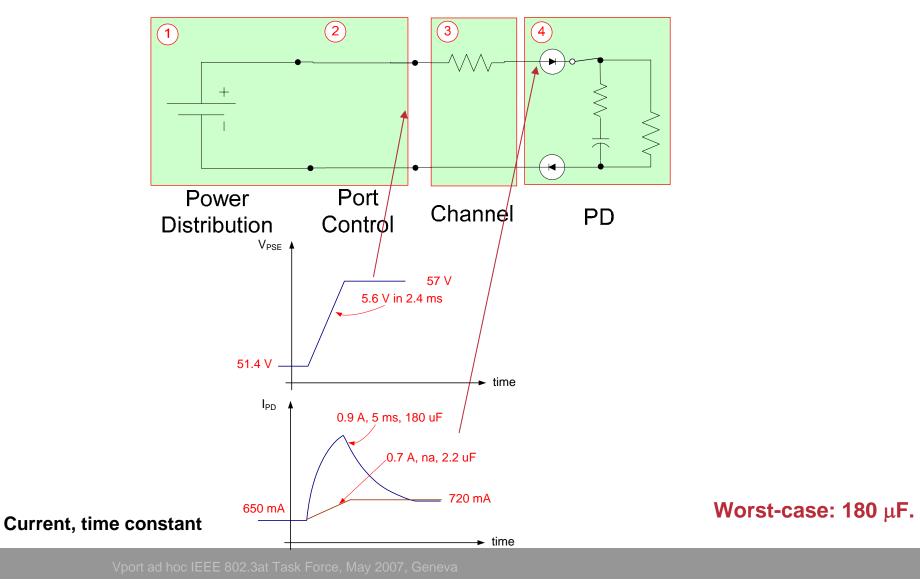

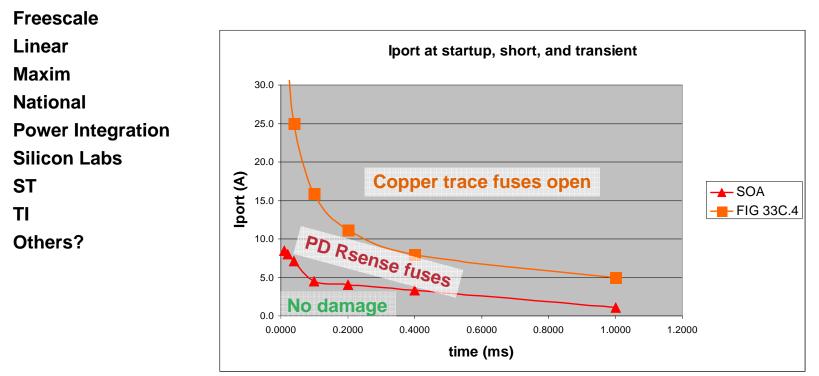

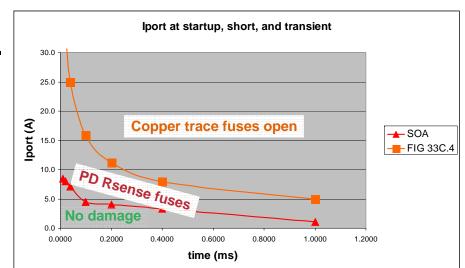

## **Collected Worst-case Current Limits**

Load drop: 47/48 ports, short channel 5  $\mu$ F, 29.5 W PD. PSE voltage ramp: short channel 180  $\mu$ F, 29.5 W PD.

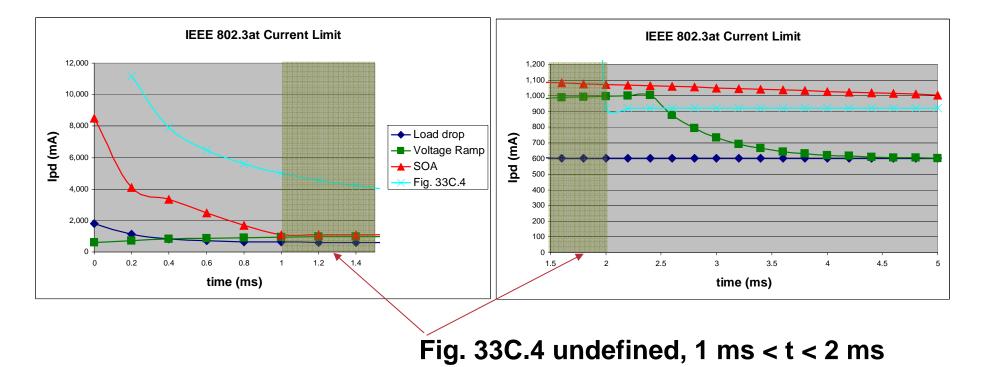

48 ports,  $R_{distribution} = 80 \text{ m}\Omega$ , Rport = 0.9  $\Omega$ ,  $R_{channel} = 0.8 \Omega$  (short),  $C_{PD_ON} = 5 \ \mu\text{F}$  (no ESR), SOA for 805 size resistor 1  $\Omega$  in parallel with 1  $\Omega$ , 1 A fuse (1.98 A<sup>2</sup>s), Generic NCH MOSFET,  $V_{DS} = 10 \text{ V} @ \text{I}_{D} = 14 \text{ A}$

## The SOA Curve is for a PD

Assumes a straw man PD.

This PD does not exist but could be created.

Using two 1  $\Omega$  resistors in parallel to sense current.

Most PD silicon vendors limit current at the PD.

# What Current Limit Should be used?

- Figure 33C.4?

- + Shorter peak current time.

- + A larger range of values supports the standard.

- Could damage a PD we are not aware of.

- PD Rsense SOA?

- + Interoperability with out damage.

- Longer time to transition the PD voltage.

- Tighter tolerances.

- 33.2.8.8 Output Current

Measurement after 1 ms .... See Figure 33C.4

Ad hoc 100% ok with Figure 33C.4 limit.

19 people

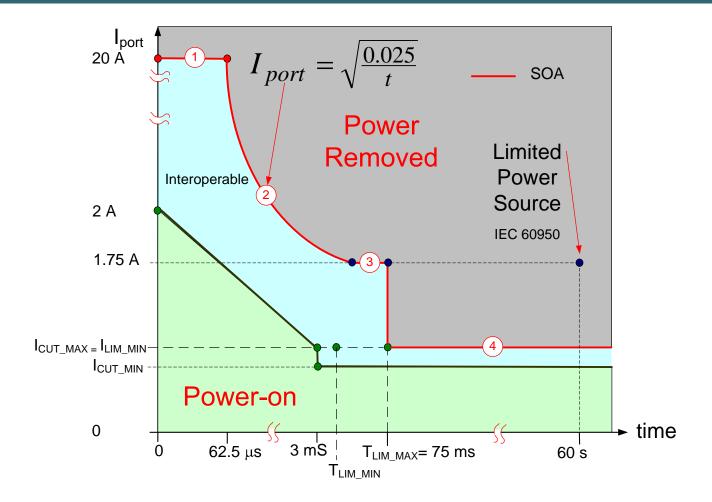

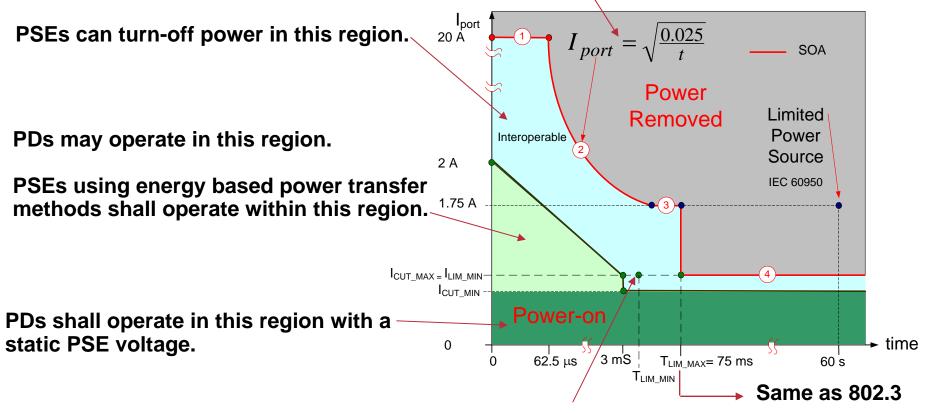

### **Power-on proposed compliance curve**

On Curve-2, 1.6 A @ t = 10.4 mS; 920 mA @ t = 29.5 ms.

# **Understanding the Current Limit Curve**

PSEs shall turn-off power before this region is entered.

PSEs may supply a constant current of  $I_{LIM}$  to this point to ensure interoperability. PSEs supplying a constant current of  $I_{LIM}$  shall operate to at least  $T_{LIM MIN}$ .

The light green boundary has 45% average margin above the simulated system needs.

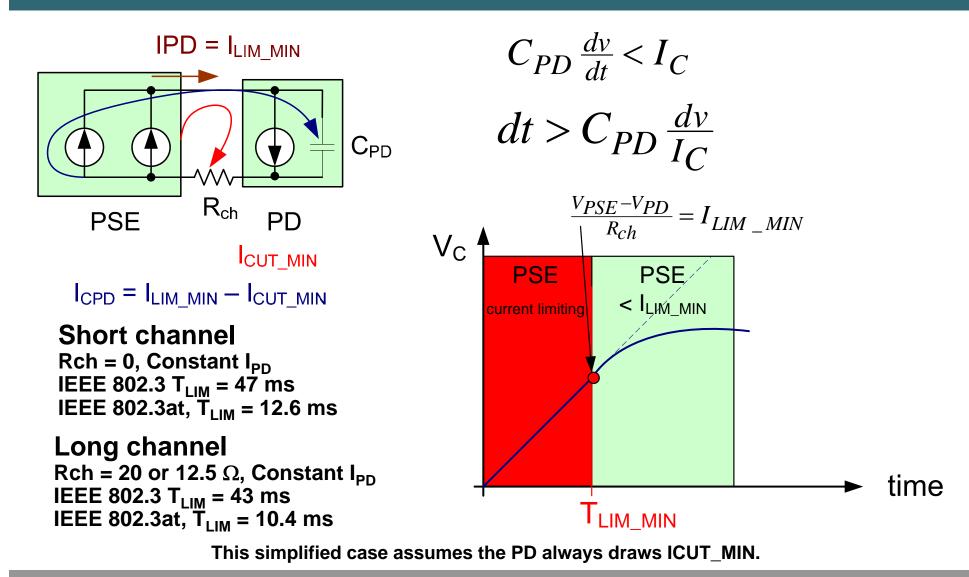

# **Simplified System in Current Limit**

#### **Simplified System in Current Limit**

Short channel Rch = 0, Constant  $I_{PD}$ IEEE 802.3  $T_{LIM}$  = 47 ms IEEE 802.3at,  $T_{LIM}$  = 12.6 ms

#### **IEEE 802.3**

$$T_{LIM} > C_{PD} \frac{dv}{I_C}$$

$T_{IIM} > 47ms$

$T_{LIM} > 180 \mu F \frac{57 - 44}{400 - 350}$

**IEEE 802.3at**

$T_{LIM} > 180 \mu F \frac{57-50}{820-720}$

$T_{LIM} > 12.6ms$

Long channel Rch = 20 or 12.5  $\Omega$ , Constant I<sub>PD</sub> IEEE 802.3 T<sub>LIM</sub> = 43 ms IEEE 802.3at, T<sub>LIM</sub> = 10.4 ms

$$\begin{split} dv_{MIN} &> R_{ch} I_{LIM} \\ dv_{MIN} &> 20\Omega \times 400 mA \\ dv_{MIN} &> 8V \\ V_{PSE} &= 57V, V_{PD} = 57 - 350 mA \times 20\Omega V = 49 \\ T_{LIM} &> 180 \, \mu F \, \frac{49 - 44 - 8}{400 - 350} \\ T_{LIM} &> 43 ms \end{split}$$

$dv_{MIN} > 12.5\Omega \times 820mA$   $dv_{MIN} > 10.3V$   $V_{PSE} = 50V, V_{PD} = 41V @ 720mA$   $V_{PSE} = 57V, V_{PD} = 48V @ 720mA$  $T_{LIM} > 180\mu F \frac{57-41-10.3}{820-720}$

93% of ad hoc okay this model (13/14).

$T_{LIM} > 10.4 ms$

## **IEEE 802.3 Concern**

- A PD can legally draw 400 mA for 50 ms. Table 33-12, Item 4.

- A system permitting this will not ensure interoperability when the PD is drawing its maximum allowable current and a PSE voltage transient occurs.

- Proposed Solution: Recommend that no more than I<sub>CUT\_MIN</sub> be drawn by a PD with a static port voltage.

IEEE 802.3at will use the correct value to begin with.

The previous IEEE Task Force may have allowed  $I_{CUT\_MAX}$  (PSE) to ensure circuits could accommodated this current value, but expected no more than  $I_{CUT\_MIN}$  to be drawn normally by the PD.

# **PSE SOA**

# **Next Step**

- The task force should review this proposal.

- Final ad hoc clean up.

- Motion to set this baseline will be made at the July Plenary.

#### Use Case: PSE load drop

A PSE providing 50 V at 600 mA with PDs consuming 29.5 W.

# Use Case: PSE power supply backup