# EEE Compatible MII/GMII Interface (revised)

May 2008 IEEE 802.3az Interim Meeting

Joseph Chou, Dachin Tseng, Albert Kuo Realtek Semiconductor Corp.

## **Supporters**

- ☐ Jim Barnette (Vitesse)

- ☐ Brad Booth (AMCC)

- Mandeep Chadha (Vitesse)

- ☐ Dan Dove (ProCurve Networking by HP)

- □ Paul Gyugyi (Nvidia)

- □ Robert Hays (Intel)

- □ Adam Healey (LSI)

- ☐ Brian Murray (LSI)

- Mario Träber (Infineon)

## **Purposes**

Revised version of chou\_02\_0508:

- □ Insert one cycle of clock before the end of LPI operating state

- □ Add MII registers to control the option to turn on and off interface clocks

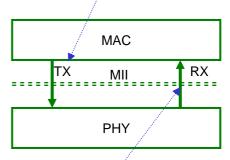

## Signals between MAC and PHY (MII)

| TX_EN | TX_ER | TXD<3:0>          | Indication                 |  |

|-------|-------|-------------------|----------------------------|--|

| 0     | 0     | 0000 through 1111 | Normal inter-frame         |  |

| 0     | 1     | 0000              | Reserved                   |  |

| 0     | 1     | 0001              | EEE Low Power IDLE         |  |

| 0     | 1     | 0010 through 1111 | Reserved                   |  |

| 1     | 0     | 0000 through 1111 | Normal data transmission   |  |

| 1     | 1     | 0000 through 1111 | Transmit error propagation |  |

| RX_DV | RX_ER | RXD<3:0>                             | Indication                 |  |

|-------|-------|--------------------------------------|----------------------------|--|

| 0     | 0     | 0000 through 1111 Normal inter-frame |                            |  |

| 0     | 1     | 0000                                 | Normal inter-frame         |  |

| 0     | 1     | 0001                                 | EEE Low Power IDLE         |  |

| 0     | 1     | 0010 through 1111                    | Reserved                   |  |

| 0     | 1     | 1110                                 | False Carrier indication   |  |

| 0     | 1     | 1111                                 | Reserved                   |  |

| 1     | 0     | 0000 through 1111                    | Normal data reception      |  |

| 1     | 1     | 0000 through 1111                    | Data reception with errors |  |

EEE\_LPI

Opcode from

MAC to PHY

EEE\_LPI

Opcode from

PHY to MAC

Note: From 802.3az Task Force Dove\_01\_0108.pdf Clause 22

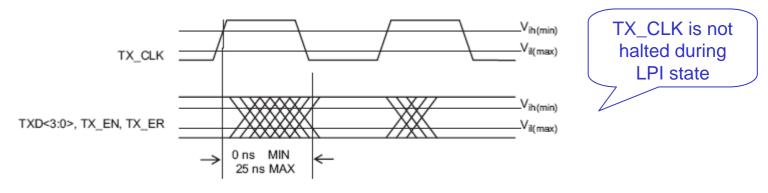

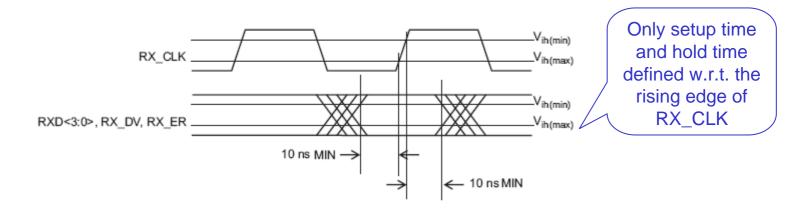

## Signal timing relationships at the MII

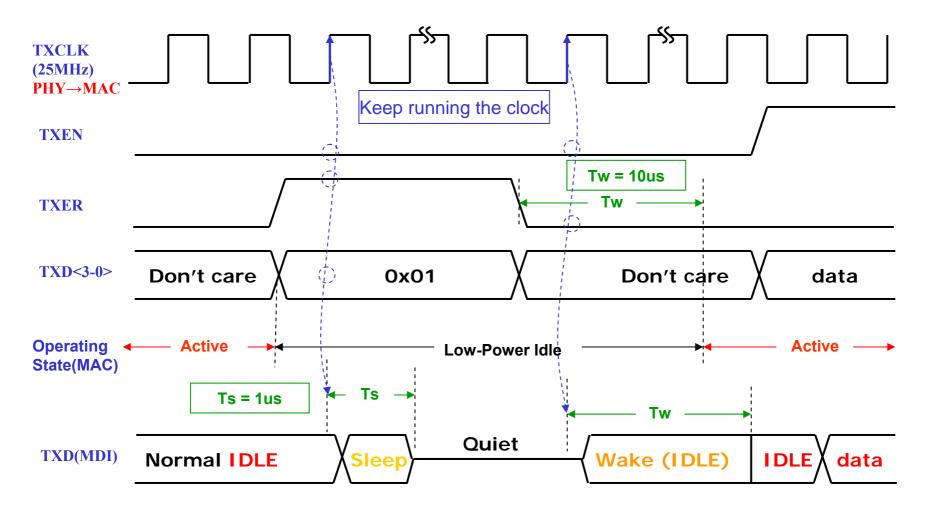

Figure 22-14—Transmit signal timing relationships at the MII

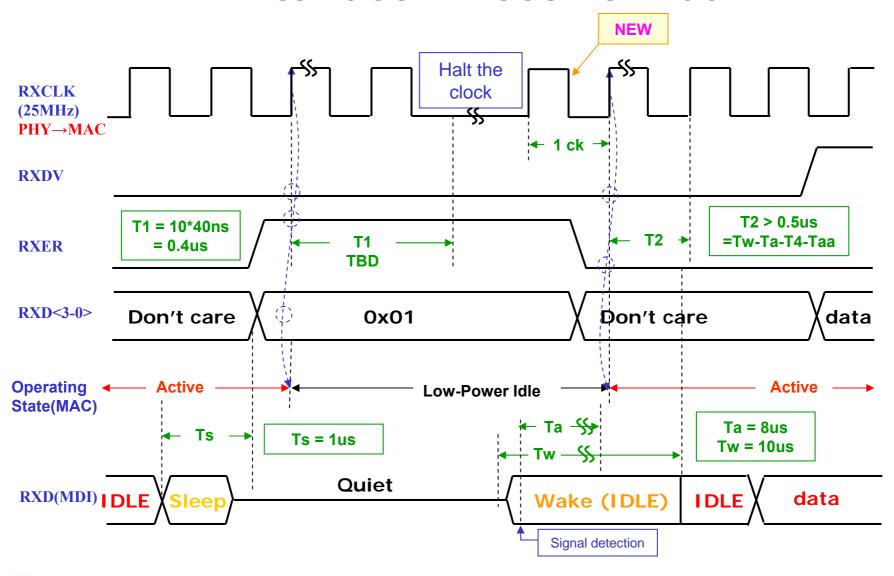

Figure 22-15—Receive signal timing relationships at the MII

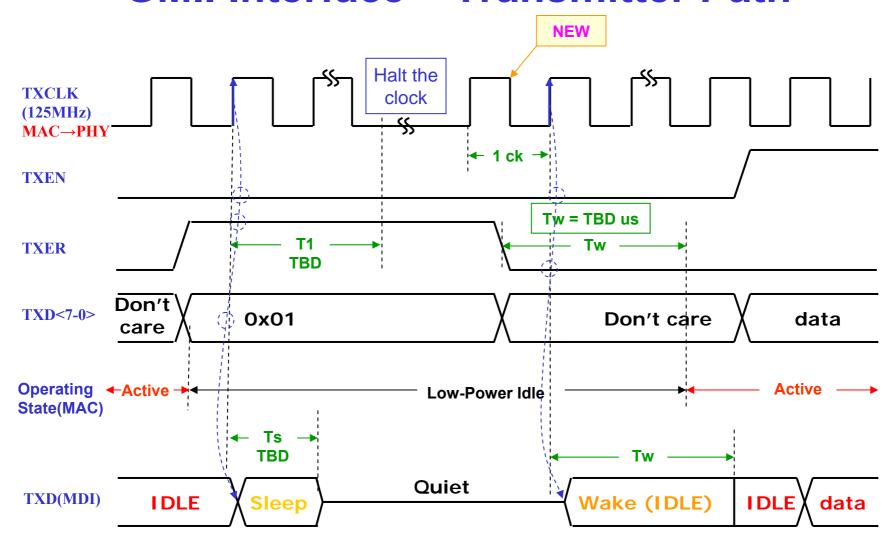

#### MII Interface – Transmitter Path

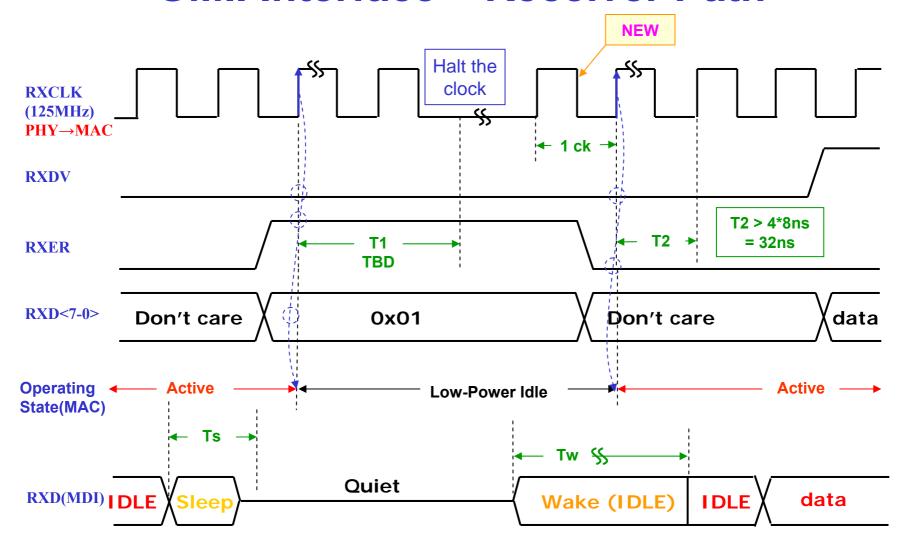

#### MII Interface – Receiver Path

## Signals between MAC and PHY (GMII)

| TX_EN        | TX_ER | TXD<7:0>      | Description        | PLS_DATA.request parameter    | EEE_LPI                                           |

|--------------|-------|---------------|--------------------|-------------------------------|---------------------------------------------------|

| 0            | 0     | 00 through FF | Normal inter-frame | TRANSMIT_COMPLETE             | Opcode from                                       |

| 0            | 1     | 00            | Reserved           | _                             | MAC to                                            |

| 0            | 1     | 01            | Low Power IDLE     | EEE Low Power IDLE            | PHY                                               |

| 0            | 1     | 02 through 0E | Reserved           | _                             |                                                   |

| 0            | 1     | 0F            | Carrier Extend     | EXTEND (eight bits)           |                                                   |

| <del> </del> |       | 1             |                    | +                             | MAC MAC                                           |

| RX_DV        | RX_ER | RXD<7:0>      | Description        | PLS_DATA.indication parameter | TX MII RX                                         |

| 0            | 0     | 00 through FF | Normal inter-frame | No applicable parameter       | [ <del>-                                   </del> |

| 0            | 1     | 00            | Normal inter-frame | No applicable parameter       | PHY                                               |

| 0            | 1     | 01            | Low Power IDLE     | EEE Low Power IDLE            |                                                   |

| 0            | 1     | 02 through 0D | Reserved           | _                             | EEE_LPI Opcode from                               |

Clause 35

PHY to MAC

Note: From 802.3az Task Force Dove\_01\_0108.pdf

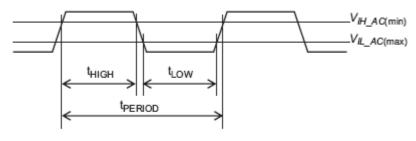

## Signal timing relationships at the GMII

Figure 35-17—GTX CLK and RX CLK timing parameters at receiver input

| $f_{FREQ}$          | GTX_CLK Frequency         | _ | 125 –<br>100 ppm | 125 +<br>100 ppm | MHz |

|---------------------|---------------------------|---|------------------|------------------|-----|

| tperiod             | GTX_CLK Period            | - | 7.50             | 8.50             | ns  |

| t <sub>PERIOD</sub> | RX_CLK Period             | - | 7.50             | -                | ns  |

| t <sub>HIGH</sub>   | GTX_CLK, RX_CLK Time High | - | 2.50             | -                | ns  |

| t <sub>LOW</sub>    | GTX_CLK, RX_CLK Time Low  | - | 2.50             | -                | ns  |

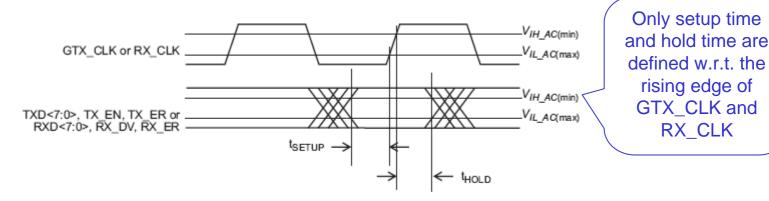

Needs to modify

Only setup time

defined w.r.t. the rising edge of

GTX CLK and

RX CLK

Figure 35-19—GMII signal timing at receiver input

IEEE 802.3az March 2008 Plenary Meeting

#### **GMII Interface – Transmitter Path**

#### **GMII Interface – Receiver Path**

## **Estimated Power Saving and Option**

**Power consumption:** Each clock pin consumes as much as 6mW to 25mW at 3.3V I/O power supply depending on the loading.

- ☐ For MII interface

- Only RXCLK can be turned off

- → saves 6~25mW

- ☐ For GMII interface

- Both RXCLK and TXCLK can be turned off

- → saves 12~50mW

NEW

## **Propose**

- □ Optionally halt the following clocks during Low Power Idle state:

- > RXCLK (from PHY to MAC) for MII interface

- > TXCLK (from MAC to PHY) for GMII interface

- > RXCLK (from PHY to MAC) for GMII interface

- ☐ Define new MII registers to enable or disable the on/off capability of MII/GMII clocks

- ➤ One control register (R/O) for TXCLK (for GMII)

- ➤ One control register (R/W) for RXCLK (for MII, GMII)

# Thank you

Questions?

# **Backup**

#### **Straw Poll**

□ Do you oppose halting clocks of MII and GMII interfaces during Low Power Idle operating state to save more power? (5/13/2008, 5 pm, Munich)

YES: 1

NO: 16

**ABSTAIN: 3**

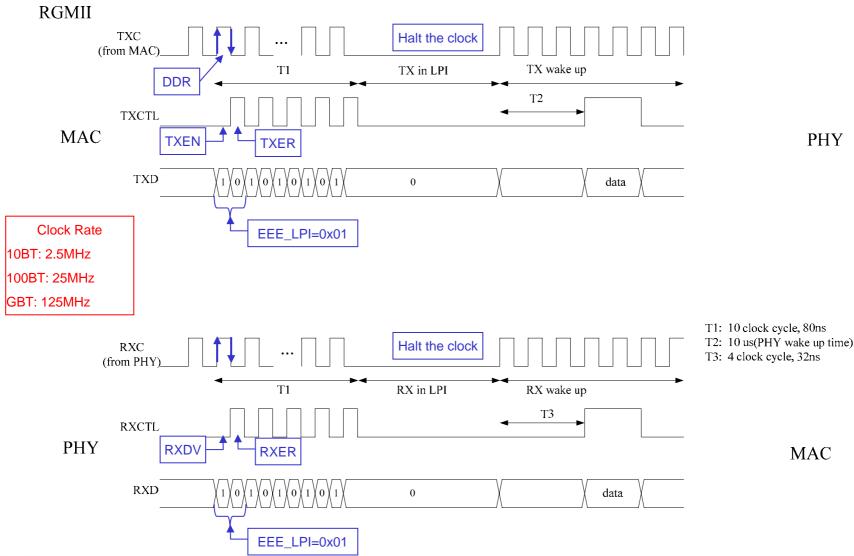

#### **RGMII Interface**

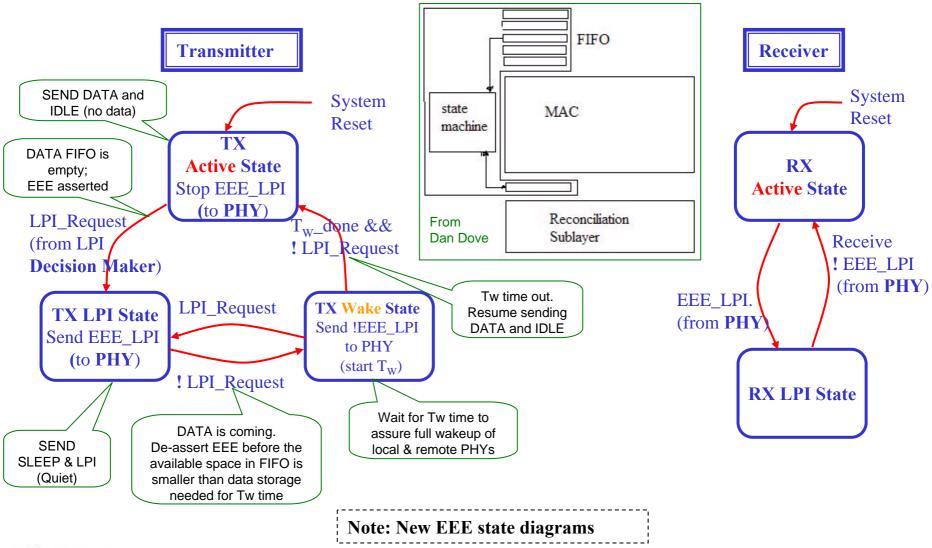

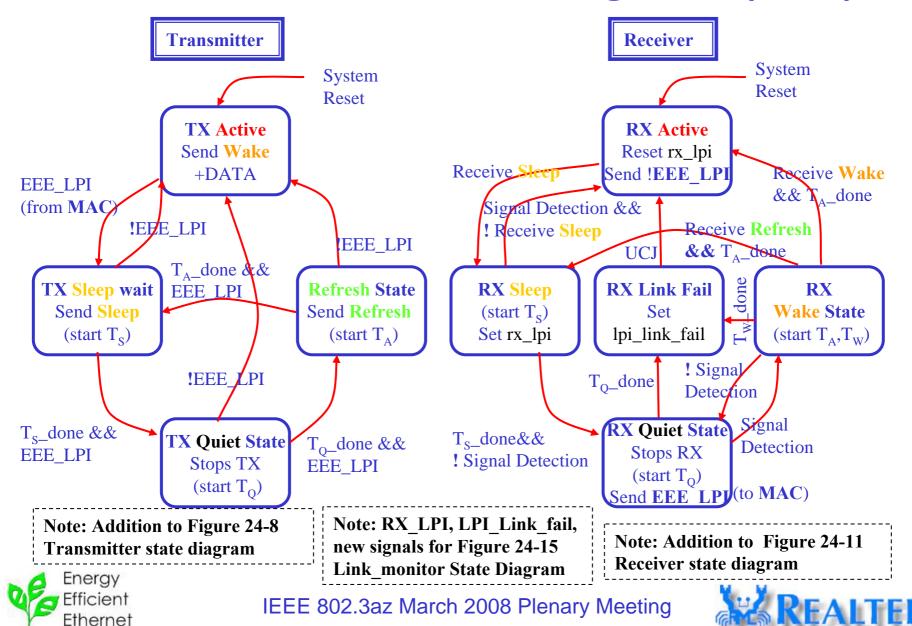

## 100BT LPI Line State Diagrams (PHY)

## 100BT LPI Operating State Diagrams (above PHY)