# **10GBASE-T EEE Synchronization**

11/11/2008 Gavin Parnaby

## **Supporters**

- George Zimmerman, Solarflare

- Brett McClellan, Solarflare

- Dimitry Taich, Teranetics

- Mike Grimwood, Broadcom

# Synchronization objectives

- Maximize the quiet time for best power savings

- Maximize predictability

- architecture optimization

- eliminate interoperability risk

- simplify validation

- simplify testing

- Ideally require no new signaling

- Stable; no link degradation due to corner cases of synchronization mechanism

#### **Proposed solution**

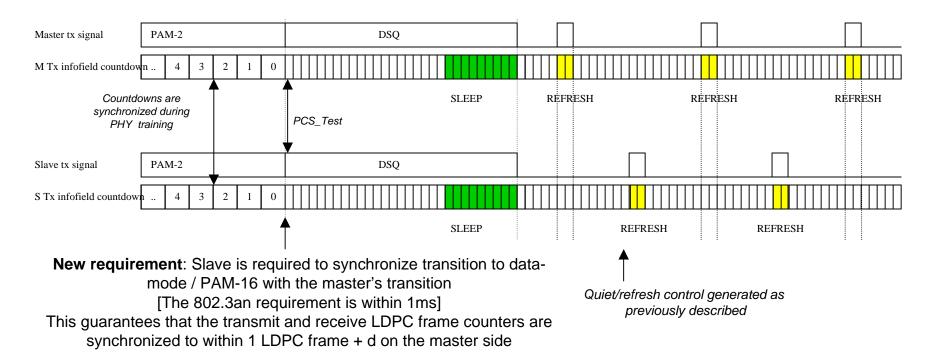

- Master and slave establish synchronization by using the transition to PAM-16 as a common reference

- PAM-2 infofield during initial training contains a counter that indicates the number of frames to the PAM-16 transition (state PCS\_Test, clause 55.4.2.5), for master and for slave

- Master sends infofields to slave indicating exactly when the transition to PAM-16 will happen on the master to slave side

- Slave sends infofields to master indicating exactly when the transition to PAM-16 will happen on the slave to master side

### **Proposed solution**

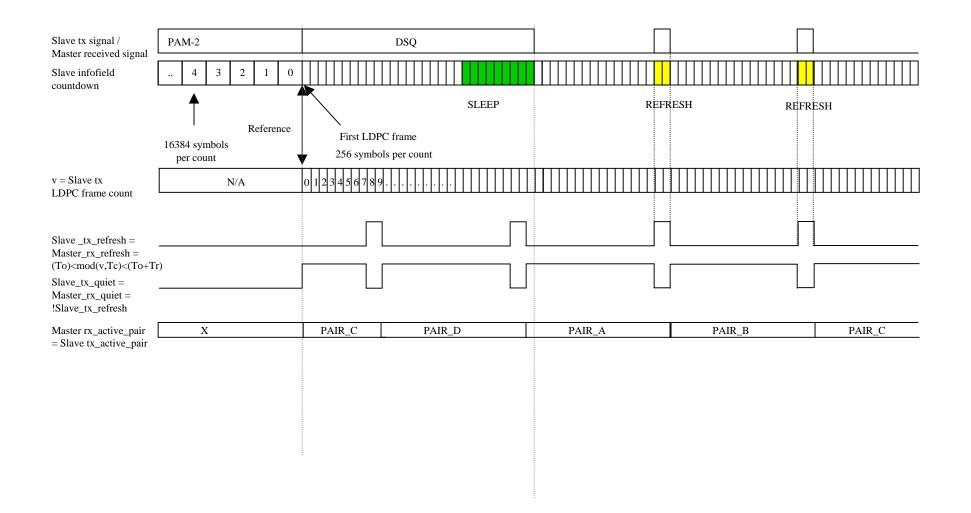

- Generate the refresh timing for both sides from fixed timing references

- Start tx LDPC frame counter when local phy transitions from training to data mode during initial training

- Start rx LDPC frame counter when LP transitions from training to data mode during initial training

- Active pair on both sides derived using simple modulo arithmetic from the appropriate counter

- Refresh\_active for both sides generated by simple modulo arithmetic from the appropriate counter

- Both PHYs know exactly when they send and receive refresh, and the active pair

- Following the PAM-16 transition event both sides know when refreshes are due, and which pair is active, with no ambiguity

# **Precise synchronization**

- Existing text requires only that master and slave countdowns are synchronized to within 1 PMA training frame [= 64 LDPC frames] [clause 55.4.5.14]

- This is not precise enough to ensure refreshes do not overlap

- New requirement that for EEE compliant PHYs, the slave synchronize its transition to PAM-16 to within 1 LDPC frame of the master, at the MDI

- Ensures that refresh offset is < 1 LDPC frame from ideal at the slave MDI</li>

- Ensures that refresh offset is < 3 LDPC frames from ideal at the master MDI

- Ample opportunity to do this during the countdown to PCS\_Test

# **Definitions**

- Tc = Tq + Tr

- The time for a complete quiet refresh cycle on a single pair

- To

- The desired offset time between the master and slave refresh signals

- U

- Master transmitted LDPC frame count, reset to 0 at master's Tx transition to PAM-16 at PCS\_Test

- V

- Slave transmitted LDPC frame count , reset to 0 at Slave's Tx transition to PAM-16 at PCS\_Test

### Assumptions

#### Use Tc=128, Tq+Tr=128

| Tr | Τq  |

|----|-----|

| 4  | 124 |

| 8  | 120 |

| 16 | 112 |

| 32 | 96  |

# **Generating logic**

|                   | Master Tx / Slave Rx   | Master Rx / Slave Tx                                                    |  |  |  |  |

|-------------------|------------------------|-------------------------------------------------------------------------|--|--|--|--|

| Refresh<br>active | Tq ≤ Mod (U,Tc)        | To ≤ Mod (V,Tc) < To+Tr                                                 |  |  |  |  |

| Pair A            | 0 ≤ Mod(U,4Tc) < Tc    | To+Tr ≤ Mod(V,4Tc) < To +Tr +Tc                                         |  |  |  |  |

| Pair B            | Tc ≤ Mod(U,4Tc) < 2Tc  | To +Tr +Tc ≤ Mod(V,4Tc) < To +Tr + 2Tc                                  |  |  |  |  |

| Pair C            | 2Tc ≤ Mod(U,4Tc) < 3Tc | To +Tr + 2Tc ≤ Mod(V,4Tc) < To +Tr + 3Tc                                |  |  |  |  |

| Pair D            | 3Tc ≤ Mod(U,4Tc) < 4Tc | To +Tr + 3Tc $\leq$ Mod(V,4Tc) $<$ 4Tc<br>OR 0 $\leq$ Mod(V,4Tc) $<$ To |  |  |  |  |

*U* = master transmit LDPC frame counter

V = master receive LDPC frame counter

Tc = Tq + Tr = 128; To = Tc/2 - Tr

# Tx\_mode control

- Lpi\_tx\_mode =

- NORMAL when !tx\_lpi\_active

- REFRESH\_A when tx\_lpi\_active \* (tx\_active\_pair==PAIR\_A \* tx\_refresh\_active)

- REFRESH\_B when tx\_lpi\_active \* (tx\_active\_pair==PAIR\_B \* tx\_refresh\_active)

- REFRESH\_C when tx\_lpi\_active \* (tx\_active\_pair==PAIR\_C

\* tx\_refresh\_active)

- REFRESH\_D when tx\_lpi\_active \* (tx\_active\_pair==PAIR\_D \* tx\_refresh\_active)

- QUIET when tx\_lpi\_active\* !tx\_refresh\_active

- ALERT when tx\_lpi\_active \* tx\_alert\_active

# Synchronization at slave

| Master tx signal /<br>Slave received signal                                                                                  | PAM-2                                   | DSQ                                       |        |         |       |        |         |

|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------|--------|---------|-------|--------|---------|

| Master infofield<br>countdown                                                                                                | 4 3 2 1 0                               |                                           |        |         |       |        |         |

|                                                                                                                              | Reference<br>16384 symbols<br>per count | First LDPC frame<br>256 symbols per count | SLEEP  | REFRESH | REFRE | SH     | REFRESH |

| u = Master tx<br>LDPC frame count                                                                                            | N/A                                     | 0 1 2 3 4 5 6 7 8 9                       |        |         |       |        |         |

| Master_tx_refresh =<br>Slave Rx_refresh =<br>Tq ≤ Mod (u,Tc)<br>Master_tx_quiet =<br>Slave Rx _quiet =<br>!Master_tx_refresh |                                         |                                           |        |         |       |        |         |

| Master tx_active_pair =<br>Slave rx_active_pair                                                                              | N/A                                     | PAIR_A                                    | PAIR_B | PA      | IR_C  | PAIR_D | PAIR_A  |

|                                                                                                                              |                                         |                                           |        |         |       |        |         |

|                                                                                                                              |                                         | :                                         |        |         |       |        |         |

# Synchronization at master

FS-8B

# Synchronization between master and slave

- Each PHY has a Tx LDPC frame counter, and an Rx LDPC frame counter

- The Tx LDPC frame counter is reset when the transmit signal transitions to data mode

- The Rx LDPC frame counter is reset when the receive signal transitions to data mode

- Transmit and receive refresh periods are deterministic thereafter, on both sides

### **Further details**

- Refreshes that begin during SLEEP are not transmitted

- To eliminate partial refreshes that overlap with SLEEP

- Means that LPI state always begins with quiet or full refresh

### **Advantages**

- Quiet / refresh is completely predictable on both sides

- Can bound refresh offset to a very small number of frames on both sides

- Easily testable

- Only requirement is slave countdown synchronization

- Potential for higher power savings due to predictable power downs

- Method achieves robust synchronization without introducing new signaling

- Key variables are deterministic on both sides throughout