# Proposed Modifications to IEEE P802.3az/D0.9 Clause 40

Adam Healey, Niall Fitzgerald, Jacobo Riesco, Brian Murray LSI Corporation

IEEE P802.3az Task Force Meeting Seoul, KR September 2008

#### **Motivation**

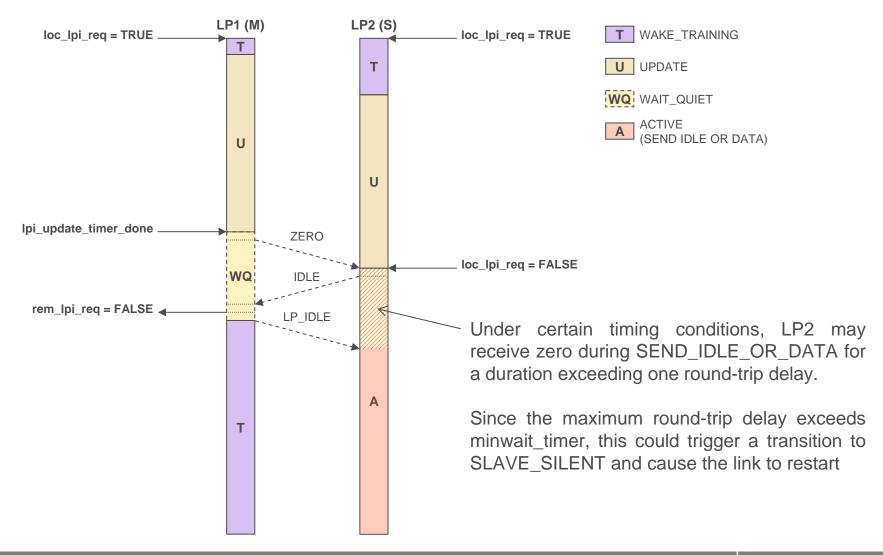

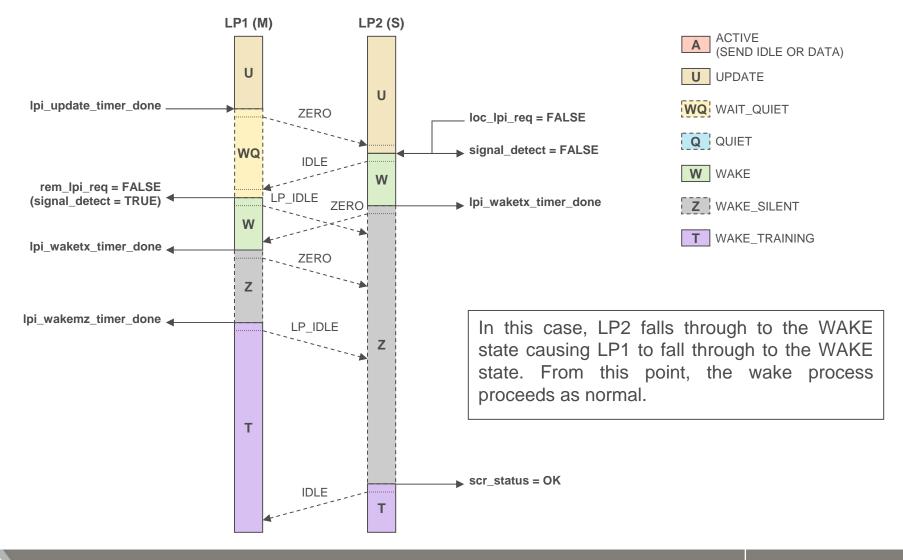

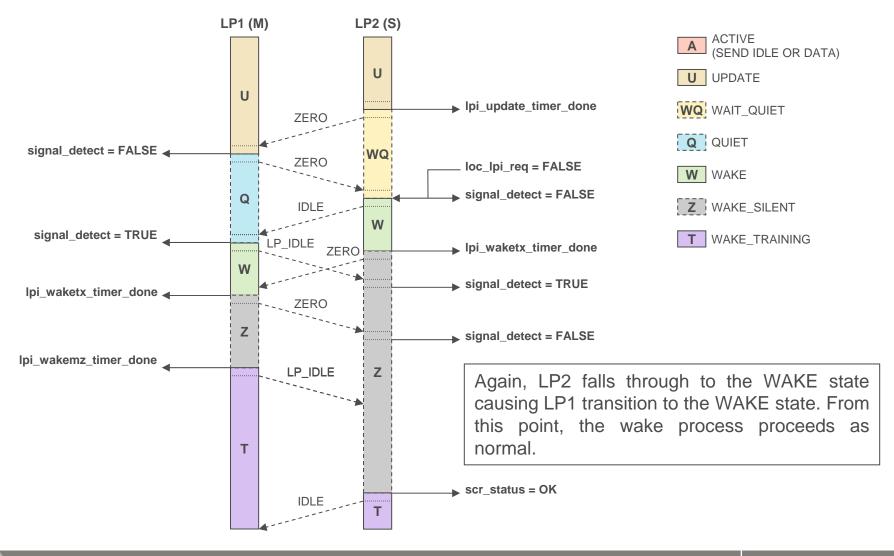

- It has been pointed out\* that, per the current PHY Control state diagram, there is a possibility that the local device could receive zero during SEND IDLE OR DATA when the local device de-asserts loc\_lpi\_req during UPDATE but the link partner transitions to WAIT\_QUIET prior to receiving the notification

- Under certain timing conditions, the duration of zero could be on the order of the round-trip delay, leading to a link restart

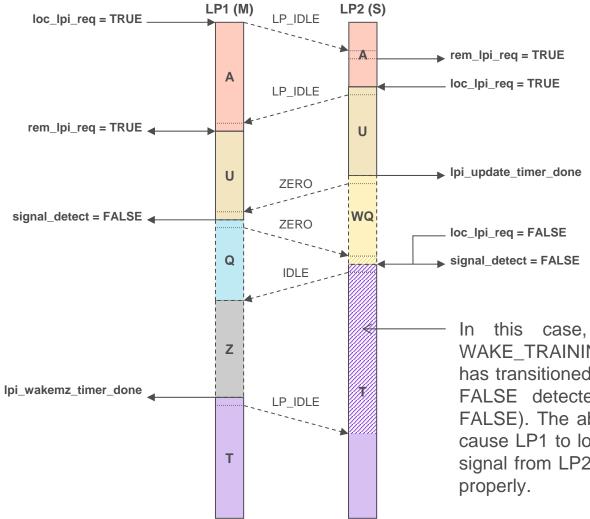

- It has also been pointed out\* that there is a possibility that the SLAVE can bypass the WAKE\_SILENT state and cause the WAKE process to fail

- Finally, it has been pointed out that the roles of SLEEP and UPDATE are similar so they may be consolidated into a single state

- This is reinforced by the fact that lpi\_sleep\_timer has recently been assigned a range similar to lpi\_update\_timer

\* Joseph Chou, Realtek

#### Before we begin...

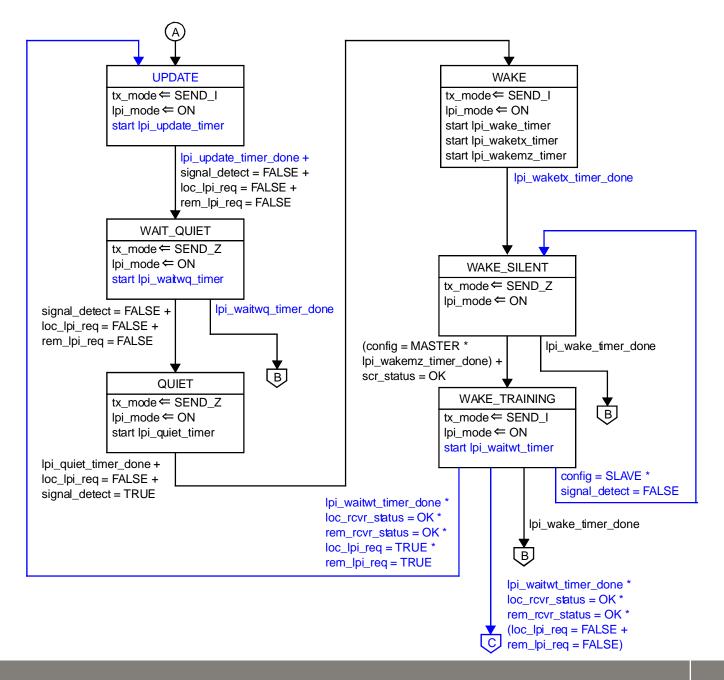

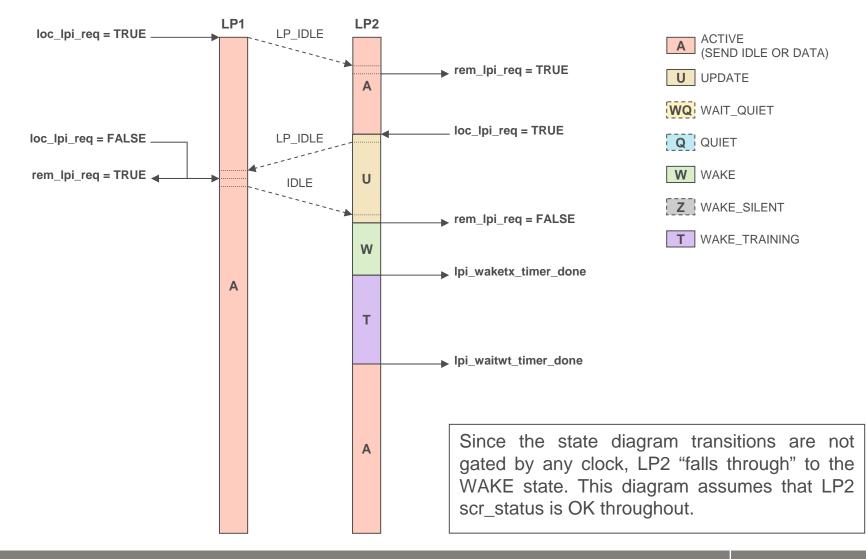

- State diagram transitions are not gated by a clock and it is possible to instantaneously "fall through" states

- For example, starting at UPDATE...

- signal\_detect = FALSE causes fall through to QUIET

- loc\_lpi\_req = FALSE causes fall through to WAKE

- Interpreting the state machine in this way leads one to the conclusion that Case 1 in chou\_01\_0908.pdf is not an issue

#### chou\_01\_0908: Case 2

IEEE P802.3az Task Force

LSI 🖧

In this case, LP2 falls through to the WAKE\_TRAINING state before it realizes LP1 has transitioned to QUIET (e.g. signal\_detect = FALSE detected slightly after loc\_lpi\_req = FALSE). The absence of signal from LP1 may cause LP1 to lose timing while the presence of signal from LP2 may prevent LP1 from training properly.

# **Corrective actions**

- Refer to the proposed state diagram in the next slide...

- Note changes recommended in grimwood\_01\_0908.pdf included for completeness

Healey 9/15/2008

IEEE P802.3az Task Force

LSI 🖧

# **Supporting edits**

- 40.4.2.4: Upon activation of the low power mode, the PHY Control asserts tx\_mode = SEND\_I for period of time defined by <a href="http://pi\_sleep\_timerlpi\_update\_timer">http://pi\_sleep\_timerlpi\_update\_timer</a> which allows the remote PHY to prepare for the transition to the WAIT\_QUIET state. When <a href="http://pi\_sleep\_timerlpi\_update\_timer">http://pi\_sleep\_timerlpi\_update\_timer</a> expires, PHY Control asserts tx\_mode = SEND\_Z and transmission ceases.

- 40.4.5.2: Delete lpi\_sleep\_timer

- **40.4.5.2**: Replace lpi\_wait\_timer with lpi\_waitwt\_timer

This timer defines the minimum time the PHY must remain in the WAKE\_TRAINING state.

Values: The condition lpi\_waitwt\_timer\_done becomes true upon timer expiration.

Duration: This timer shall have a period between 1.8 µs and 2.0 µs.

# **Supporting edits (continued)**

• 40.4.5.2: Add lpi\_waitwq\_timer

This timer defines the maximum time the PHY will dwell in the WAIT\_QUIET state before forcing the link to restart.

Values: The condition lpi\_waitwq\_timer\_done becomes true upon timer expiration.

Duration: This timer shall have a period between 4.5  $\mu$ s and 5.0  $\mu$ s.

IEEE P802.3az Task Force

10

LSI

Healey 9/15/2008

IEEE P802.3az Task Force

LSI 🎇

Healey 9/15/2008

IEEE P802.3az Task Force

LSI 🖧

# **Questions?**