| <b>#</b><br>1 | Item<br>Document Outline | <b>Details</b><br>Move to adopt the draft outline, based on slides 3 thru 7 of<br>"ganga_02_0508.pdf" as the basis for the first draft of P802.3ba.                                                                                                                       | Motion<br>#1 of May 2008 | Reference File<br>http://grouper.ieee.org/groups/802/3/ba/public/may08/ganga_02_0508.pdf |

|---------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------|

| 2             | Nomenclature             | Move to adopt the nomenclature, based on slide 8 of<br>"ganga_02_0508.pdf" as the basis for the first draft of P802.3ba                                                                                                                                                   | <u>#2 of May 2008</u>    | http://grouper.ieee.org/groups/802/3/ba/public/may08/ganga_02_0508.pdf                   |

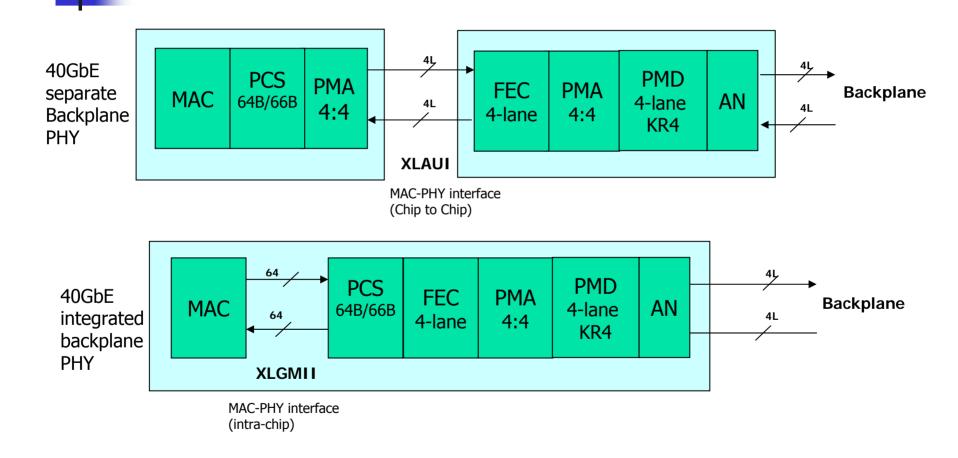

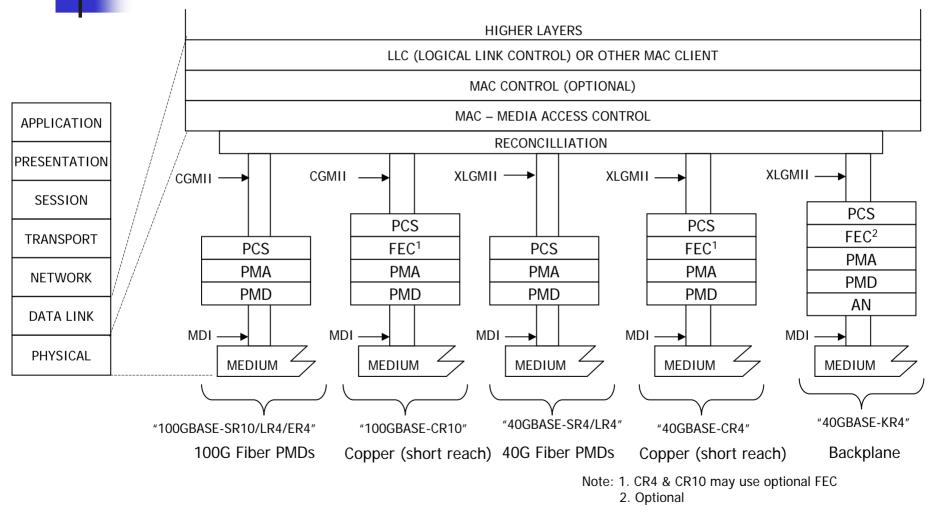

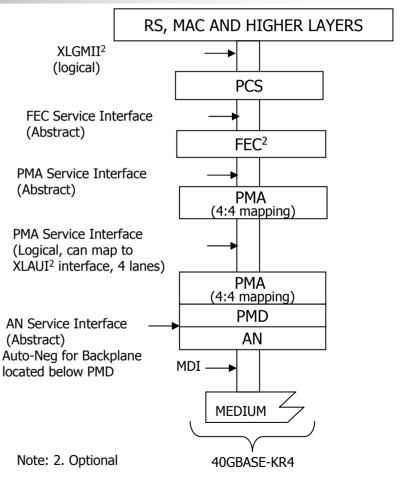

| 3             | Architecture             | Move that the 802.3ba Task Force adopt slides 4 thru 9 as the 40/100G architecture as proposed in "ganga_01_0508.pdf" with the inclusion of an optional n-lane x 10.3125GBd electrical interface for PMD service interface (to slides 5,6, and 9), as baseline.           | <u>#3 of May 2008</u>    | http://grouper.ieee.org/groups/802/3/ba/public/may08/ganga_01_0508.pdf                   |

| 4             | XLGMII / CGMII           | Move to adopt "gustlin_02_0508.pdf" as the baseline for the XLGMII and CGMII logical interfaces.                                                                                                                                                                          | <u>#4 of May 2008</u>    | http://grouper.ieee.org/groups/802/3/ba/public/may08/gustlin_02_0508.pdf                 |

| 5             | PCS                      | Move to adopt "gustlin_01_0508.pdf" as the baseline for the 40GbE and 100GbE PCS.                                                                                                                                                                                         | <u>#5 of May 2008</u>    | http://grouper.ieee.org/groups/802/3/ba/public/may08/gustlin_01_0508.pdf                 |

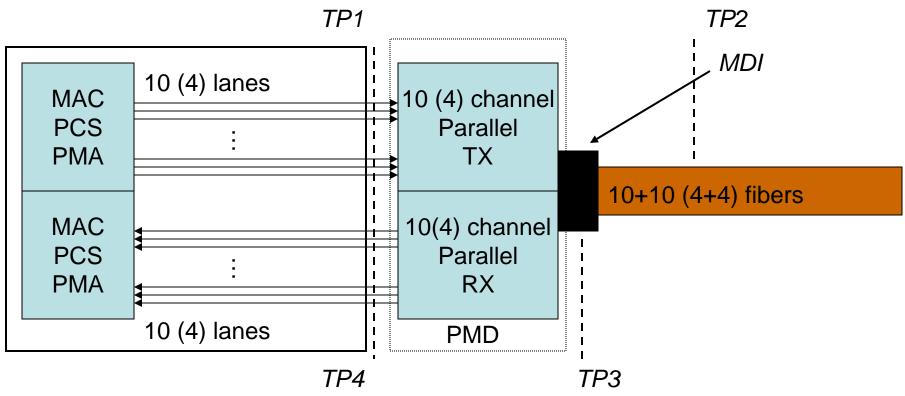

| 6             | MMF PMD                  | Move that the 802.3ba Task Force adopt the parallel PMD proposal<br>and tables on pages 6, 8, 9 and 10 of (pepeljugoski_01_0508) as the<br>baseline proposal of the work of the task force towards writing the first<br>draft standard for 40GBASE-SR4 and 100GBASE-SR10. | <u>#6 of May 2008</u>    | http://grouper.ieee.org/groups/802/3/ba/public/may08/pepeljugoski_01_0508.pdf            |

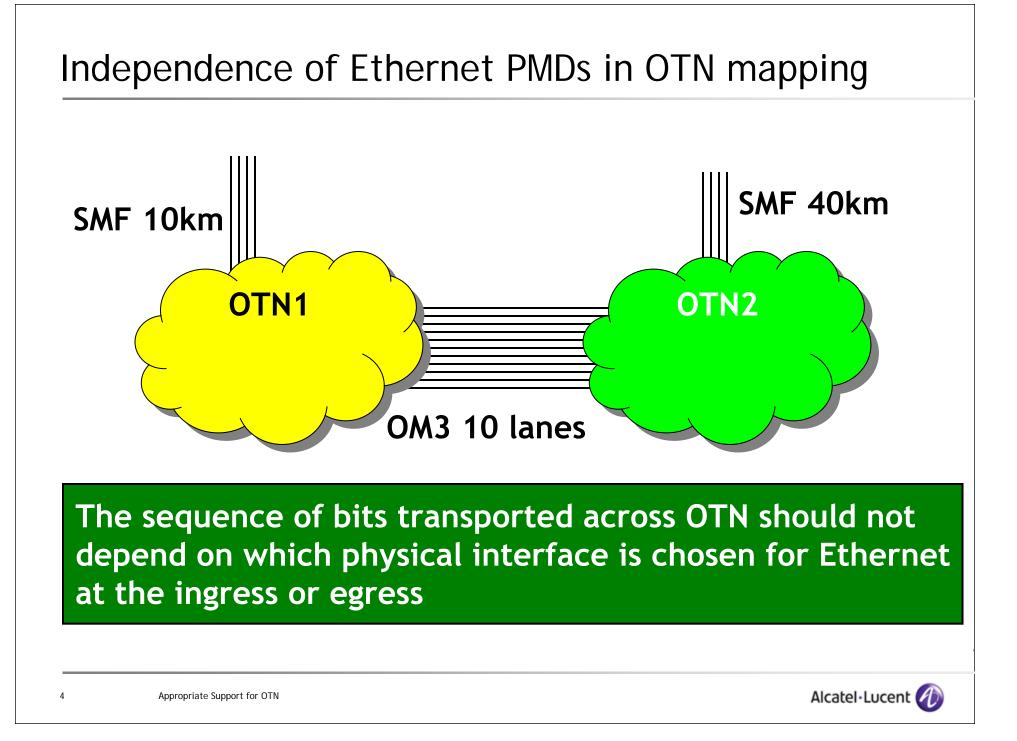

| 7             | OTN Compatibility        | Move to adopt "trowbridge_01_0508.pdf" as the baseline for the "Appropriate support for OTN" with the inclusion of "and pending concurrence of the 802.3 working group" prior to the last bullet of slide 11.                                                             | <u>#8 of May 2008</u>    | http://grouper.ieee.org/groups/802/3/ba/public/may08/trowbridge_01_0508.pdf_             |

| 8             | 100GE 40KM PMD           | Move to adopt 4x25G LAN WDM (as per cole_02_0508) as the baseline proposal for the 100GE 40km SMF PMD.                                                                                                                                                                    | <u>#12 of May 2008</u>   | http://grouper.ieee.org/groups/802/3/ba/public/may08/cole_02_0508.pdf                    |

| 9             | 100GE 10KM PMD           | Move to adopt 4x25G LAN WDM (as per cole_01_0508) as the baseline proposal for 100GE 10km SMF PMD.                                                                                                                                                                        | <u>#15 of May 2008</u>   | http://grouper.ieee.org/groups/802/3/ba/public/may08/cole_01_0508.pdf                    |

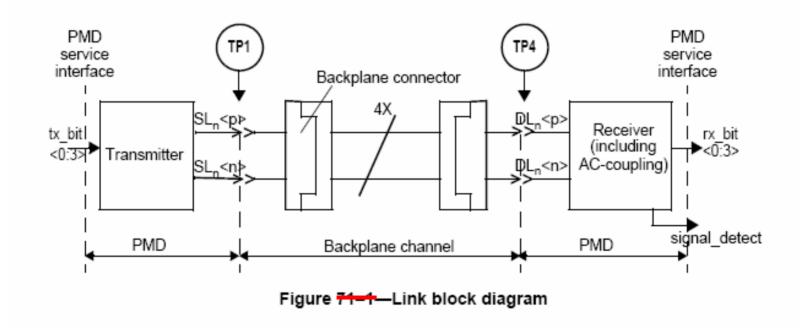

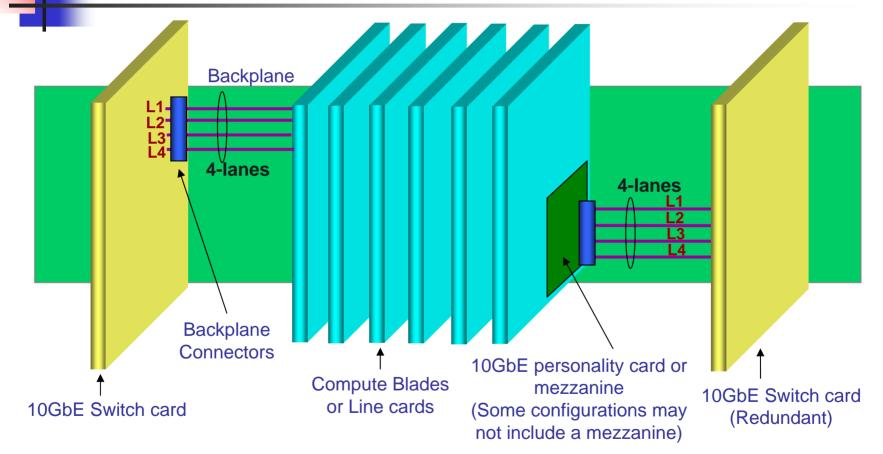

| 10            | Backplane PMD            | Move to adopt mellitz_01_0508.pdf as the baseline for the 40GbE backplane PHY (40GBASE-KR4).                                                                                                                                                                              | <u>#16 of May 2008</u>   | http://grouper.ieee.org/groups/802/3/ba/public/may08/mellitz_01_0508.pdf_                |

### **Chief Editor's Report**

#### Ilango Ganga, Intel Editor-in-Chief, IEEE P802.3ba Task Force

May 13, 2008

05/13/2008

IEEE P802.3ba Task Force meeting, May 2008, Munich, Germany

1

## **Existing clauses**

- Clause 1 Introduction to 802.3

- Add appropriate normative references, definitions, description of compatibility interfaces, and abbreviations

- Annex A –Bibliography

- Add appropriate informative references

- Clause 4, Annex 4A Media access control

- Mostly speed independent, update Table 4-2 MAC parameters

- Clause 30, Annex 30A & 30B Management

- Need presentation Add new objects, attributes, and enumerations for 40Gb/s and 100Gb/s functions

# Existing clauses (cont'd)

- Annex 31B MAC control PAUSE operation

- Need presentation Update timing considerations for PAUSE

- Clause 45 Management data input/output (MDIO) interface.

- Add new registers for the control and management of 40Gb/s and 100Gb/s PHY types

- Add new MMDs if any, control/status of PMA/PMD and PCS

- Update Backplane Auto-Negotiation and FEC registers

- Presentations to other clauses to include the required management variables

# Existing clauses (cont'd)

- Annex 69A Interference tolerance testing

- Need presentation 40GbE test methodology

- Annex 69B –Interconnect characteristics

- Need presentation 40GbE cross-talk limits if needed

- Clause 72 10GBASE-KR PMD

- Changes if any due to 40GbE

- Clause 73 Auto-Negotiation for Backplane Ethernet

- Add technology ability bit for new 40GbE PHY

- Clause 74 Forward error correction for 10GBASE-KR

- Changes for 4 lane KR operation

- Clause 74A FEC block coding examples

- Additional patterns for 4 lanes if needed

Need to select a proposal for 40Gb/s Backplane Ethernet

## **New Clauses**

- Introduction to 40Gb/s and 100Gb/s operation

- Based on presentations for other new clauses

- Global PICs separate PICS tables for 40 and 100Gb/s Sub-layers

- Need to select an architecture proposal for baseline

- Reconciliation Sublayer and Media Independent Interface(s)

- Need presentation to reference for baseline

- Physical Coding Sublayer clause(s)

- Need to select a proposal for baseline

- PMA Sublayer clause(s)

- Need presentation to reference for baseline(s)

- nAUI Electrical interface if included in adopted baseline proposals

- Need presentation to reference for baseline

- FEC sublayer for optical PMDs if included in adopted baseline proposals

- Need presentation to reference for baseline

## New Clauses

- 40G Backplane PMD Sublayer

- Need to select a proposal for baseline

- 40G / 100G Cu Cable PMD(s) Sublayer

- Need to select a proposal for baseline

- 40G / 100G MMF PMD(s) Sublayer

- Need to select a proposal for baseline

- 40G 10Km MMF PMD(s) Sublayer

- Need presentation to reference for baseline

- 100G 10km SMF PMD(s) Sublayer

- Need presentation to reference for baseline

- 100G 40km SMF PMD(s) Sublayer

- Need presentation to reference for baseline

- Additional annexes to describe test methods, channel characteristics, coding details, etc.,

- Need presentations to reference for baseline(s)

05/13/2008

IEEE P802.3ba Task Force meeting, May 2008, Munich, Germany

# **Proposed Nomenclature**

#### Nomenclature for the 3 part suffix

- Speed

- 40 = 40Gb/s, 100 = 100Gb/s

- Medium type

- Copper

- K = Backplane

- C = Cable assembly

- Optical

- S = Short Reach (100m)

- L = Long Reach (10Km)

- E = Extended Long Reach (40Km)

- Coding scheme

- R = 64B/66B block coding

- Number of lanes or wavelengths

- Copper: n = 4 or 10

- Optical: n = number of lanes or wavelengths

- n=1 not required as serial is implied

| PHY description            | Port Type     |

|----------------------------|---------------|

| 40G Backplane PHY          | 40GBASE-KR4   |

| 40G Cable Assembly PHY     | 40GBASE-CR4   |

| 100G Cable Assembly PHY    | 100GBASE-CR10 |

| 40G MMF 100m PHY (Ribbon)  | 40GBASE-SR4   |

| 100G MMF 100m PHY (Ribbon) | 100GBASE-SR10 |

| 40G SMF 10Km PHY           | 40GBASE-LR4   |

| 100G SMF 10Km PHY          | 100GBASE-LR4  |

| 100G SMF 40Km PHY          | 100GBASE-ER4  |

#### 40/100G Architecture and Interfaces proposal

Ilango Ganga, Intel Brad Booth, AMCC Howard Frazier, Broadcom Shimon Muller, Sun Gary Nicholl, Cisco

May 13, 2008

5/13/2008

IEEE P802.3ba 40/100GbE Task Force Meeting, Munich, Germany

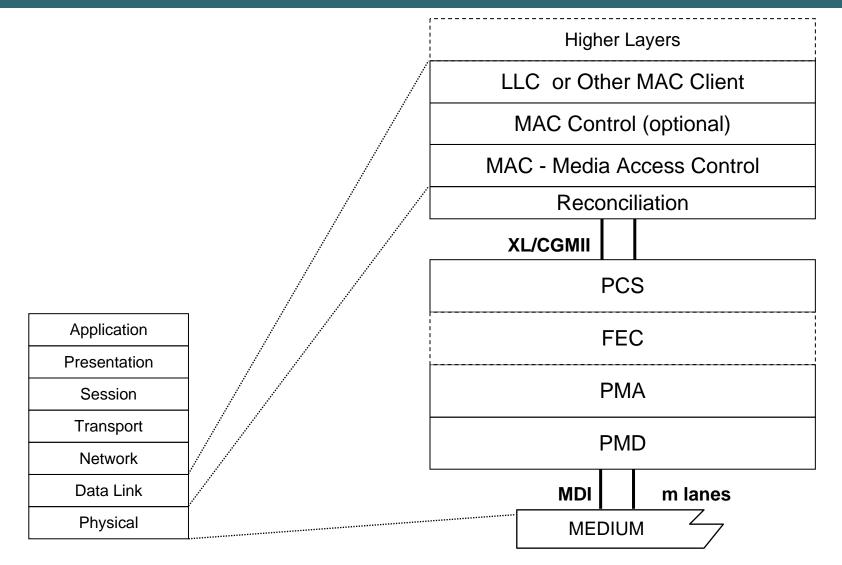

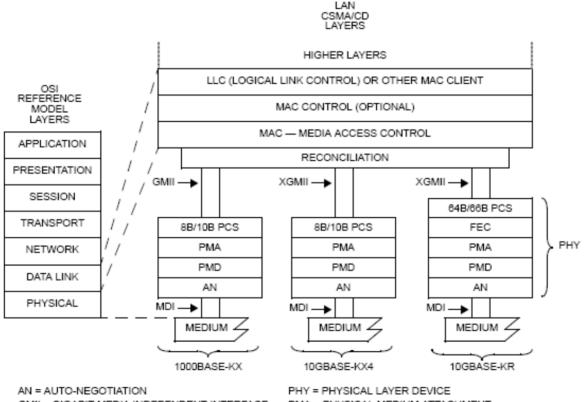

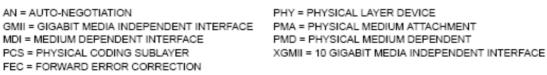

# Proposed 40/100GbE layer model

IEEE P802.3ba 40/100GbE Task Force Meeting, Munich, Germany

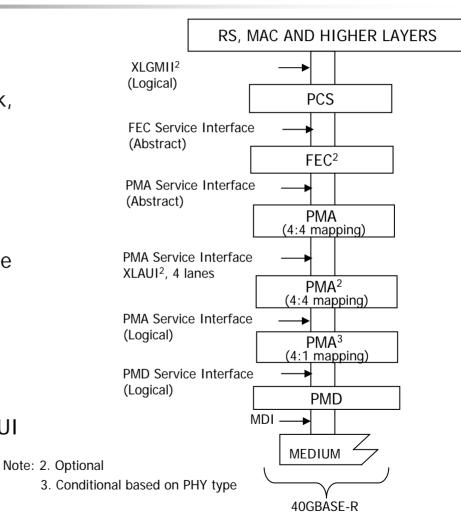

# Proposed 40GbE architecture

- XLGMII (intra-chip)

- Logical, define data/control, clock, no electrical specification

- PCS

- 64B/66B encoding

- Lane distribution and alignment

- XLAUI (chip-to-chip)

- 10.3125 GBaud electrical interface

- 4 lanes, short reach

- FEC service interface

- Abstract, can map to XLAUI electrical interface

- PMA Service interface

- Logical n lanes, can map to XLAUI electrical interface

- PMD Service interface

- Logical

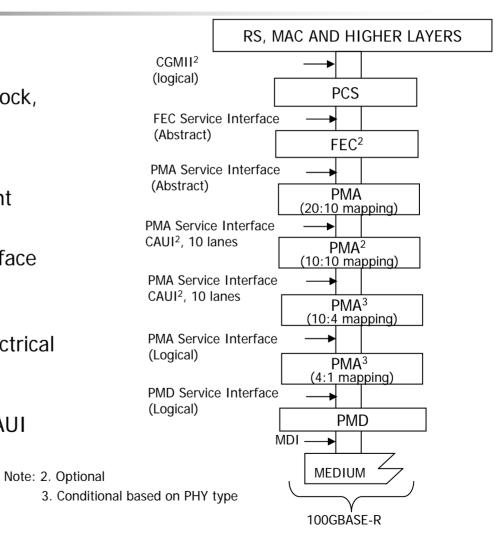

# Proposed 100GbE architecture

- CGMII (intra-chip)

- Logical, define data/control, clock, no electrical specification

- PCS

- 64B/66B encoding

- Lane distribution and alignment

- CAUI (chip-to-chip)

- 10.3125 GBaud electrical interface

- 10 lanes, short reach

- FEC service interface

- Abstract, can map to CAUI electrical interface

- PMA Service interface

- Logical n lanes, can map to CAUI electrical interface

- PMD Service interface

- Logical

5/13/2008

IEEE P802.3ba 40/100GbE Task Force Meeting, Munich, Germany

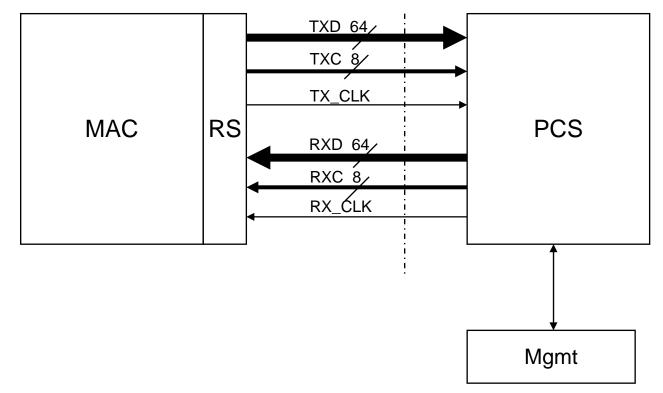

# Interface description (1)

- XLGMII (Forty Gigabit MII) or CGMII (100 Gigabit MII) PCS interface

- Interface between MAC and PHY layers needed for intra-chip connectivity

- Need for Compatibility interface

- Multiple vendors develop IP blocks for system on chip implementations

- Provides a point of interoperability for multi vendor implementations

- Logical definition, data width, control, clock frequency, no electrical specification

- XLGMII and CGMII will have same logical behavior

- Allows XLGMII/CGMII implementations with different data/control widths at either end of a link

- See gustlin\_02\_0508 for further details on XL/CGMII

# Interface description (2)

#### XLAUI or CAUI interface (Chip-to-Chip)

- 10.3125 GBaud electrical interface

- Lane width: 4 lane for 40G, and 10 lane for 100G

- Provides a point of interoperability for multi vendor implementations

- Similar to XAUI, for 10GbE, which is widely used as MAC-PHY interface

- Low pin count, low power interface, for example PHYs, Switches, LAN controllers

- Common electrical definition for XLAUI/CAUI

- 10.3125 GBaud differential signaling

- Short reach channel: e.g. around 10 inches with 1 connector

- Same electrical definition can be optionally used with multiple Service interfaces (e.g. PMA, FEC, etc.,)

- This is not an MDI

# Interface description (3)

- FEC Service interface

- Interface between PCS and optional FEC sub-layer

- Used for backplane PHYs, may be used with other PHY types (e.g. copper cable assy)

- FEC Service interface is similar to PMA interface

- Possible implementations: FEC integrated with MAC/PCS, or with PMA/PMD device

- Abstract definition, with an option to map to XLAUI/CAUI electrical interface

- PMA Service interface

- Interface between PMA and PCS

- Logical definition with n Lanes, can map to XLAUI/CAUI electrical interface

- PMD Service interface

- Interface between PMD and PMA

- PMA and PMD may be implemented together in the same device

- Logical definition

### **XL/CGMII and RS Proposal**

#### Mark Gustlin - Cisco

IEEE 802.3ba May 2008 Munich

### **Contributors and Supporters**

- Steve Trowbridge Alcatel-Lucent

- Brad Booth AMCC

- Dimitrios Giannakopoulos AMCC

- Piers Dawe Avago

- Howard Frazier Broadcom

- Arthur Marris Cadence Design Systems

- Gary Nicholl Cisco

- Med Belhadj Cortina Systems

- Chris Cole Finisar

- Subi Krishnamurthy Force10 Networks

- Aris Wong Foundry

- Shashi Patel Foundry

- Ryan Latchman Gennum

- Shinji Nishimura Hitachi

- Hidehiro Toyoda Hitachi

- John Jaeger Infinera

- Andy Moorwood Infinera

- Thananya Baldwin Ixia

- Jerry Pepper Ixia

- Faisal Dada JDSU

- Norbert Folkens JDSU

- Jack Jewell JDSU

- Jeffery J. Maki Juniper Networks

- David Ofelt Juniper Networks

- Adam Healey LSI

- Avigdor Segal Marvell

- Martin White Marvell

- Pete Anslow Nortel

- Song Shang SMI

- Shimon Muller Sun

- Farhad Shafai Sarance

- Andre Szczepanek TI

- Frank Chang Vitesse

#### **40GE/100GE** Architecture

• Why define it?

Electrically it won't see the light of day

Some want it for RTL to RTL connections within devices

• The interface is naturally scaled based on speed targets of an implementation

FPGAs run slower, ASICs faster, next generation ASICs even faster...

- Define it as a logical interface only

- Service primitives (function calls, pseudo code) +

- Signals, code-points, syntax, sequences, true/false

- Leverage XGMII, but make it 8 lanes instead of 4

- Preserve use of encoded rather than discrete delimiters

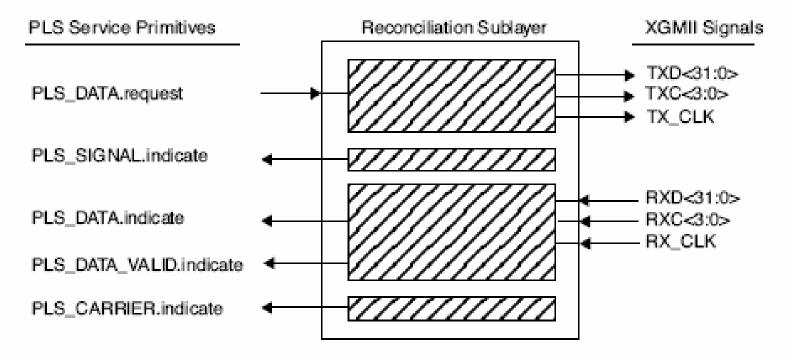

Figure 46–2–Reconciliation Sublayer (RS) inputs and outputs

From 802.3ae

- Leverage XGMII, but make it 8 lanes instead of 4

- CLK = 625MHz for 40GE, 1.5625GHz for 100GE

- Clock may be scaled down in frequency by increasing the width from 8 lanes to 16, 24, 32 etc.

XL/CGMII

#### **RX Diagram is Identical**

| TX_CLK     |      |        |                  |           |

|------------|------|--------|------------------|-----------|

| TXC<7:0>   | 0xFF | 0x01 X | 0x00 💔 0x0       | FC X 0xFF |

| TXD<7:0>   | I    | s X    | Frame Data 🔰     | XI        |

| TXD<15:0>  | I    | Dp     | Frame Data 🔰     | XI        |

| TXD<23:16> | I    | Dp X   | Frame Data 🚺 🗙 1 |           |

| TXD<31:24  | I    | Dp     | Frame Data 👫 🔨   | 1         |

| TXD<39:32> | I    | Dp     | Frame Data ∬ 🗙   | I         |

| TXD<47:40> | I    | Dp     | Frame Data ∬ 🛛   | I         |

| TXD<55:48> | I    | Dp X   | Frame Data ∬ 🔨   | I         |

| TXD<63:56> | I    | SFD    | Frame Data 🚺 🕺   |           |

I: Idle control character, S: Start control character, Dp: preamble Data octet, T: Terminate control character, SFD: Start of Frame Delimiter

#### Same encoding as XGMII (for both tx and rx):

| TXC                                                                                                        | TXD           | Description                     | PLS_DATA.request parameter                                                                  |  |  |

|------------------------------------------------------------------------------------------------------------|---------------|---------------------------------|---------------------------------------------------------------------------------------------|--|--|

| 0                                                                                                          | 00 through FF | Normal data transmission        | ZERO, ONE (eight bits)                                                                      |  |  |

| 1                                                                                                          | 00 through 06 | Reserved                        | -                                                                                           |  |  |

| 1                                                                                                          | 07            | Idle                            | No applicable parameter<br>(Normal inter-frame)                                             |  |  |

| 1                                                                                                          | 08 through 9B | Reserved                        | _                                                                                           |  |  |

| 1                                                                                                          | 9C            | Sequence (only valid in lane 0) | No applicable parameter<br>(Inter-frame status signal)                                      |  |  |

| 1                                                                                                          | 9D through FA | Reserved                        | -                                                                                           |  |  |

| 1                                                                                                          | FB            | Start (only valid in lane 0)    | No applicable parameter, replaces first<br>eight ZERO, ONE of a frame (pream-<br>ble octet) |  |  |

| 1                                                                                                          | FC            | Reserved                        | -                                                                                           |  |  |

| 1                                                                                                          | FD            | Terminate                       | DATA_COMPLETE                                                                               |  |  |

| 1                                                                                                          | FE            | Transmit error propagation      | No applicable parameter                                                                     |  |  |

| 1                                                                                                          | FF            | Reserved                        | -                                                                                           |  |  |

| NOTE-Values in TXD column are in hexadecimal, most significant bit to least significant bit (i.e., <7:0>). |               |                                 |                                                                                             |  |  |

#### Table 46–3–Permissible encodings of TXC and TXD

#### 8B vs. 4B alignment

- We could keep the legacy 4B alignment even with the new 8B wide bus

- Or we could go to 8B alignment

Only start packets in lane 0

Significant gate savings for 100GE, especially in FPGAs

Deficit counter goes from 0-7 for 8B alignment (vs. 0-3 for 4)

Doubles the buffering required for clock compensation when compared to 4B alignment

- Recommended to go with 8B alignment

- If interface is to be scaled down in frequency (and up in width), packet starts are still on 8B boundaries (lane 0, 8, 16 etc).

#### **IPG Rules for 8B Alignment**

• A MAC implementation may be designed to always insert additional idle characters to align the start of preamble on an eight byte boundary.

Note that this will reduce the effective data rate for certain packet sizes separated with minimum inter-frame spacing.

Alternatively, the RS may maintain the effective data rate by sometimes inserting and sometimes deleting idle characters to align the Start control character.

When using this method the RS must maintain a Deficit Idle Count that represents the cumulative count of idle characters deleted or inserted. The counter is incremented for each idle character deleted, decremented for each idle character inserted, and the decision of whether to insert or delete idle characters is constrained by bounding the counter to a minimum value of zero and maximum value of seven.

### Summary

- Simple logical interface based on XGMII

- Extended to 8 Bytes

- Naturally scales up and down in width and frequency

- Packet Starts on 8 Byte boundaries

### 100GE and 40GE PCS (MLD) Proposal

IEEE 802.3ba May 2008 Munich

### **Contributors and Supporters**

David Law – 3com Steve Trowbridge - Alcatel-Lucent Jesse Simsarian - Alcatel-Lucent Brad Booth – AMCC Dimitrios Giannakopoulos – AMCC Francesco Caggioni – AMCC Keith Conroy – AMCC Piers Dawe - Avago Rita Horner – Avago Howard Frazier - Broadcom Arthur Marris – Cadence Mike Shahine - Ciena Mark Nowell - Cisco Gary Nicholl - Cisco Hugh Barrass - Cisco Steve Swanson - Corning Med Belhadj - Cortina Chris Cole - Finisar Krishnamurthy Subramanian – Force10

Aris Wong – Foundry Networks Shashi Patel – Foundry Networks Bill Ryan – Foundry Networks Ryan Latchman - Gennum Justin Abbott - Gennum Hong Liu – Google Ashby Armistead – Google Shinji Nishimura - Hitachi Ltd Hidehiro Toyoda - Hitachi Ltd Dan Dove – HP Petar Pepeljugoski – IBM John Jaeger - Infinera Andy Moorwood - Infinera **Drew Perkins - Infinera** Jerry Pepper - Ixia Thananya Baldwin - Ixia Faisal Dada - JDSU Jack Jewell - JDSU Mike Dudek - JDSU

Jeffery J. Maki - Juniper Networks **David Ofelt - Juniper Networks** Brad Turner - Juniper Networks Adam Healey - LSI Martin White – Marvell Andy Weitzner – Marvell Pete Anslow – Nortel David W. Martin – Nortel Osamu Ishida - NTT Shoukei Kobayashi - NTT Matt Traverso – Opnext Farhad Shafai - Sarance Technologies Farzin Firoozmand – SMI Craig Hornbuckle – SMI Song Shang - SMI Ted Seely - Sprint Kengo Matsumoto - Sumitomo Electric Shimon Muller - Sun Andre Szczepanek – TI Martin Carroll - Verizon Frank Chang - Vitesse

### Agenda

- 40GE/100GE Architecture

- PCS and MLD layer details

- Possible XL/CGMII Interface

- Alignment details

- Alignment performance metrics

- Clocking example

- Skew

- Summary

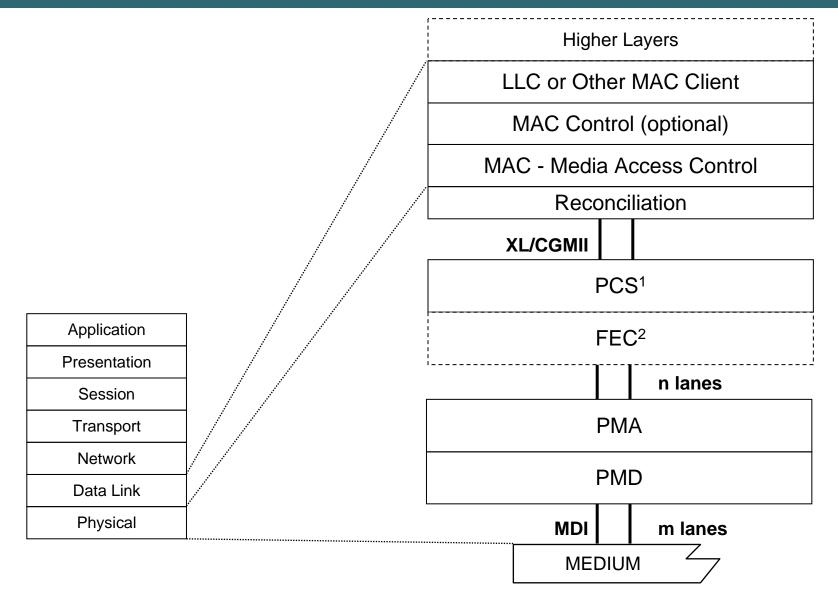

#### **40GE/100GE Generic Architecture**

2: For 40GE Backplane

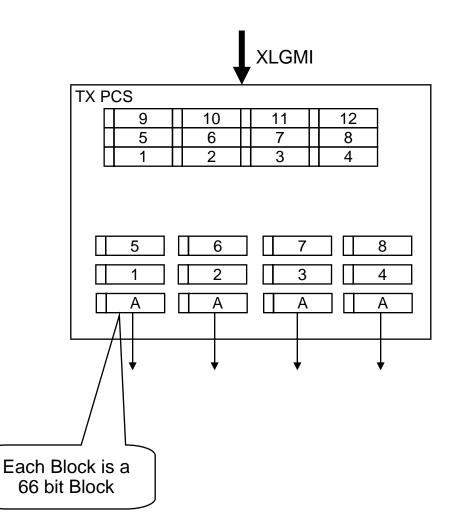

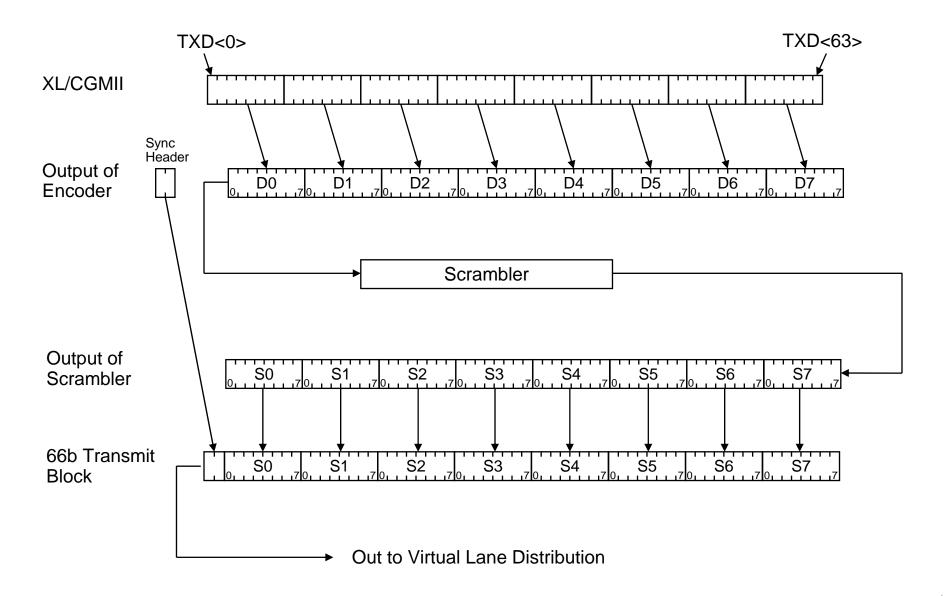

#### Proposed 100GE/40GE PCS

• 10GBASE-R 64B/66B based PCS

Run at 100Gbps or 40Gbps serial rate

Includes 66 bit block encoding and scrambling

• Multi-Lane Distribution

Data is distributed across n virtual lanes 66 bit blocks at a time

Round robin distribution

Periodic alignment blocks are added to each virtual lane to allow deskew in the rx PCS

• PMA maps n lanes to m lanes

PMA is simple bit level muxing

Does not know or care about PCS coding

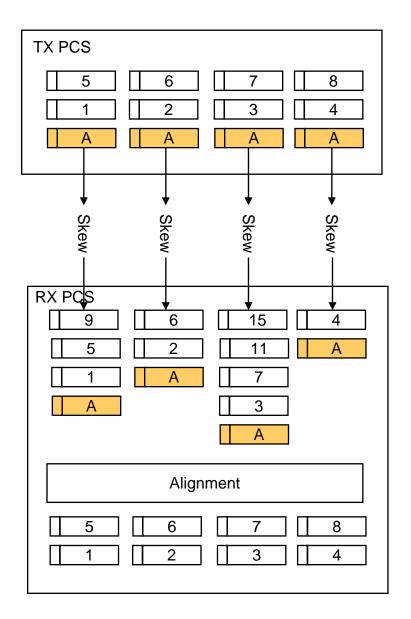

• Alignment and static skew compensation is done in the Rx PCS only

### **Striping Mechanism**

This example is 40GE with 4 electrical and 4 optical lanes

PCS Functions: 66 bit encoding Scrambling Periodic alignment block addition Round robin block distribution

#### Alignment Mechanism – 40GE Example

RX PCS Functions: Re-Align 66 bit blocks Remove the Alignment blocks Then descramble and decode

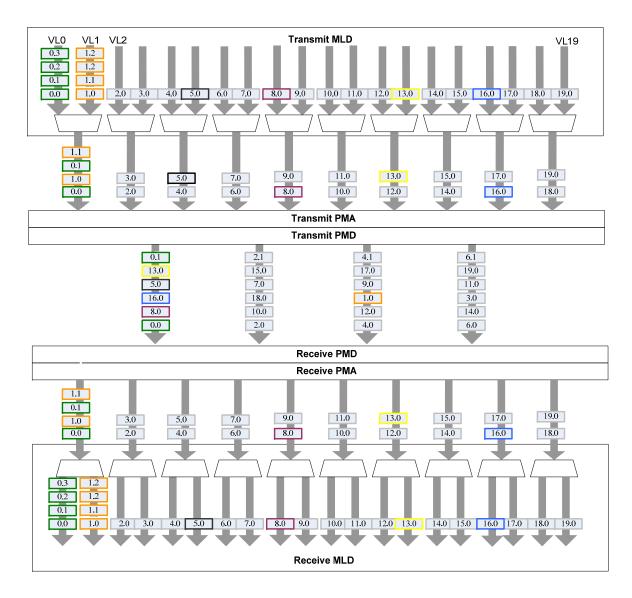

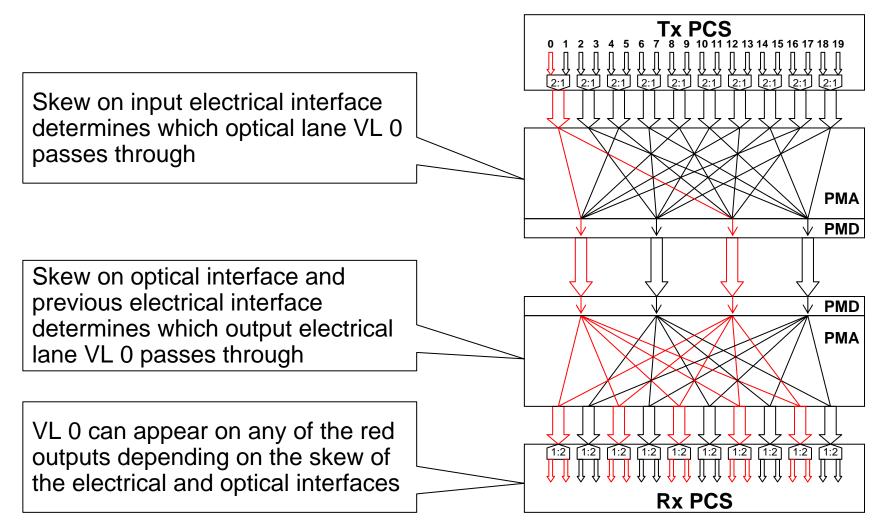

### **Key Concept – Virtual Lanes**

- Virtual lanes may or may not correspond to physical lanes

- Virtual lanes are created by distributing PCS encoded data in a round robin fashion, on a 66 bit block basis

- The number of virtual lanes generated is scaled to the Least Common Multiple (LCM) of the n lane electrical interface and the m lane PMD

This allows all data (bits) from one virtual lane to be transmitted over the same electrical and optical lane combination

This ensures that the data from a virtual lane is always received with the correct bit order at the Rx MLD

The alignment markers allow the Rx PCS to perform skew compensation, realign all the virtual lanes, and reassemble a single 100G or 40G aggregate stream (with all the 64B/66B blocks in the correct order)

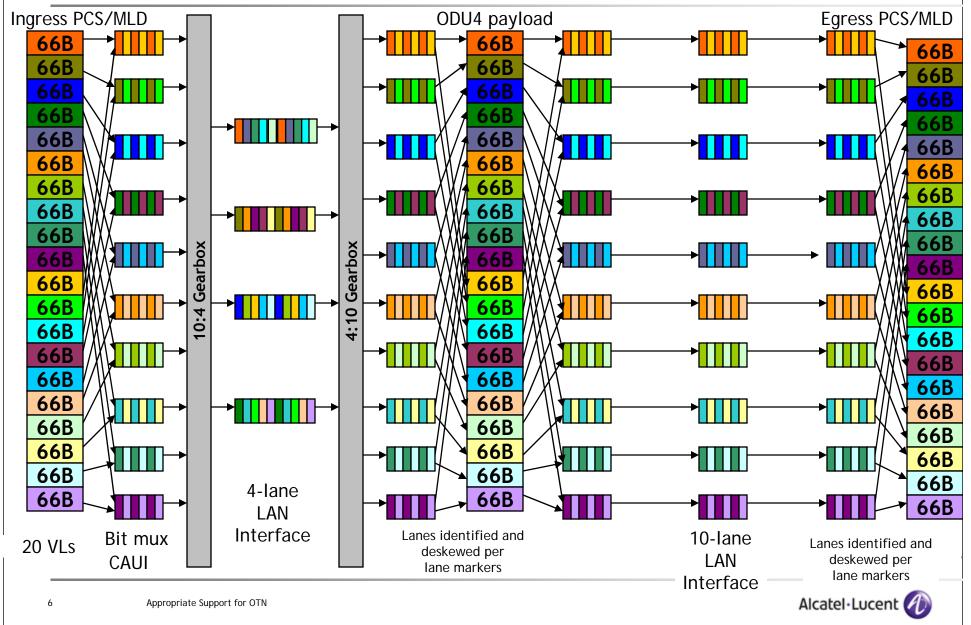

### Bit Flow Through – 100GE 4 lane PMD

- 20 VLs

- 10 Electrical lanes

- 4 Optical lanes

- With Skew, VLs move around

- RX MLD puts things back in order

#### How Many Virtual Lanes are Needed?

• 4 VLs For 40GE, this covers all of the possible combinations of lanes:

| Electrical Lane Widths | PMD Lane Widths | Virtual Lanes Needed |

|------------------------|-----------------|----------------------|

| 4, 2, 1                | 4, 2, 1         | 4                    |

• 20 VLs For 100GE, this covers all of the possible combinations of lanes:

| Electrical Lane Widths | PMD Lane Widths | Virtual Lanes Needed |

|------------------------|-----------------|----------------------|

| 10, 5, 4, 2, 1         | 10, 5, 4, 2, 1  | 20                   |

## PCS Encoding

• Same 10GBASE-R PCS (Clause 49) encoding

| Input Data                                                                                                               | S<br>y<br>n<br>c | Block               | Payload        |                |                |                |                |     |                |                |                |          |                            |

|--------------------------------------------------------------------------------------------------------------------------|------------------|---------------------|----------------|----------------|----------------|----------------|----------------|-----|----------------|----------------|----------------|----------|----------------------------|

| Bit Position:<br>Data Block Format:                                                                                      | 01               | 2                   |                |                |                |                |                |     |                |                | 65             |          |                            |

| D <sub>0</sub> D <sub>1</sub> D <sub>2</sub> D <sub>3</sub> /D <sub>4</sub> D <sub>5</sub> D <sub>6</sub> D <sub>7</sub> | 01               | D <sub>0</sub>      | D1             | D <sub>2</sub> | D <sub>3</sub> | 1              | 04             | 1   | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> |          |                            |

| Control Block Formats:                                                                                                   |                  | Block Type<br>Field |                |                | 1              |                |                |     |                |                |                | ]        |                            |

| C <sub>0</sub> C <sub>1</sub> C <sub>2</sub> C <sub>3</sub> C <sub>4</sub> C <sub>5</sub> C <sub>6</sub> C <sub>7</sub>  | 10               | 0x1 e               | C <sub>0</sub> | C1             | C <sub>2</sub> | C <sub>3</sub> | C4             |     | C5             | C <sub>6</sub> | C7             |          |                            |

| C0C1C2C3O4D5D6D7                                                                                                         | 10               | 0x2d                | 9,             | 01             | 0 <sub>2</sub> | <b>C</b> 3     | 04             | F i | 5              | D <sub>6</sub> | D <sub>7</sub> | <u> </u> | Not used                   |

| G, C, C, C, C,/S, D, D, D,                                                                                               | 10               | 0,423               | <b>G</b> ,     | C,             | C <sub>2</sub> | Ç,             |                |     | 2              | D,             | D,             |          | since we have              |

| 0.0.0.0/6.0.0.0                                                                                                          | 10               | 0.69                | D.             |                |                |                |                |     |                | D.             | D              |          | 8B alignment               |

| -0-1-2-3-4-5-6-7                                                                                                         |                  |                     | -              | -2             | -3             |                |                |     | •              | 0              | ,              | <u></u>  |                            |

| 00 D1 D2 D3/04 D5 D6 D7                                                                                                  | <b>I</b> —       | 0x55                | 01             | D <sub>2</sub> | D <sub>3</sub> | 00             |                | L   | 5              | D6             | 07             |          |                            |

| S <sub>0</sub> D <sub>1</sub> D <sub>2</sub> D <sub>3</sub> /D <sub>4</sub> D <sub>5</sub> D <sub>6</sub> D <sub>7</sub> | 10               | 0x78                | D              | D <sub>2</sub> | D <sub>3</sub> |                | D4             |     | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> |          |                            |

| $O_0 D_1 D_2 D_3 C_4 C_5 C_6 C_7$                                                                                        | 10               | 0x4b                | D1             | D <sub>2</sub> | D <sub>3</sub> | 00             | C4             |     | C <sub>5</sub> | C <sub>6</sub> | C7             |          | $\int$                     |

| T <sub>0</sub> C <sub>1</sub> C <sub>2</sub> C <sub>3</sub> /C <sub>4</sub> C <sub>5</sub> C <sub>6</sub> C <sub>7</sub> | 10               | 0x87                |                | C1             | C <sub>2</sub> | C <sub>3</sub> | C4             |     | C <sub>5</sub> | C <sub>6</sub> | C7             |          | Only block                 |

| ${\tt D}_0{\tt T}_1{\tt C}_2{\tt C}_3\!/{\tt C}_4{\tt C}_5{\tt C}_6{\tt C}_7$                                            | 10               | 0x99                | Do             |                | C <sub>2</sub> | C3             | C4             |     | C <sub>5</sub> | C <sub>6</sub> | C <sub>7</sub> |          | type used for ordered sets |

| $D_0 D_1 T_2 C_3 C_4 C_5 C_6 C_7$                                                                                        | 10               | 0xaa                | D <sub>0</sub> | D1             |                | C <sub>3</sub> | C4             |     | C5             | C <sub>6</sub> | C7             | ]        |                            |

| ${\sf D}_0{\sf D}_1{\sf D}_2{\sf T}_3\!/{\sf C}_4{\sf C}_5{\sf C}_6{\sf C}_7$                                            | 10               | 0xb4                | Do             | Di             | D <sub>2</sub> |                | C,             | 4   | C5             | C <sub>6</sub> | C7             |          |                            |

| $D_0D_1D_2D_3/T_4C_5C_6C_7$                                                                                              | 10               | 0xcc                | Do             | D1             | D <sub>2</sub> | 1              | D <sub>3</sub> |     | C5             | C <sub>6</sub> | C7             |          |                            |

| ${\rm D}_0{\rm D}_1{\rm D}_2{\rm D}_3/{\rm D}_4{\rm T}_5{\rm C}_6{\rm C}_7$                                              | 10               | 0xd2                | D <sub>0</sub> | D1             | D <sub>2</sub> |                | )3             |     | )4             | C <sub>6</sub> | C7             |          |                            |

| ${\sf D}_0{\sf D}_1{\sf D}_2{\sf D}_3/{\sf D}_4{\sf D}_5{\sf T}_6{\sf C}_7$                                              | 10               | 0xe1                | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | 0              | )3             | D   | )4             | D <sub>5</sub> | C7             | ]        |                            |

| $D_0 D_1 D_2 D_3 D_4 D_5 D_6 T_7$                                                                                        | 10               | 0xff                | D <sub>0</sub> | D1             | D <sub>2</sub> | [              | D <sub>3</sub> | [   | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | ]        |                            |

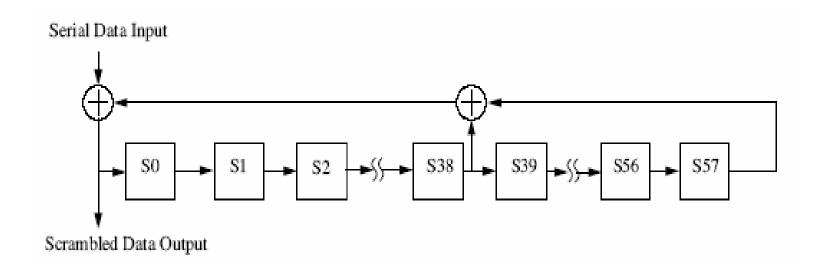

### **PCS Scrambling**

• Identical 10GBASE-R PCS (Clause 49) scrambler

Runs at 40Gbps or 100Gbps now

### **PCS Idle Deletion/Insertion rules**

• Straight from 802.3ae (except for highlighted text):

Idle insertion or deletion occurs in groups of <u>eight</u> Idle characters

Idle characters are added following idle or ordered\_sets

Idle characters are not added while data is being received

When deleting idles, the minimum IPG of <u>one character</u> is maintained

Sequence ordered\_sets are deleted to adapt between clock rates

Sequence ordered\_set deletion occurs only when two consecutive sequence ordered\_sets have been received and deletes only one of the two

Only idles are inserted for clock compensation

### **PCS Bit Order**

### **Alignment Proposal**

- Send alignment on a fixed time basis

- Alignment word also identifies virtual lanes

- Sent every 16384 66bit blocks on each virtual lane at the same time

~216usec for 20 VLs @ 100G

~108usec for 4 VLs @ 40G

- It temporarily interrupts packets

- Takes only 0.006% (60PPM) of the Bandwidth

- Rate Adjust FIFO will delete enough IPG so that the MAC still runs at 100.000G or 40.000G with the interface running at 10.3125G

### **Alignment Word Proposal**

Requirements:

- Significant transitions and DC balanced word is not scrambled

- Keep in 66 bit form, but no relation to 10GBASE-R is needed

- But why not keep it close? Because of the clock wander concerns

- Contains Virtual Lane Identifier

#### Proposed Alignment Word

|--|

- This is DC balanced

- No relationship to the normal 10GBASE-R blocks

- Added after and removed before 64/66 processing

- Alignment block is periodic, no Hamming distance concerns with 64/66 block types

### Alignment Word Proposal – 100GE

The encoding of the VL markers is as follows (based on  $x^{58} + x^{39} + 1$  scrambler output):

| VL Number | 32 Bit encoding | VL Number | 32 Bit encoding |

|-----------|-----------------|-----------|-----------------|

| 0         | C1,68,21,F4     | 10        | FD, 6C, 99, DE  |

| 1         | 9D, 71, 8E, 17  | 11        | B9, 91, 55, B8  |

| 2         | 59, 4B, E8, B0  | 12        | 5C, B9, B2, CD  |

| 3         | 4D, 95, 7B, 10  | 13        | 1A, F8, BD, AB  |

| 4         | F5, 07, 09, 0B  | 14        | 83, C7, CA, B5  |

| 5         | DD, 14, C2, 50  | 15        | 35, 36, CD, EB  |

| 6         | 9A, 4A, 26, 15  | 16        | C4, 31, 4C, 30  |

| 7         | 7B, 45, 66, FA  | 17        | AD, D6, B7, 35  |

| 8         | A0, 24, 76, DF  | 18        | 5F, 66, 2A, 6F  |

| 9         | 68, C9, FB, 38  | 19        | C0, F0, E5, E9  |

Note that data is played out in VL order, 0, 1, 2, ... 19, 0, 1...

### Alignment Word Proposal – 40GE

The encoding of the VL markers is as follows (based on  $x^{58} + x^{39} + 1$  scrambler output):

| VL Number | 32 Bit encoding |

|-----------|-----------------|

| 0         | C1,68,21,F4     |

| 1         | 9D, 71, 8E, 17  |

| 2         | 59, 4B, E8, B0  |

| 3         | 4D, 95, 7B, 10  |

Note that data is played out in VL order, 0, 1, 2, 3, 0...

# **Possible Paths Through the Link**

Note: These possible paths are based on a 10:4 and 4:10 function based on round-robin distribution. Other arrangements which give different paths are possible.

### **Virtual Lane Location on the Receive Side**

Due to how virtual lanes are multiplexed, and due to skew, and in order to be future proof:

All receivers must support receiving a transmitted virtual lane on any received virtual lane

This is true for 100GE and 40GE

### Finding VL Alignment

- After reception in the rx MLD, you have x VLs, each skewed and transposed

- First you find 66bit alignment on each VL

Each VL is a stream of 66 bit blocks

Same mechanism as 10GBASE-R (64 valid 2 bit frame codes in a row)

• Then you hunt for alignment on each VL

Look for one of the 20 VL patterns repeated and inverted

- Alignment is declared on each VL after finding 2 consecutive non-errored alignment patterns in the expected locations (16k words apart)

- Out of alignment is declared on a VL after finding 4 consecutive errored frame patterns

- Once the alignment pattern is found on all VLs, then the VLs can be aligned

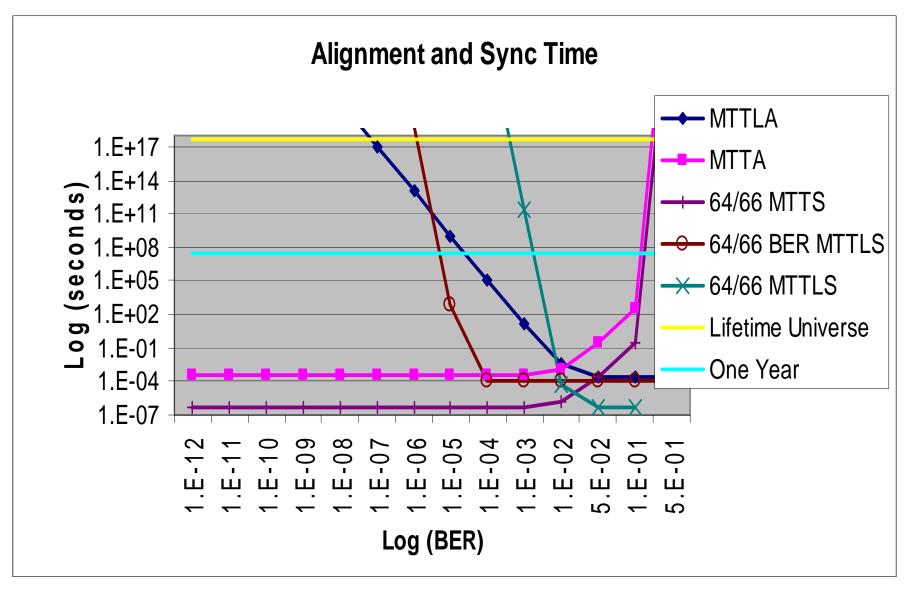

### Alignment Performance Parameters – 100GE

Mean Time To Alignment (MTTA)

Mean time it takes to gain Alignment on a lane or virtual lane for a given BER

Nominal time = 314usec

• Mean Time To Loss of Alignment (MTTLA)

Mean time it takes to lose Alignment on a lane or virtual lane for a given BER

- Probability of False Alignment (PFA) = 3 E-40

- Probability of Rejecting False Alignment (PRFA) = ~1

- Also have 64/66 sync stats on the graph for comparison

MTTS – Mean Time To Sync (64 non errored syncs in a row)

BER MTTLS – With the 125usec BER window, what is the Mean Time To Lose Sync

MTTLS - Mean Time To Lose Sync

### Alignment Performance Parameters – 100GE

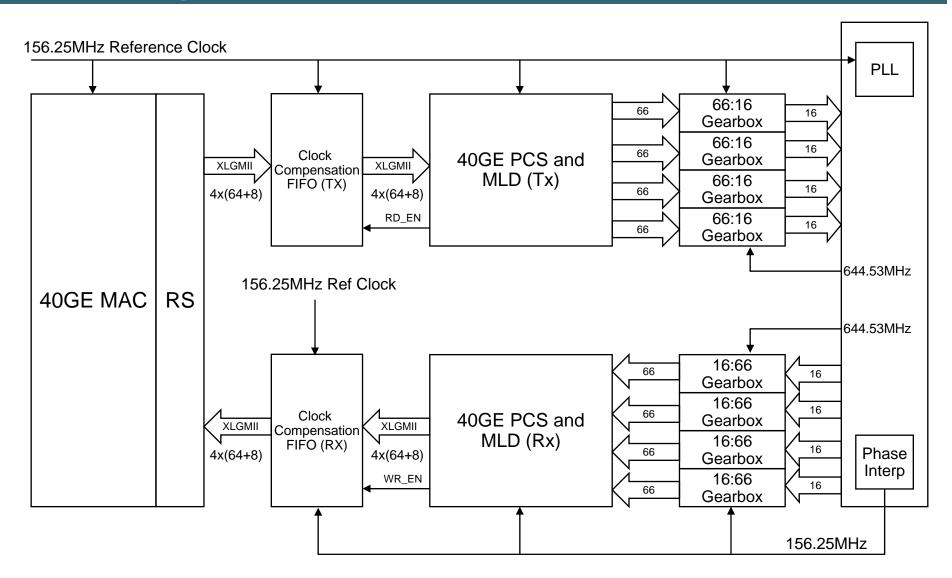

### **Clocking Example – 40GE**

### **Skew Handling**

- Both dynamic and static skew budgets need to be identified

- See other presentations for details

### Summary

- Simple 10GBASE-R based PCS

- MLD layer to support multiple physical lanes/lambdas

- Complexity is low within the MLD layer

- Simple block data striping

- Complexity in the optical module is low

- Simple bit muxing even when m != n

- Based on proven 64B/66B framing and scrambling

- Electrical interface is feasible at 10x10G or 4x10G

- Allows for a MAC rate of 100.000G or 40.000G

- Overhead very low and independent of packet size

- Supports an evolution of optics and electrical interfaces

## Proposal for a PMD for 100GBASE-SR10 and 40GBASE-SR4 and Related Specifications

Petar Pepeljugoski - IBM Piers Dawe, John Petrilla - Avago Technologies John Dallesasse, Kenneth Jackson - Emcore Lew Aronson, Jonathan King, Chris Cole - Finisar Mike Dudek, Jack Jewell – JDSU Phil McClay - Zarlink

# Proposal

- 10 parallel lanes @ 10.3125 GBd for 100GBASE-SR10 over OM3 fiber

- 4 parallel lanes @ 10.3125 GBd for 40GBASE-SR4 over OM3 fiber

- No glue chip required

- See also last slide

# Transmitter specifications (each lane)

| Description                                   | Value                                          | Unit  |

|-----------------------------------------------|------------------------------------------------|-------|

| Signaling speed (nominal)                     | 10.3125                                        | GBd   |

| Signaling speed variation from nominal (max)  | ±100                                           | ppm   |

| Center wavelength (range)                     | 840-860                                        | nm    |

| RMS spectral width (max)                      | 0.65                                           | nm    |

| Average Launch Power (max) (2)                | 1 <sup>(1)</sup>                               | dBm   |

| Launch Power (min) in OMA                     | -3 (1), (3)                                    | dBm   |

| Average launch power of OFF transmitter (max) | -30                                            | dBm   |

| Extinction ratio (min)                        | 3                                              | dB    |

| RIN <sub>12</sub> OMA (max)                   | -128 to -132 <sup>(1),(3)</sup>                | dB/Hz |

| Optical Return Loss Tolerance (max)           | 12                                             | dB    |

| Encircled Flux                                | > 86% @ 19um,<br>< 30% at 4.5um <sup>(1)</sup> |       |

| Transmitter eye mask definition               | TBD                                            |       |

| Aggregate TP2 signal metrics (4)              | TBD                                            | TBD   |

| TP1 jitter allocation                         | 0.3 <sup>(5)</sup>                             | U.I.  |

<sup>(1)</sup> subject to further study

<sup>(2)</sup> see presentation on eye safety by J. Petrilla at March 2008 meeting

<sup>(3)</sup> to be made informative if aggregate signal parameter includes the effect

<sup>(4)</sup> for further study, e.g. TDP, TWDP, etc.

<sup>(5)</sup> for further study, intermediate between 10G SFP+ and 8GFC

# Receiver characteristic (each lane)

| Description                                  |                         |          |

|----------------------------------------------|-------------------------|----------|

| Signaling speed (nominal)                    | 10.3125                 | GBd      |

| Signaling speed variation from nominal (max) | ± 100                   | ppm      |

| Center wavelength (range)                    | 840-860                 | nm       |

| Average receiver power (max)                 | <b>1</b> <sup>(1)</sup> | dBm      |

| Average power at receiver input (min)        | -7.9 <sup>(1),(2)</sup> | dBm      |

| Receiver reflectance (max)                   | -12                     | dB       |

| Stressed receiver sensitivity in OMA (max)   | TBD                     | dBm      |

| - Vertical eye closure penalty (target)      | TBD                     | dB       |

| - Stressed eye jitter (target)               | TBD                     | UI pk-pk |

| TP4 jitter allocation                        | 0.7                     | UI       |

<sup>(1)</sup> For further study

<sup>(2)</sup> Depends on connector loss

# Link and Cable Characteristic

| Parameter                    | Value    | Unit   |

|------------------------------|----------|--------|

| Supported fiber types        | 50µm OM3 |        |

| Effective Modal<br>Bandwidth | 2000*    | MHz*km |

| Power Budget                 | >8.3**   | dB     |

| Operating Range              | 0.5-100  | m      |

| Channel insertion loss       | 1.9***   | dB     |

\* - depends on launch conditions

\*\* - for further study

\*\*\* - connector loss under study

# Appropriate Support for OTN Baseline Proposal

Stephen J. Trowbridge Alcatel-Lucent

Appropriate Support for OTN

#### **Supporters**

- Thomas Fischer Nokia-Siemens Networks

- Pete Anslow Nortel Networks

- Ralf-Peter Braun Deutsche Telekom

- Martin Carroll Verizon

- Ghani Abbas Ericsson

- Arne Alping Ericsson

- Chris Cole Finisar

- Mark Gustlin Cisco

- Osamu Ishida NTT

- George Young AT&T

- Gary Nicholl Cisco

### Key elements of OTN support

- Use a Lane Independent PCS to enable different Ethernet PMDs to be used at the OTN ingress/egress

o Key feature of MLD

- 40 GbE must fit into the OPU3 payload with a minimum of PCS codeword and timing transparency

- o Limitation on control block types to permit transcoding

- Lane Marker transparency for 40 GbE

- o ITU-T decision, but maintain spare value in 4-bit representation of control block types available for encoding lane markers if necessary

- Link fault signaling for 802.3ba Ethernet over OTN can use existing mechanisms from 802.3ae

### Common PCS – Good news

- The MLD proposal comprises a common PCS that is used across all Ethernet PMDs - see <u>gustlin\_01\_0308</u>

- As the complexity of using the MLD PCS is no more than that of managing skew to within 32UI (see <u>shafai\_01\_0308</u>), consensus is moving towards using the MLD PCS for all PHY types including 40 GbE backplane

- Skew in OTN must be managed so that Ethernet over OTN does not exceed LAN deskew budget (OTN must deskew)

**Example:** Four-Lane 100 GbE LAN interface at OTN ingress; 10-Iane 100 GbE LAN interface at OTN egress.

### Common PCS Proposal (100 GbE and 40 GbE)

- Adopt MLD with 64B/66B coding as the common PCS for all 802.3ba interfaces. This enables:

- o A single canonical form to be used for mapping of any 802.3ba interface with at least codeword transparency over OTN

- o Selection of different Ethernet PMDs at the OTN ingress and egress

### OTN support for 40 GbE

#### • Two ways to provide 40 GbE transparent transport over OTN:

- Choose a MAC bit-rate (e.g., 38.9 Gbit/s) such that 64B/66B coding and lane marker insertion results in a bit-stream that fits the payload area of an OPU3 (not preferred)

- o Impose strict requirements on PCS codeword set that permits codeword transparent mapping of 40 GbE into payload of OPU3 (preferred)

- Feasibility for codeword transparent mapping from 40.0 Gbit/s MAC rate into capacity of OPU3 payload demonstrated in <u>trowbridge\_01\_0707</u>, with possible improvements shown in <u>trowbridge\_01\_0308</u> (actual standard to be specified as mapping of 40 GbE into OTN by ITU-T SG15)

- o The proposed transcoding method requires 15 or fewer control block types to be used in underlying 64B/66B code

- o A single additional (among the 16 available) control block type can be used to encode a lane marker, with 56 bits available for a very sparse coding of the lane number

- 10G Base-R 64B/66B coding uses 15 control block types. 40GbE/100GbE may use fewer control block types if packet and ordered set start is restricted to an 8-byte boundary

- To rely on transcoding, a fixed, limited set of control block types understood by both IEEE and ITU-T is essential to specification of the mapping of 40 GbE into OPU3 and interoperable implementations

8

# Possible Changes to 64B/66B for 40 GbE and 100 GbE given 8-byte boundary for packet start and ordered sets

| Ordered sets can't start in 5 <sup>th</sup> lane | Input Data                                                                                                               | S<br>y<br>n<br>c | Block I             | Payload        |                |                |                |                |                |                |                |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------|---------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

|                                                  | Bit Position:                                                                                                            | 01               | 2                   |                |                |                |                |                |                |                | 65             |

|                                                  | $\begin{array}{c} \textbf{Data Block Format:} \\ D_0 D_1 D_2 D_3 / D_4 D_5 D_6 D_7 \end{array}$                          | 01               | D <sub>0</sub>      | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | [              | D <sub>4</sub> | $D_5$          | D <sub>6</sub> | D <sub>7</sub> |

|                                                  | Control Block Formats:                                                                                                   | ┢                | Block Type<br>Field |                |                |                |                |                |                |                |                |

|                                                  | C <sub>0</sub> C <sub>1</sub> C <sub>2</sub> C <sub>3</sub> /C <sub>4</sub> C <sub>5</sub> C <sub>6</sub> C <sub>7</sub> | 10               |                     | C <sub>0</sub> | C <sub>1</sub> | C <sub>2</sub> | C <sub>3</sub> | C <sub>4</sub> | C <sub>5</sub> | C <sub>6</sub> | C <sub>7</sub> |

| \ <b>\_</b>                                      |                                                                                                                          | 10               | 0x2d                | C <sub>0</sub> | C;             | C <sub>2</sub> | C <sub>0</sub> | 0,             | D <sub>2</sub> | D <sub>0</sub> |                |

|                                                  |                                                                                                                          | 10               | 0+22                | C,             | Ć,             | <u>_</u>       | C,             |                | Ρ,             | D,             | Ρ,             |

| Packets can't                                    | O <sub>2</sub> D <sub>1</sub> D <sub>2</sub> D <sub>2</sub> /S <sub>1</sub> D <sub>2</sub> D <sub>2</sub> D <sub>2</sub> | 10               | 0x66                | D4             | De             | De             | 0.             |                | De             | De             | D-7            |

| start in 5 <sup>th</sup> lane                    |                                                                                                                          | 10               | 0x55                | D,             | D2             | D,             | 0,             | 0,             | D <sub>E</sub> | De             | D-             |

| start in 5 tane                                  | S <sub>0</sub> D <sub>1</sub> D <sub>2</sub> D <sub>3</sub> /D <sub>4</sub> D <sub>5</sub> D <sub>6</sub> D <sub>7</sub> | 10               | 0x78                | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | 1              | D <sub>4</sub> | $D_5$          | D <sub>6</sub> | D <sub>7</sub> |

|                                                  | O <sub>0</sub> D <sub>1</sub> D <sub>2</sub> D <sub>3</sub> /C <sub>4</sub> C <sub>5</sub> C <sub>6</sub> C <sub>7</sub> | 10               | 0x4b                | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | O <sub>0</sub> | C <sub>4</sub> | C <sub>5</sub> | C <sub>6</sub> | C <sub>7</sub> |

|                                                  | $T_0 C_1 C_2 C_3 / C_4 C_5 C_6 C_7$                                                                                      | 10               | 0x87                |                | C <sub>1</sub> | C <sub>2</sub> | C <sub>3</sub> | C <sub>4</sub> | C <sub>5</sub> | C <sub>6</sub> | C <sub>7</sub> |

|                                                  | D <sub>0</sub> T <sub>1</sub> C <sub>2</sub> C <sub>3</sub> /C <sub>4</sub> C <sub>5</sub> C <sub>6</sub> C <sub>7</sub> | 10               | 0x99                | D <sub>0</sub> |                | C <sub>2</sub> | C <sub>3</sub> | C <sub>4</sub> | C <sub>5</sub> | C <sub>6</sub> | C <sub>7</sub> |

| It is expected that the                          | $D_0  D_1  T_2  C_3 / C_4  C_5  C_6  C_7$                                                                                | 10               | 0xaa                | D <sub>0</sub> | D <sub>1</sub> |                | C <sub>3</sub> | C <sub>4</sub> | C <sub>5</sub> | C <sub>6</sub> | C <sub>7</sub> |

| 64B/66B coding for 40GbE                         | $D_0  D_1  D_2  T_3 / C_4  C_5  C_6  C_7$                                                                                | 10               | 0xb4                | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> |                | C <sub>4</sub> | C <sub>5</sub> | C <sub>6</sub> | C <sub>7</sub> |

| and 100 GbE will use                             | $D_0 D_1 D_2 D_3 / T_4 C_5 C_6 C_7$                                                                                      | 10               | 0xcc                | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> |                | D <sub>3</sub> | C <sub>5</sub> | C <sub>6</sub> | C <sub>7</sub> |

| between 11 and 15                                | $D_0D_1D_2D_3/D_4T_5C_6C_7$                                                                                              | 10               | 0xd2                | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | [              | D <sub>3</sub> | D <sub>4</sub> | C <sub>6</sub> | C <sub>7</sub> |

| control block types, leaving                     | $D_0 D_1 D_2 D_3 / D_4 D_5 T_6 C_7$                                                                                      | 10               | 0xe1                | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | [              | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | C <sub>7</sub> |

| one 4-bit code free for                          | D <sub>0</sub> D <sub>1</sub> D <sub>2</sub> D <sub>3</sub> /D <sub>4</sub> D <sub>5</sub> D <sub>6</sub> T <sub>7</sub> | 10               | 0xff                | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | [              | D <sub>3</sub> | D <sub>4</sub> | $D_5$          | D <sub>6</sub> |

| encoding of lane markers<br>if necessary         |                                                                                                                          |                  | Figu                | re 49–7-       | 64B/60         | 6B bloc        | k form         | ats            |                |                |                |

9

### 40 GbE into OPU3 – what can break the mapping?

- Someone could implement a proprietary extension that used nonstandard control block types

- o Extremely unlikely area for proprietary extension as proper packet delineation depends on control block types and misuse could lose packet framing and impair MTTFPA; however

- o As a safeguard, the standard should contain extremely strong language to prevent proprietary extensions in this area

- Evolution of the standard could allocate new control block types that are not anticipated by the OTN mapper

- o As a safeguard, the relationship between IEEE 802.3 and ITU-T Recommendation should be clearly noted in the standards

### OTN support for 40 GbE proposal

- The aggregate PCS encoded bit-rate for 40 GbE including 64B/66B coding with inserted MLD lane markers shall be no more than 41.25 Gbit/s ±100ppm

- Aside from MLD lane markers, PCS codewords are 64B/66B encoded blocks similar to those used in 10G Base-R (IEEE Std 802.3 clause 49)

- The PCS coding for 40 GbE shall use no more than the 15 control block types specified for 10G Base-R (likely fewer, if 8-byte alignment for packet start and/or ordered sets)

- The equivalent of Figure 49-7 for the 40 GbE PCS shall include the following text:

- "Control block types not listed in Figure xx-yy shall not be transmitted and shall be considered an error if received"

- and Pending concurrence of the 802.3 working group

- "The mapping of 40G Base-?? signals into OPU3 (to be) specified in ITU-T Recommendation G.709 depends on the set of control block types shown in Figure xx-yy. Any change to the coding specified in Figure xx-yy must be coordinated with ITU-T Study Group 15."

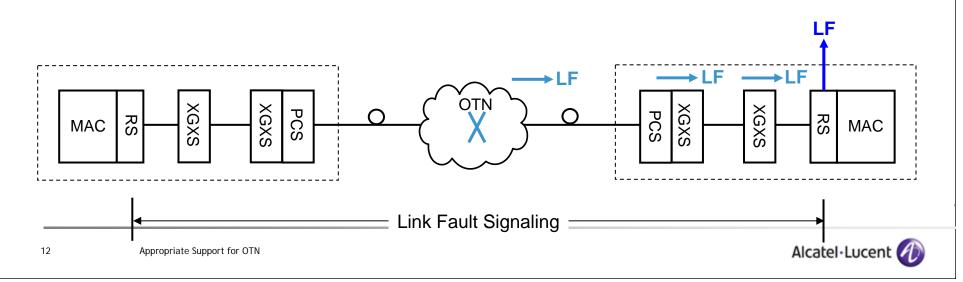

#### Link Fault Signaling for Ethernet over OTN

LF will be transmitted on the Ethernet interface as the forward defect indication when failures are detected within the OTN network (using the same sequence ordered set as in 802.3ae)

- Consistent with the definition of link fault signaling (LF/RF) in Clause 46

- An OTN failure is treated no differently than any other failure between remote and local RS (Clause 46)

- Nothing needs to be added or changed for 802.3ba

- The equipment functions specified by ITU-T SG15 supporting the OTN mappings for 40GE and 100GE should clarify that Local Fault (LF) should be inserted on the downstream (egress) ethernet interface in the event of OTN failures

## 100GE 40km SMF PMD

## IEEE 802.3ba Task Force 13-15 May 2008

Chris Cole - Finisar

**Pete Anslow - Nortel**

Ramon Gutierrez - UNAM

Wenbin Jiang - Huawei

John Johnson - CyOptics Radha Nagarajan - Infinera Hirotaka Oomori - Sumitomo Matt Traverso - Opnext

### Supporters

- Ghani Abbas Ericsson

- Arne Alping Ericsson

- Ralf-Peter Braun Deutsche Telekom

- Martin Carroll Verizon

- Mike Dudek JDSU

- Jörg-Peter Elbers Adva

- Joel Goergen Force10

- John Jaeger Infinera

- Jack Jewell JDSU

- Jeff Maki Juniper Networks

- George Young AT&T

- Mark Nowell CISCO

- Gary Nicholl CISCO

- Shoichi Ogita Eudyna

- Thomas Paatzsch Cube Optics

- Shashi Patel Foundry Networks

- Bill Ryan Foundry Networks

- Sam Sambasivan AT&T

- Henk Steenman AMS-IX

- Eddie Tsumura ExceLight

- George Young AT&T

- Ted Woodward Telcordia

### 40km SMF Outline

- Status

- Architecture

- LAN WDM Baseline (-10nm) Grid

- 40km Baseline Grid Link and Power Budget

<u>The following appendices have NOT been reviewed by the presentation co-</u> <u>authors (other then the lead author) and supporters, so their co-authorship</u> <u>and support does not necessarily apply to any of the appendices</u>

- Appendix 1: LAN WDM Reference (0nm) Grid and Power Budget

- Appendix 2: LAN WDM -5nm Grid and Power Budget

- Appendix 3: LAN WDM -15nm Grid and Power Budget

- Appendix 4: 1310nm EML 40km SMF Dispersion Tolerance Measurements

- Appendix 5: SOA Overload Performance Simulation

### 40km SMF Status

- Baseline Approach to 40km SMF reach

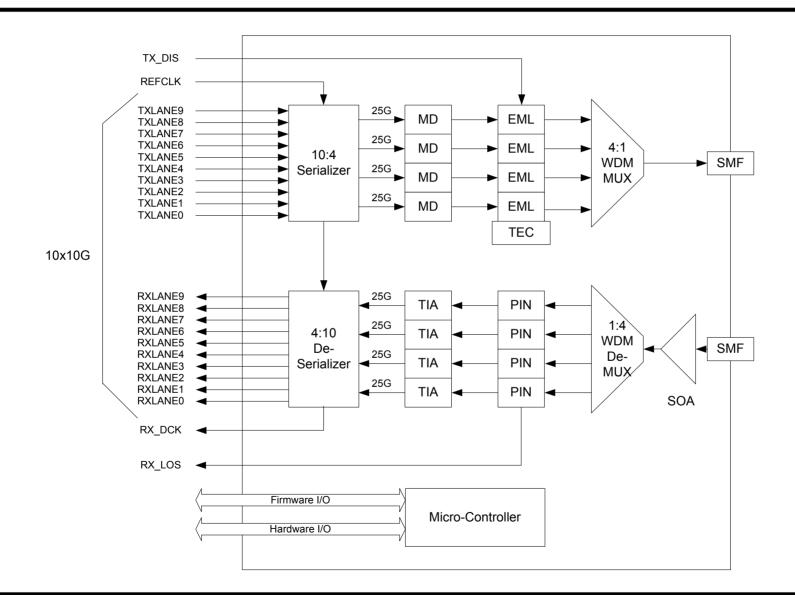

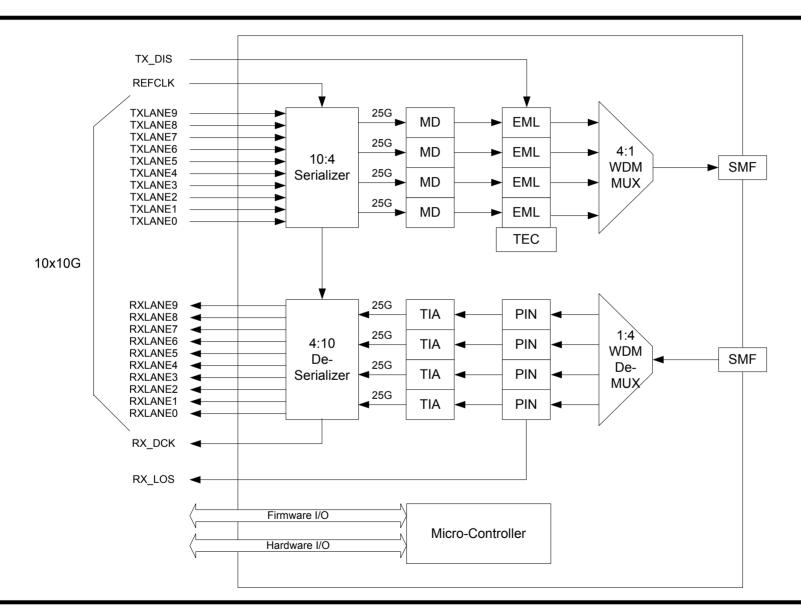

- TX:  $4x25G \text{ MD-EML} \rightarrow \text{LAN WDM Mux}$

- RX: 4x25G PIN-TIA  $\leftarrow$  LAN WDM DeMux  $\leftarrow$  SOA

- Technical presentations discussing baseline approach

- cole\_01\_1106, cole\_02\_0107, cole\_01\_0407, cole\_01\_0507, cole\_01\_0907, cole\_02\_0108

- traverso\_01\_0407

- jiang\_01\_0507, jiang\_01\_0907

- gutierrez\_01\_0507, gutierrez\_01/02/03/04\_1107

- matsumoto\_01\_1107

- nagarajan\_01\_1107

- johnson\_01\_0108

- anslow\_01\_0308

- Key Issues analyzed

- Min receiver sensitivity

- Non-linear effects

- Overload

- PMD Penalty

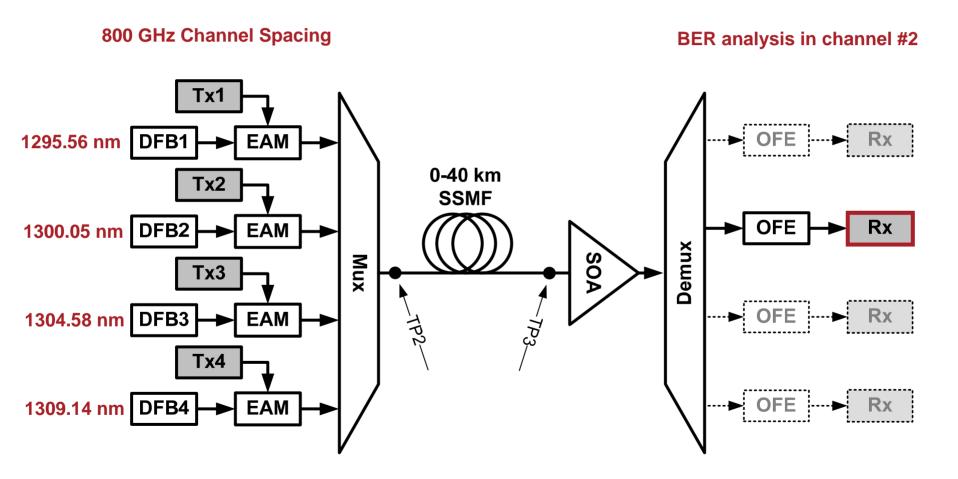

## Gen1 40km 4x25G 1310nm Transceiver Architecture

# LAN WDM Baseline (-10nm) Grid

- ITU G.694.1 specification

- 800GHz spacing (193.1THz base)

- 4 wavelengths shifted by -10nm from Reference Grid

- Exact wavelength values: 1295.56 1300.05 1304.58 1309.14 nm

- Shorthand wavelength values: 1295, 1300, 1305, 1310 nm

- 2nm window (precise pass-band TBD)

- G.652 A&B 40km SMF worst dispersion and fiber loss

- Max positive dispersion (1310nm) = 36ps/nm

- Max negative dispersion (1295nm) = -114ps/nm

- Max Loss (1310nm) = 16.8dB

- Max Loss (1295nm) = 17.3dB

## 40km Baseline Grid Power Budget

| 25G Link Budget<br>40km SMF<br>TP2 → TP3<br>dB | LAN WDM<br>EML chirp $\alpha$ = -0.5<br>$\lambda$ = 1295nm<br>ER = 8dB | 25G Pwr. Budget<br>40km SMF<br>TP2 $\rightarrow$ TP3<br>OMA (Average) dBm | LAN WDM<br>EML chirp $\alpha$ = -0.5<br>$\lambda$ = 1295nm<br>ER = 8dB |

|------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------|

| Fiber Loss (G.652<br>A&B)                      | 17.3                                                                   | TX Min [Max]                                                              | 2.6 (1.0) [5.6 (4.0)]                                                  |

| Connector loss                                 | 2.0                                                                    | TP2 TX Min [Max]<br>2.5dB Mux loss                                        | 0.1 (-1.5) [4.1 (2.5)]                                                 |

| Dispersion Penalty                             | 1.5                                                                    | Link Budget (dB)                                                          | 22.5 dB                                                                |

| Other Penalties<br>(TX, PMD)                   | 1.7                                                                    | TP3 RX Min                                                                | -22.4 (-24.0)                                                          |

| Total budget                                   | 22.5 dB                                                                | RX Min (with 1dB crosstalk penalty)                                       | -10.2 (-11.8) dBm                                                      |

- EML chirp range assumption:  $-0.5 \le \alpha \le 1.0$

- 1.5 dB Dispersion Penalty and 1dB PMD in Other Penalties needs further quantification

- Min attenuation = 0dB assumption subject to verification of SOA WDM overload at low bias

- RX overload, max difference in power between wavelengths, other specs TBD

# Appendix 1: LAN WDM Reference (0nm) Grid

- ITU G.694.1 specification

- 800GHz spacing (193.1THz base)

- 4 wavelengths selected for minimum dispersion in 1310nm window

- Exact wavelength values: 1305.72, 1310.28, 1314.88, 1319.51 nm

- Shorthand wavelength values: 1305, 1310, 1315, 1320 nm

- 2nm window

- G.652 A&B 40km SMF worst dispersion and fiber loss

- Max positive dispersion (1320nm) = 75ps/nm

- Max negative dispersion (1305nm) = -74ps/nm

- Max Loss (1320nm) = 17dB

- Reference Grid is used as basis for comparison of alternate grid proposals

### 40km Reference Grid Power Budget

| 25G Link Budget<br>40km SMF<br>TP2 → TP3 | LAN WDM<br>EML chirp $\alpha = 1.0$<br>$\lambda = 1320$ nm<br>ER = 8dB | 25G Pwr. Budget<br>40km SMF<br>TP2 → TP3<br>OMA (Average) | LAN WDM<br>EML chirp $\alpha = 1.0$<br>$\lambda = 1320$ nm<br>ER = 8dB |

|------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------|

| Fiber Loss (G.652<br>A&B)                | 17 dB                                                                  | TX Min                                                    | 2.6 (1.0) dBm                                                          |

| Connector loss                           | 2.0                                                                    | TP2 TX Min<br>2.5dB Mux loss                              | 0.1 (-1.5)                                                             |

| Dispersion Penalty                       | 2.0                                                                    | Link Budget (dB)                                          | 22.7 dB                                                                |

| Other Penalties<br>(TX, PMD)             | 1.7                                                                    | TP3 RX Min                                                | -22.6 (-24.2)                                                          |

| Total budget                             | 22.7 dB                                                                | RX Min (with 1dB crosstalk penalty)                       | -10.2 (-11.8) dBm                                                      |

# Appendix 2: LAN WDM -5nm Grid

- ITU G.694.1 specification

- 800GHz spacing (193.1THz base)

- 4 wavelengths shifted by -5nm from Reference Grid

- Exact wavelength values: 1300.62, 1305.15, 1309.71, 1314.3 nm

- Shorthand wavelength values: 1300, 1305, 1310, 1315 nm

- 2nm window

- G.652 A&B 40km SMF worst dispersion and fiber loss

- Max positive dispersion (1315nm) = 56ps/nm

- Max negative dispersion (1300nm) = -92ps/nm

- Max Loss (1315nm) = 16.6dB

- Max Loss (1300nm) = 17.1dB

## 40km -5nm Grid Power Budget

| 25G Link Budget<br>40km SMF<br>TP2 → TP3<br>dB | LAN WDM<br>EML chirp $\alpha$ = -0.5<br>$\lambda$ = 1300nm<br>ER = 8dB | 25G Pwr. Budget<br>40km SMF<br>TP2 $\rightarrow$ TP3<br>OMA (Average) dBm | LAN WDM<br>EML chirp $\alpha$ = -0.5<br>$\lambda$ = 1300nm<br>ER = 8dB |

|------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------|

| Fiber Loss (G.652<br>A&B)                      | 17.1                                                                   | TX Min [Max]                                                              | 2.6 (1.0) [5.6 (4.0)]                                                  |

| Connector loss                                 | 2.0                                                                    | TP2 TX Min [Max]<br>2.5dB Mux loss                                        | 0.1 (-1.5) [4.1 (2.5)]                                                 |

| Dispersion Penalty                             | 1.2                                                                    | Link Budget (dB)                                                          | 22 dB                                                                  |

| Other Penalties<br>(TX, PMD)                   | 1.7                                                                    | TP3 RX Min                                                                | -21.9 (-23.5)                                                          |

| Total budget                                   | 22 dB                                                                  | RX Min (with 1dB crosstalk penalty)                                       | -10.2 (-11.8) dBm                                                      |

- EML chirp assumption:  $-0.5 \le \alpha \le 1.0$

- 1.2 dB Dispersion Penalty and 1dB PMD in Other Penalties needs further quantification

- EML  $\lambda$  = 1315nm, chirp = 1.0: Dispersion Penalty = 1.5dB, Fiber Loss = 16.6dB

# Appendix 3: LAN WDM -15nm Grid

- ITU G.694.1 specification

- 800GHz spacing (193.1THz base)

- 4 wavelengths shifted by -15nm from Reference Grid

- Exact wavelength values: 1290.54, 1295.00, 1299.49, 1304.01 nm

- Shorthand wavelength values: 1290, 1295, 1300, 1305 nm

- 2nm window

- G.652 A&B 40km SMF worst dispersion and fiber loss

- Max positive dispersion (1305nm) = 19.2ps/nm

- Max negative dispersion (1290nm) = -134ps/nm

- Max Loss (1305nm) = 16.9dB

- Max Loss (1290nm) = 17.6dB

## 40km -15nm Grid Power Budget

| 25G Link Budget<br>40km SMF<br>TP2 → TP3<br>dB | LAN WDM<br>EML chirp $\alpha$ = -0.5<br>$\lambda$ = 1290nm<br>ER = 8dB | 25G Pwr. Budget<br>40km SMF<br>TP2 $\rightarrow$ TP3<br>OMA (Average) dBm | LAN WDM<br>EML chirp $\alpha$ = -0.5<br>$\lambda$ = 1290nm<br>ER = 8dB |

|------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------|

| Fiber Loss (G.652<br>A&B)                      | 17.6                                                                   | TX Min [Max]                                                              | 2.6 (1.0) [5.6 (4.0)]                                                  |

| Connector loss                                 | 2.0                                                                    | TP2 TX Min [Max]<br>2.5dB Mux loss                                        | 0.1 (-1.5) [4.1 (2.5)]                                                 |

| Dispersion Penalty                             | 1.7                                                                    | Link Budget (dB)                                                          | 23.0 dB                                                                |

| Other Penalties<br>(TX, PMD)                   | 1.7                                                                    | TP3 RX Min                                                                | -22.9 (-24.5)                                                          |

| Total budget                                   | 23.0 dB                                                                | RX Min (with 1dB crosstalk penalty)                                       | -10.2 (-11.8) dBm                                                      |

- EML chirp assumption:  $-0.5 \le \alpha \le 1.0$

- 1.7dB Dispersion Penalty and 1dB PMD in Other Penalties needs further quantification

- EML  $\lambda$  = 1305nm Dispersion Penalty = 0.6dB, Fiber Loss = 16.9dB

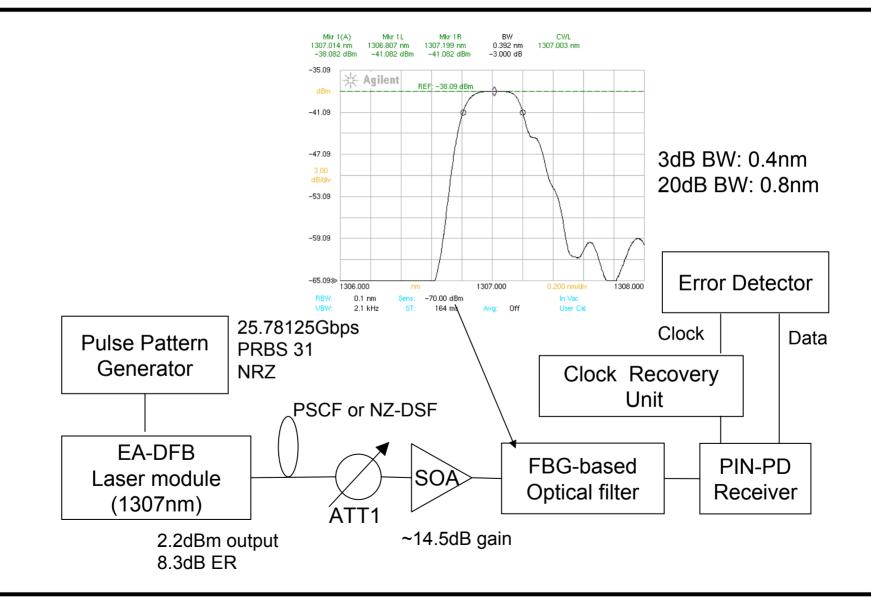

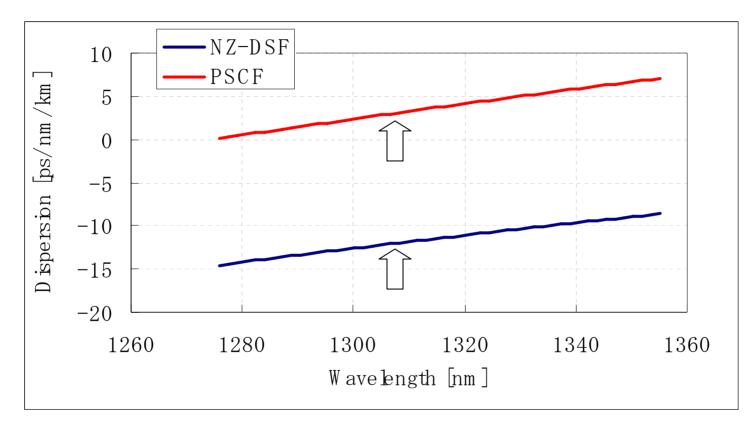

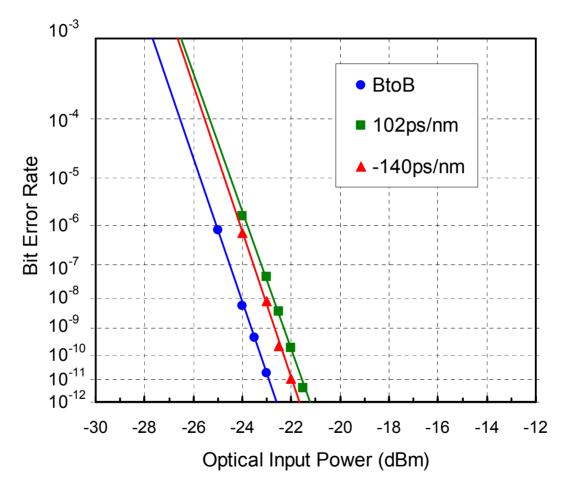

Appendix 4: Dispersion Penalty Measurements

1310nm band EML Dispersion Tolerance Measurement Result over 40km SMF

100GE 40km PMD

Hirotaka Oomori (Sumitomo Electric Industries, Ltd.)

Eddie Tsumura (ExceLight Communications, Inc.)

### **Test Setup**

- NZ-DSF: Non Zero Dispersion Shifted Fiber

- PSCF: Pure Silica Core Fiber

1.4dB penalty @102ps/nm

0.9dB penalty @-140ps/nm

13-15 May 2008

Gain-controlled SOA performance High input power conditions 100 GbE 40-km PMD Ramón Gutiérrez-Castrejón Universidad Nacional Autonoma de Mexico-UNAM email: RGutierrezC@ii.unam.mx

For the analysis we have considered:

- Extinction ratio = 8 dB

- Optical signal-to-noise ratio = 40 dB

- High and low EML output powers = +5.6 dBm, +2.6 dBm

- Insertion loss MUX = 2.5 dB

- Insertion loss DEMUX = 5.2 dB

| EML Output Power         | +5.6 dBm | +2.6 dBm |

|--------------------------|----------|----------|

| Per Channel Power at TP2 | +3.1 dBm | +0.1 dBm |

| Total Power at TP2       | 9.1 dBm  | 6.1 dBm  |

- BER vs. SOA injection current analysis

- Current varied in (50 mA ,...,100 mA), corresponding to small-signal gain in (4 dB,...,18 dB). Lower bound determined by SOA model.

- Four fiber lengths analyzed: 0, 0.001, 5 and 10 km

- Fiber Characteristics: losses: 0.45 dB/km (+ 2 dB connector), dispersion coefficient @ 1310 nm: D = -0.20 ps/nm/km, dispersion slope @ 1310 nm: S = 0.090 ps/nm<sup>2</sup>/km

- Analysis for

- <u>High</u> power transmitters: All channels at 5.6 dBm

- Low power Transmitters: All channels at 2.6 dBm

- <u>Combined</u> power: All channels at 5.6 dBm, but Tx2\*\* at 2.6 dBm

- Special test bit pattern of 2^10-1 bits. See gutierrez\_01\_1107.

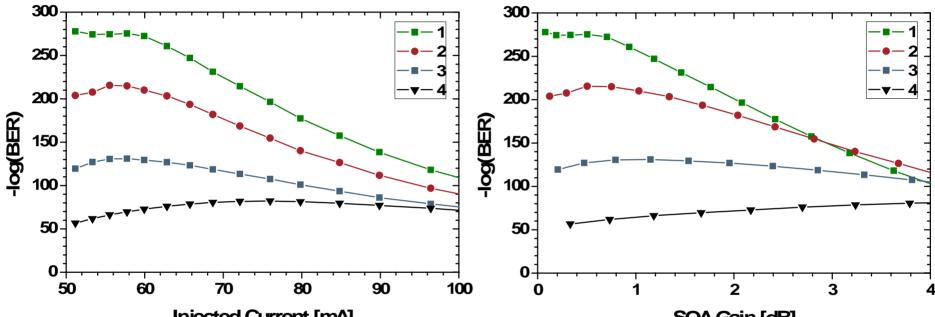

### BER Performance: <u>High</u> Power Transmitter (5.6 dBm)

Injected Current [mA]

SOA Gain [dB]

| Curve | Fiber Length | Fiber Losses | SOA Input Power (Tot) |  |  |

|-------|--------------|--------------|-----------------------|--|--|

| 1     | 0 km         | 0 dB         | +9.10 dBm             |  |  |

| 2     | 0.001 km     | 2 dB         | +7.10 dBm             |  |  |

| 3     | 5 km         | 4.25 dB      | +4.85 dBm             |  |  |

| 4     | 10 km        | 6.50 dB      | +2.60 dBm             |  |  |

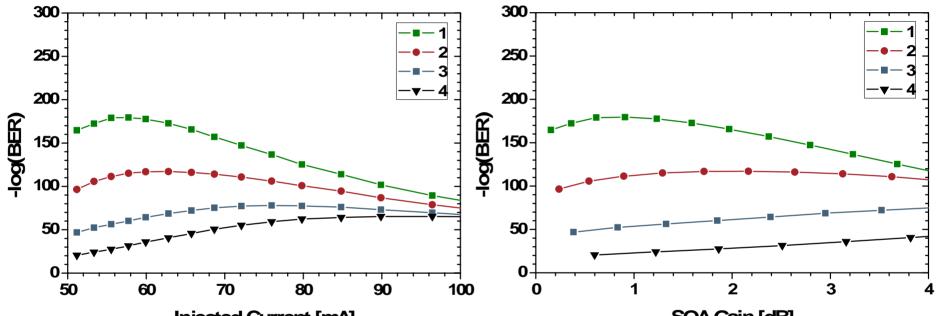

### BER Performance: Low Power Transmitter (2.6 dBm)

Injected Current [mA]

SOA Gain [dB]

| Curve | Fiber Length | Fiber Losses | SOA Input Power (Tot) |  |  |

|-------|--------------|--------------|-----------------------|--|--|

| 1     | 0 km         | 0 dB         | +6.10 dBm             |  |  |

| 2     | 0.001 km     | 2 dB         | +4.10 dBm             |  |  |

| 3     | 5 km         | 4.25 dB      | +1.85 dBm             |  |  |

| 4     | 10 km        | 6.50 dB      | -0.40 dBm             |  |  |

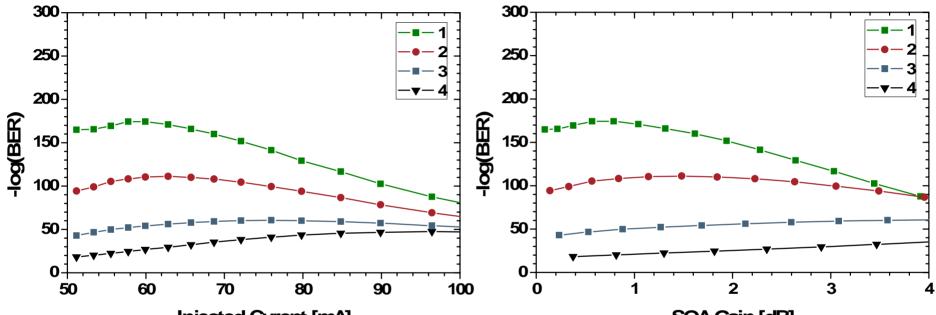

#### BER Performance: High Power w/Low Power @ Tx8

Injected Curent [mA]

SOA Gain [dB]

| Curve | Fiber Length | Fiber Losses | SOA Input Power (Tot) |  |  |

|-------|--------------|--------------|-----------------------|--|--|

| 1     | 0 km         | 0 dB         | +8.50 dBm             |  |  |

| 2     | 0.001 km     | 2 dB         | +6.50 dBm             |  |  |

| 3     | 5 km         | 4.25 dB      | +4.25 dBm             |  |  |

| 4     | 10 km        | 6.50 dB      | +2.00 dBm             |  |  |

### **Appendix 5 Conclusion**

- The SOA gain-control scheme exhibits excellent performance for high optical powers

- Good system BER performance for a wide range of current values no need for highly accurate control

- The SOA gain-control scheme operates correctly even above the transparency point (Gain > 0 dB)

- Single intermediate current value (e.g. 100 mA correspond to 18 dB of smallsignal gain) is good enough for fiber lengths ranging from 0 to 10 km and even longer

- Results depends on SOA characteristics

- Measurements required to confirm findings

# 100GE 10km SMF PMD

# IEEE 802.3ba Task Force 13-15 May 2008

Chris Cole - Finisar Bernd Huebner - Finisar Pete Anslow - Nortel John Johnson - CyOptics Radha Nagarajan - Infinera Hirotaka Oomori - Sumitomo

## Supporters

- Ghani Abbas Ericsson

- Arne Alping Ericsson

- Ralf-Peter Braun Deutsche Telekom

- Mike Dudek JDSU

- Jörg-Peter Elbers Adva

- Joel Goergen Force10

- John Jaeger Infinera

- Jack Jewell JDSU

- Jeff Maki Juniper Networks

- Arlon Martin Kotura

- Mark Nowell CISCO

- Gary Nicholl CISCO

- Thomas Paatzsch Cube Optics

- Shashi Patel Foundry Networks

- Bill Ryan Foundry Networks

- Sam Sambasivan AT&T

- Henk Steenman AMS-IX

- Eddie Tsumura ExceLight

- George Young AT&T

- Ted Woodward Telcordia

#### Outline

- Status

- Architecture

- LAN WDM Baseline (-10nm) Grid

- 10km Baseline Grid Link and Power Budget

- <u>The following appendices have NOT been reviewed by the presentation co-</u> <u>authors (other then the lead author) and supporters, so their co-authorship</u> <u>and support does not necessarily apply to any of the appendices</u>

- Appendix 1: LAN WDM Reference (0nm) Grid

- 10km Reference Grid Link and Power Budget

- Appendix 2: LAN WDM -5nm Grid

- 10km -5nm Grid Link and Power Budget

- Appendix 3: LAN WDM -15nm Grid

- 10km -15nm Grid Link and Power Budget

## 10km SMF Status

- Baseline Approach to 10km SMF reach

- TX:  $4x25G \text{ MD-EML} \rightarrow \text{LAN WDM Mux}$

- RX: 4x25G PIN-TIA  $\leftarrow$  LAN WDM DeMux

- Technical presentations discussing baseline approach

- cole\_01\_1106, cole\_01\_0307, cole\_01\_0907, cole\_01/02\_0108, cole\_01/02\_0308

- jiang\_01\_0507, jiang\_01\_0907

- nagarajan\_01\_1107

- johnson\_01\_0108

Many other presentations discussed 4x25G MD-EML approach, but on a CWDM Grid

- Key Issues analyzed

- Min receiver sensitivity

- Transmitter output power

- DML feasibility

- Dispersion Penalty

- Integration approaches

## Gen1 10km 1310nm EML PMD

# LAN WDM Baseline (-10nm) Grid

- ITU G.694.1 specification

- 800GHz spacing (193.1THz base)

- 4 wavelengths shifted by -10nm from Reference Grid

- Exact wavelength values: 1295.56 1300.05 1304.58 1309.14 nm

- Shorthand wavelength values: 1295, 1300, 1305, 1310 nm

- 2nm window (precise pass-band TBD)

- G.652 A&B 10km SMF worst corner dispersion and fiber loss

- Max positive dispersion (1310nm) = 9ps/nm

- Max negative dispersion (1295nm) = -28ps/nm

- Max Loss (1310nm) = 4.2dB

- Max Loss (1295nm) = 4.3dB

## 10km Baseline Grid Power Budget

| 25G Link Budget<br>10km SMF<br>TP2 → TP3 | LAN WDM<br>EML $\alpha$ = -1.0<br>$\lambda$ = 1295nm<br>ER = 7dB | LAN WDM<br>DML $\alpha$ = 3.5<br>$\lambda$ = 1310nm<br>ER = 4.5dB |  | 25G Pwr Budget<br>10km SMF<br>TP2 → TP3<br>OMA (Average) | LAN WDM<br>EML $\alpha$ = -1.0<br>$\lambda$ = 1295nm<br>ER = 7dB | LAN WDM<br>DML $\alpha$ = 3.5<br>$\lambda$ = 1310nm<br>ER = 4.5dB |

|------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------|--|----------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------|

| Fiber Loss<br>(G.652 A&B)                | 4.3 dB                                                           | 4.2 dB                                                            |  | TX Min                                                   | 2.3 dBm<br>(1.1)                                                 | 2.3 dBm<br>(2.5)                                                  |

| Connector loss                           | 2.0                                                              | 2.0                                                               |  | TP2 TX Min<br>2.5dB Mux loss                             | -0.2                                                             | -0.2                                                              |