PM2-1ET080190-00

# XLAUI/CAUI Jitter Tolerance Test Proposal

# IEEE P802.3ba 12 to 16 January 2009

Toshihiro SUZUKI - Anritsu Corporation

Discover What's Possible™

1

# Introduction

- \* There are two Editor's Note on 83A 5.2.2.

- \* Those are interference tolerance test and jitter tolerance test pattern. This proposal resolves these two unclear items.

#### 83A.5.2.2 Jitter tolerance

[Editor's note: (to be removed prior to publication) - An interference tolerance test is required]

[Editor's note: (to be removed prior to publication) -In addition to PRBS31, consider including appropriate patterns when performing jitter measurements e.g., MLD and other representative patterns.]

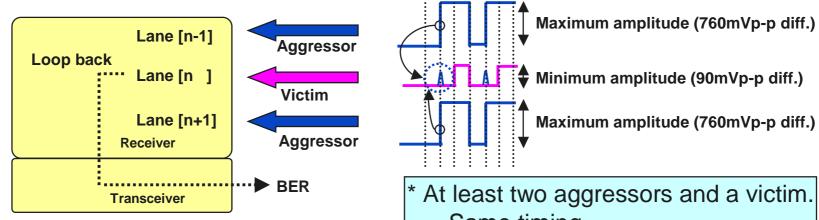

### Interference tolerance test system proposal

Table 83A–1—Transmitter characteristics

| Parameter                                         | Value                      | Units |

|---------------------------------------------------|----------------------------|-------|

| Signalling speed per lane (range)                 | $10.3125\pm100\text{ ppm}$ | GBd   |

| Single-ended output voltage range                 |                            |       |

| maximum                                           | 4.0                        | V     |

| minimum                                           | -0.4                       | V     |

| Maximum Differential Output Voltage, peak-to-peak | 760                        | mV    |

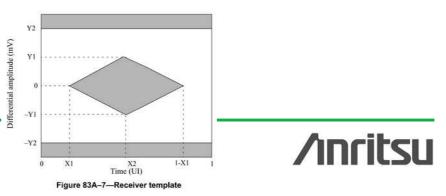

Table 83A–2—Receiver characteristics

| Parameter                                    | Value                            | Units |

|----------------------------------------------|----------------------------------|-------|

| Signalling speed per lane (range)            | 10.3125 ± 100 ppm                | GBd   |

| Minimum Differential Input Voltage, p-p      | See receiver eye mask definition | mV    |

| Receiver eye mask definition Y1 <sup>d</sup> | 45                               | mV    |

- Same timing

- Aggressors

- Maximum amplitude

- Same pattern PRBS 23

- \* A victim

- Minimum amplitude

- PRBS 31

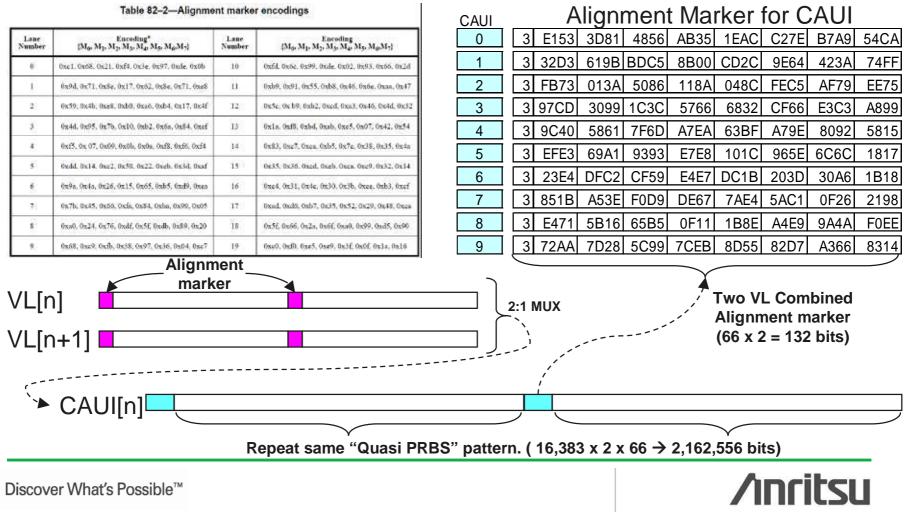

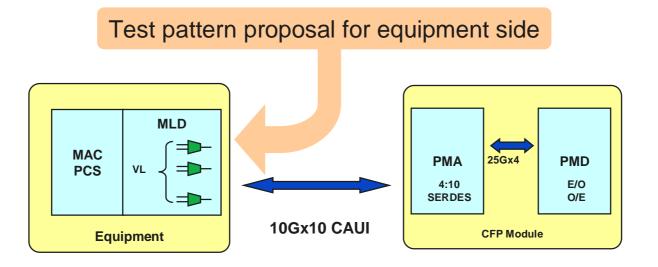

# **Jitter Tolerance Test Pattern Proposal**

- \* PRBS31 is good enough for testing jitter tolerance of optical module side. It is just simple physical characteristics test.

- \* For equipment side, test pattern should be included "Alignment Marker" to drive alignment circuit.

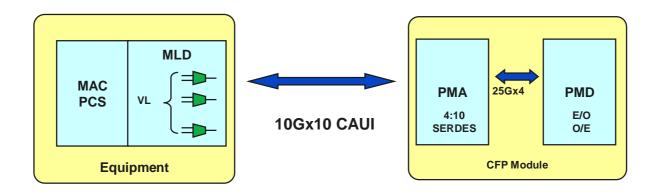

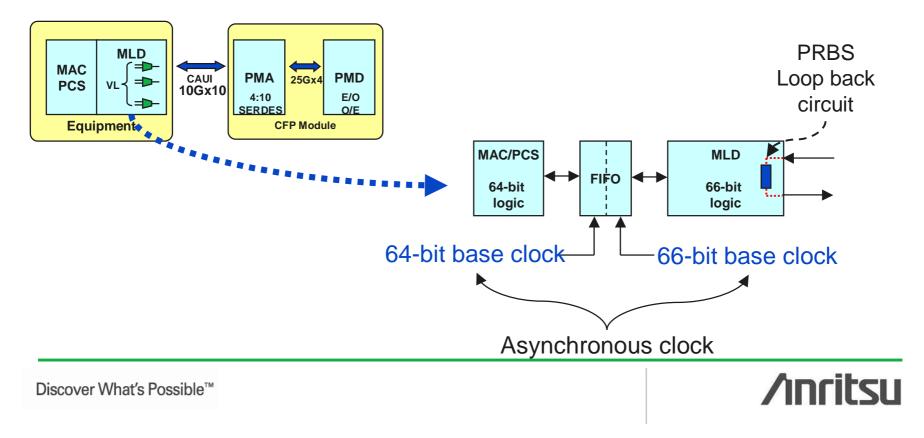

# **Equipment Circuit Assumption**

### \* Equipment circuit assumptions

- Skew alignment must be huge logic circuit.

- During PRBS loop back circuit works, alignment circuit does not work.

- PRBS Loop back circuit is smaller than skew alignment circuit.

- The circuit uses at least two asynchronous clocks (64-bit and 66-bit logic).

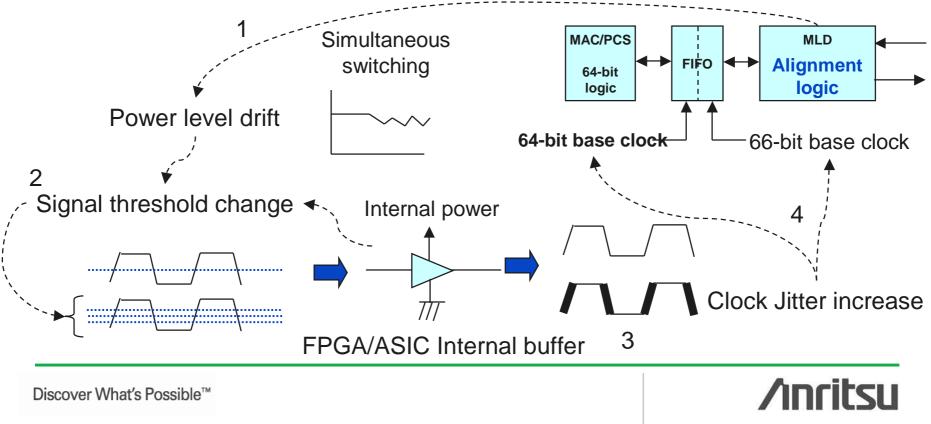

# Increasing jitter inside of large scale logic circuit -1

- -1. Simultaneous switching of large-scale circuit in FPGA/ASIC causes internal power level drift.

- -2. Power level drift changes internal buffer threshold level.

- -3. Jitter on buffer output signal increases.

- -4. The amount of jitter is different between asynchronous clocks (64-base, 66-base)

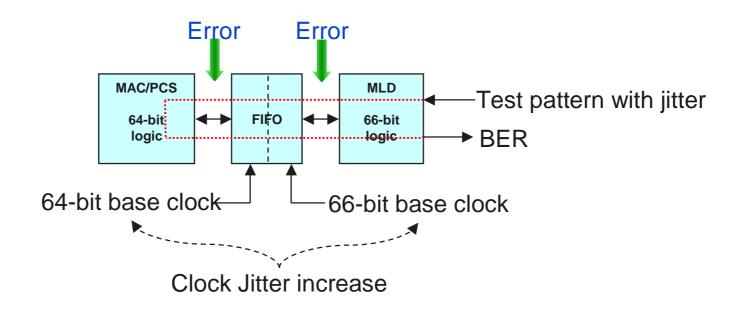

## Increasing jitter inside of large scale logic circuit -2

- The different amount of jitter decrease in phase margin at FIFO. Or it may cause error at FIFO in the worst case.

- To test jitter tolerance under the worst condition, skew alignment circuit should work.

➔ So test pattern should be included "Alignment marker" to drive alignment circuit.

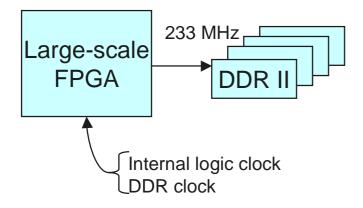

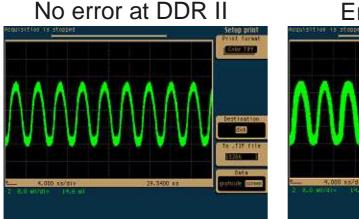

# Increasing jitter inside of large scale logic circuit -3

-- Example --

Simultaneous switching causes internal power level drift between two asynchronous clocks in FPGA causing error at DDR access

Error at DDR II

# **Jitter Tolerance Test Pattern Proposal**

For equipment side, jitter tolerance test pattern should be included "Alignment Marker" to make the worst condition.