XLAUI/CAUI Jitter Tolerance Test Requirement Proposal

> IEEE802.3ba 8 to 15 November 2008

Toshihiro SUZUKI - Anritsu Corporation

/inritsu

1

Discover What's Possible™

# Introduction

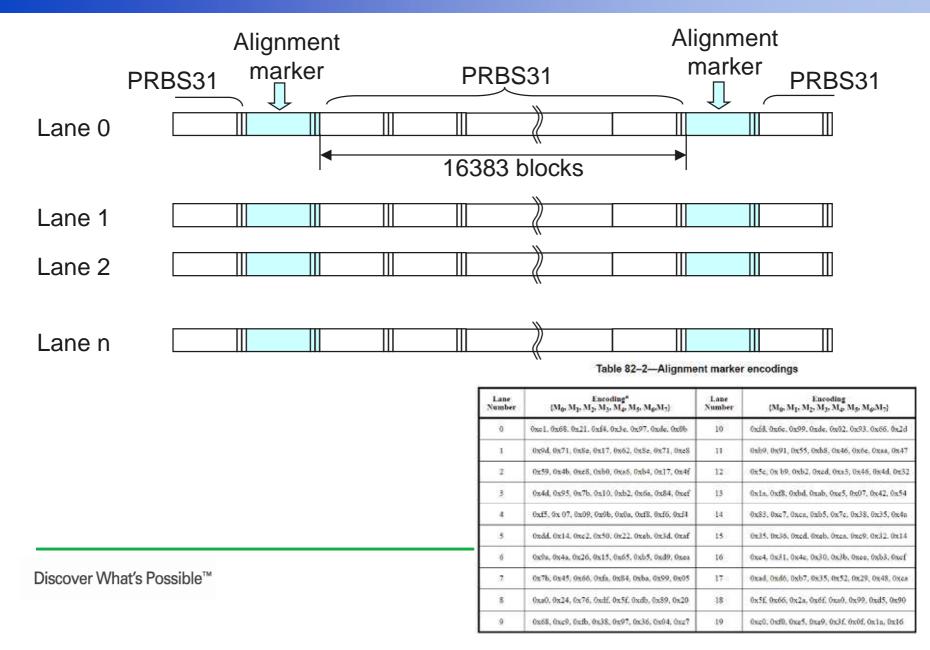

- This presentation proposes a test pattern for the Jitter test requirement in 83A.4.3.2 IEEE802.3ba D1.0.

- Testing should be under the worst conditions to achieve good product reliability.

### 83A.4.3 Jitter test requirements

[Editor's note: (to be removed prior to publication) - Insert or change, to include jitter test requirement

### 83A.4.3.1 Transmit jitter

[Editor's note: (to be removed prior to publication) - Insert or change, to include transmit jitter]

#### 83A.4.3.2 Jitter tolerance

[Editor's note: (to be removed prior to publication) - Insert or change, to include jitter tolerance]

Discover What's Possible™

## /inritsu

# **Jitter Tolerance Test Pattern Proposal**

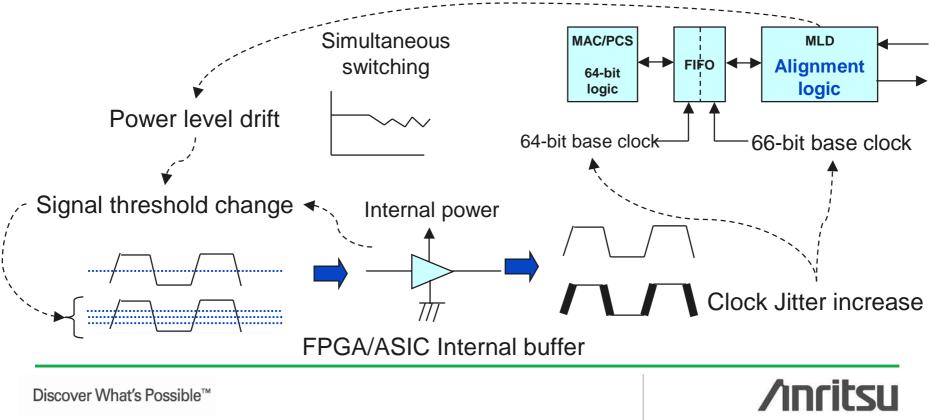

Assumptions about Circuit

- Size of working circuit in MLD block changes according to whether MLD function operating or not

- ·PRBS Loopback test circuit relatively smaller than MLD alignment circuit

- ·Logic circuit uses at least two asynchronous clocks (64-bit and 66-bit logic)

# **Jitter Tolerance Test Pattern Proposal**

- Simultaneous switching of large-scale circuit in FPGA/ASIC causes internal power level drift

- · Power level drift changes internal buffer threshold level

- → Jitter in signal output from buffer increases

# **Jitter Tolerance Test Pattern Proposal**

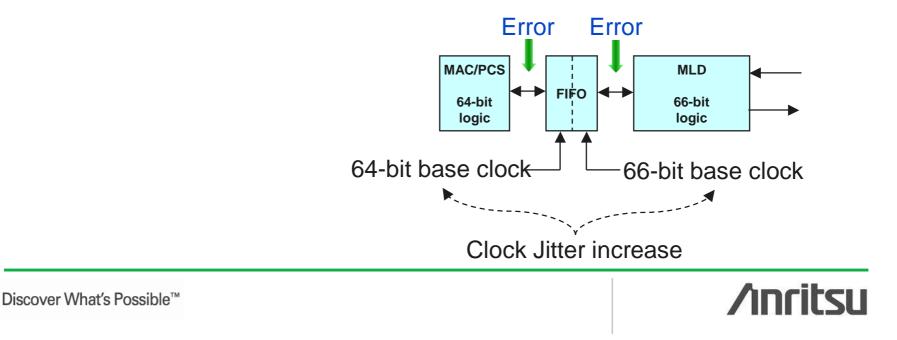

- Different increases in Jitter and timings between two asynchronous clocks (64-bit and 66-bit sides) can cause error at FIFO or decrease in phase margin of internal circuit

- MLD Input pattern increases working logic circuit (MLD alignment)

- Simultaneous switching in FPGA/ASIC increases Jitter causing internal bit errors

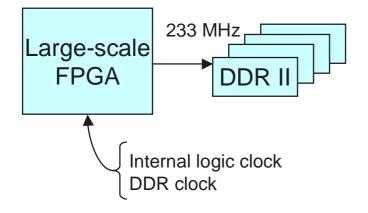

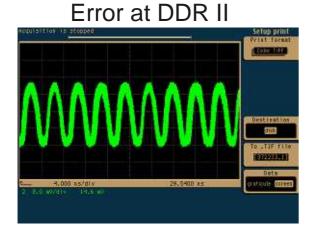

# Simultaneous Switching Increases Jitter

#### Example

Simultaneous switching causes internal power level drift between between two asynchronous clocks in FPGA causing error at DDR access

### No error at DDR II

Test Jitter tolerance under worst condition

Discover What's Possible™

## **Jitter Tolerance Test Pattern**

7