# Return loss at TP2 for 100GBASE-CR4

Mike Dudek - QLogic Nikhil Patel - QLogic

Liav Ben Artsi - Marvell Israel ltd.

Richard Mellitz – Intel Corporation

802.3bj March 2014 - Beijing

# Outline

This presentation investigates the return loss specification at TP2 in 802.3bj draft 3.1 and compares it with the COM model as well as with a synthetic model. It is in support of comment r01-49

The process is as follows (1-3 already discussed during the preparation meetings, 4-5 added).

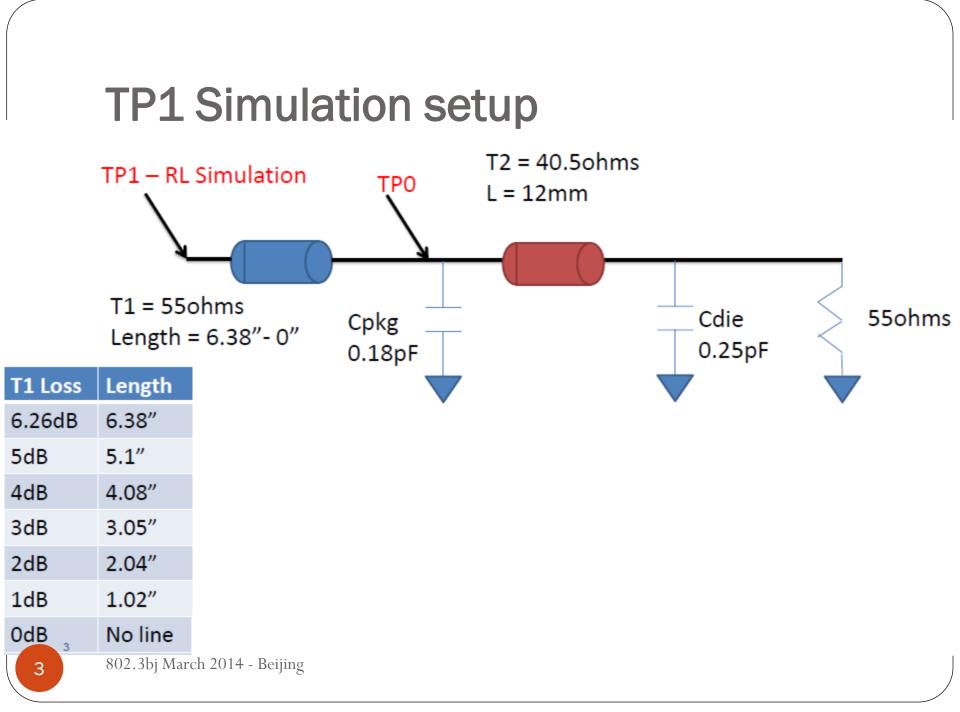

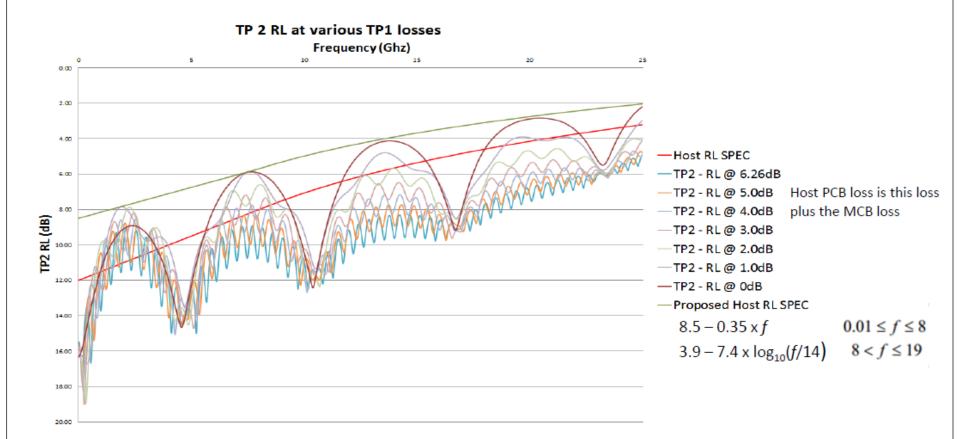

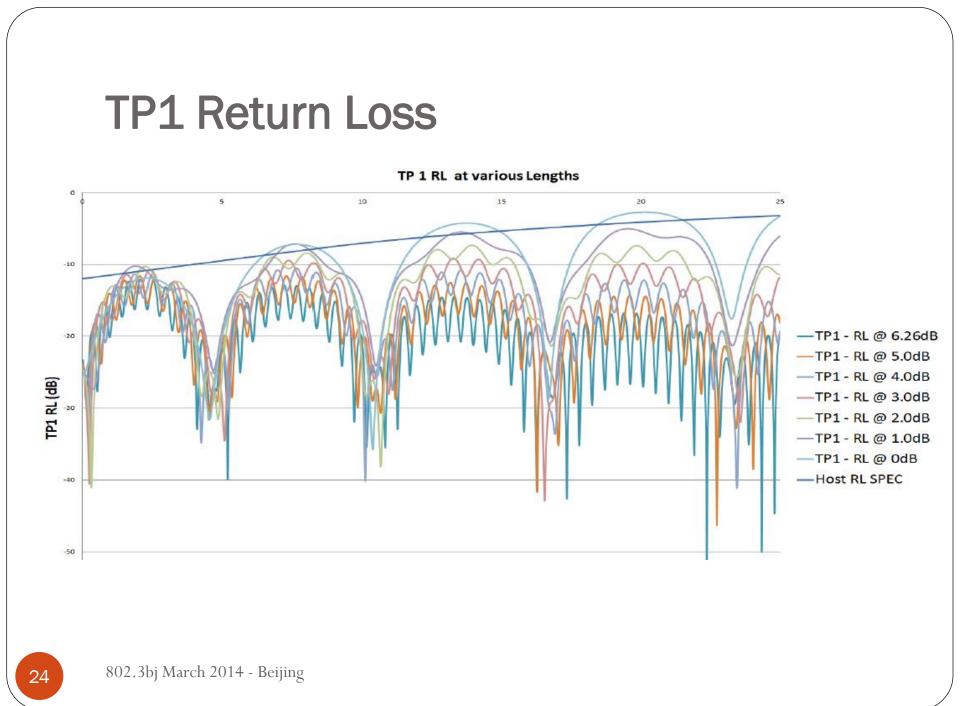

- 1. A representation of the COM model was used for TPO. A representative PCB Tline model was used to get from TPO to TP1. The length of the transmission line was varied to provide losses that varied from zero to the loss used for the COM Cable calculation. This is to represent hosts with trace lengths with the same loss as the MCB (same as the recommended min loss of the host within <0.1dB at all frequencies) to the recommended max loss of the host.

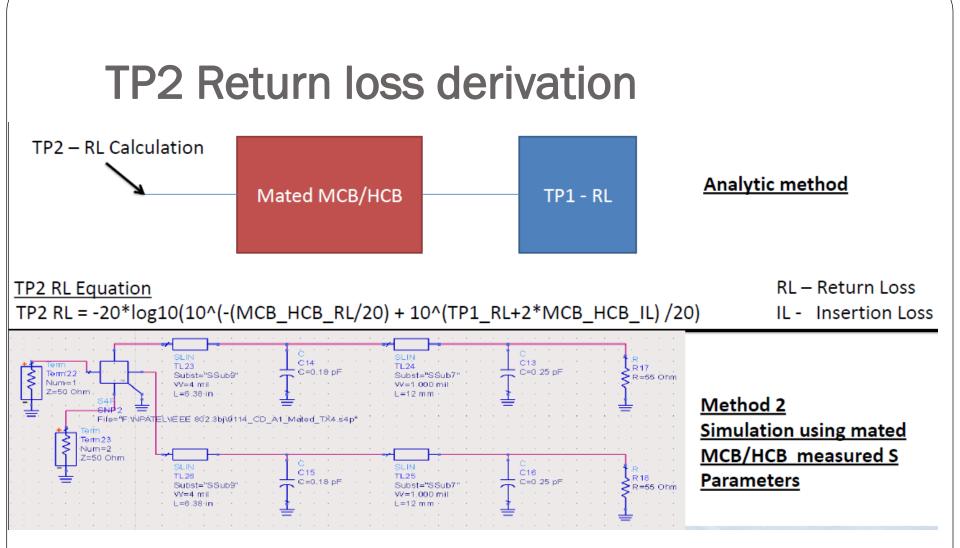

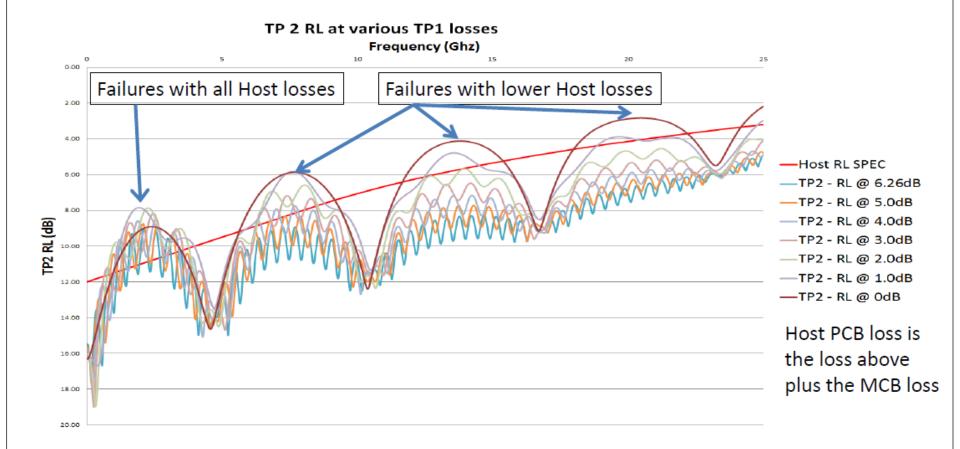

- 2. Analytical calculations (assuming worst case addition of reflections from the mated MCB/HCB and TP1) were used to generate the return loss at TP2, which are then compared with the clause 92 specification for the return loss at TP2. Note that this assumes that the host connector has a return loss no worse than the one used on the MCB.

- 3. In addition S parameters from a measured MCB/HCB were concatenated to get from TP1 to TP2 and these were compared with the clause 92 specification for the return loss at TP2.

- 4. Additional simulations and extractions were performed to verify the conclusions and adjust the suggestion for TP2 differential return loss according to a system model that would be as close as possible to actual system while taking into account manufacturing tolerance.

- 5. Cross impedance simulation was done to conclude the worst case manufacturing tolerance related TP2 RL.

## **TP2 Return Loss – Analytic Method**

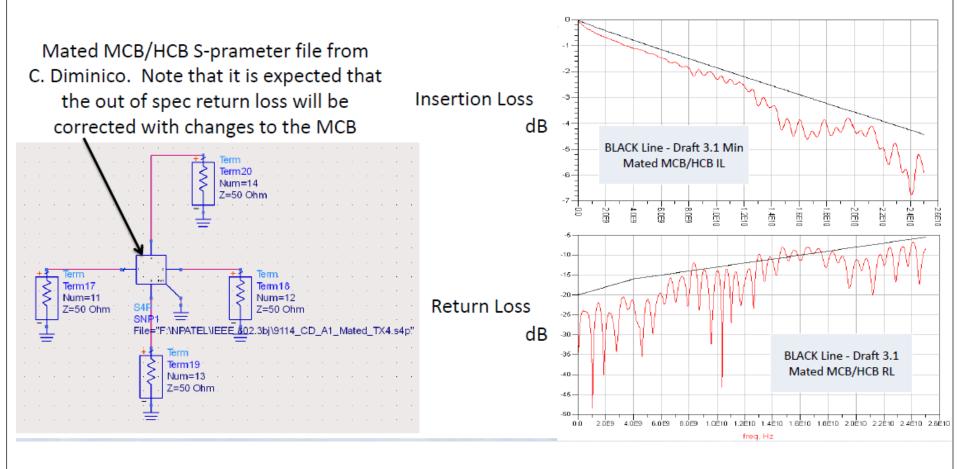

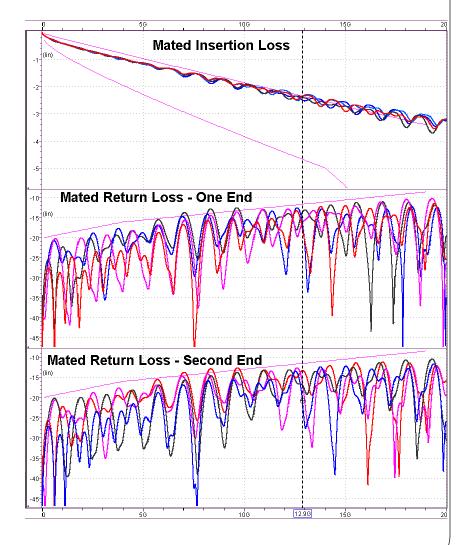

# Mated MCB/HCB S-parameter file

# TP2 Return Loss – Method 2 (measured MCB/HCB)

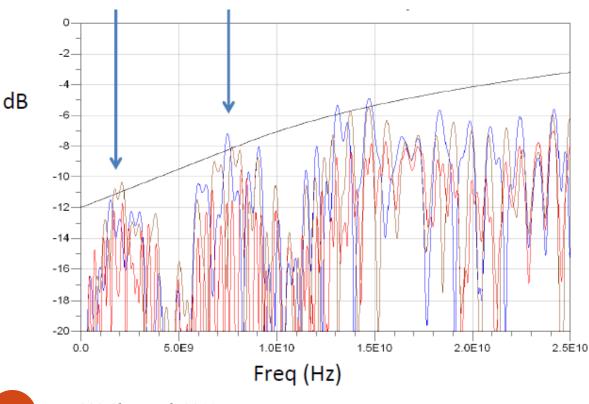

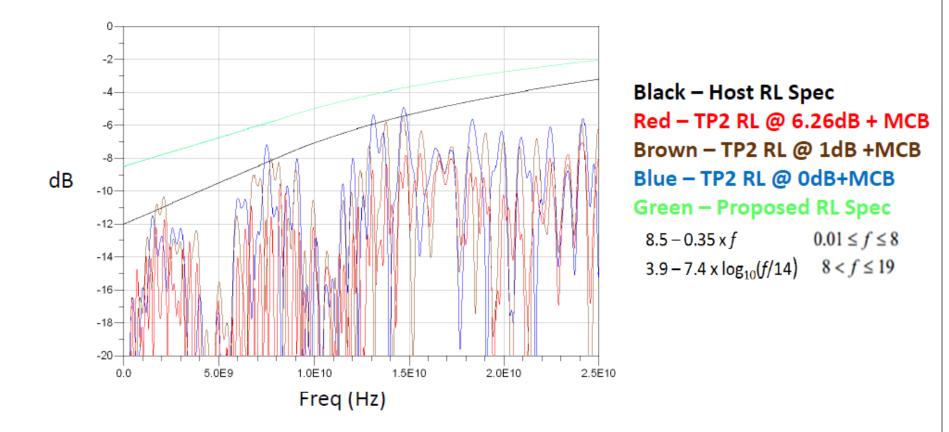

• Fails spec at these frequencies even though HCB/MCB is in spec at these frequencies

Also note that the HCB is above 100 Ohm impedance whereas lower impedance would be worst case.

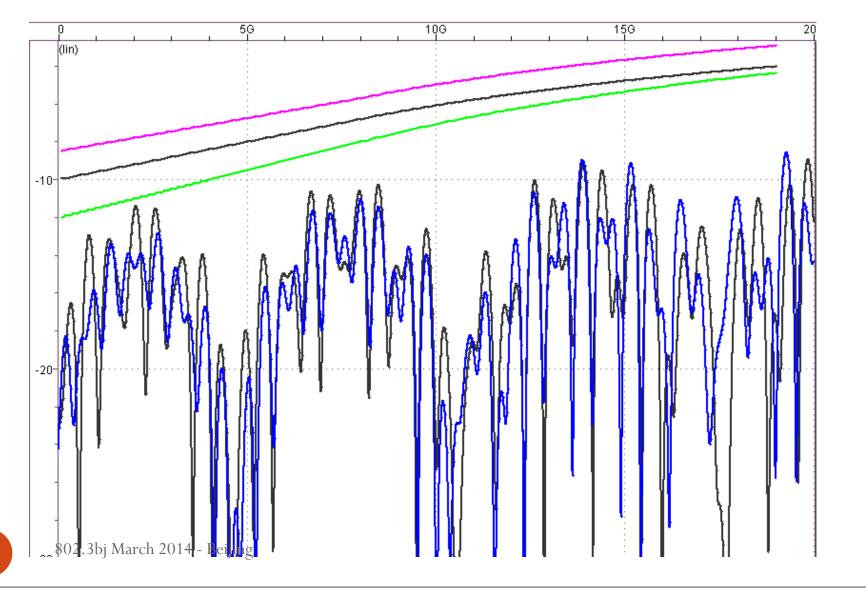

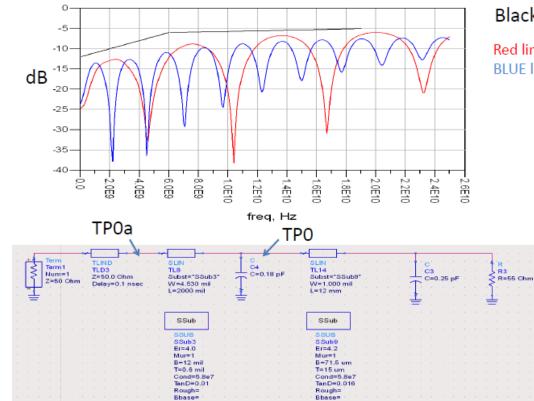

Black – Host RL Spec Red – TP2 RL @ 6.26dB Brown – TP2 RL @ 1dB Blue – TP2 RL @ 0dB

> Host PCB loss is the loss above plus the MCB loss

# **TP2 Return Loss – First Analytic Method**

## TP2 Return Loss – Method 2

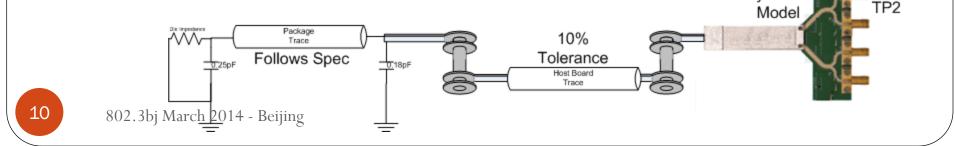

# System Model Assumptions – Method #3

- The following assumptions were taken:

- Package model follows the actual 12 mm package based on the Sparameters used to create the draft 3.1 package model + discontinuities.

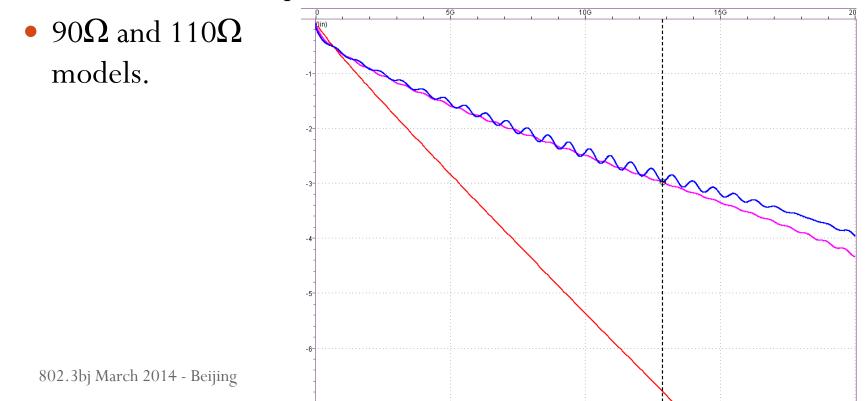

- Host board nominal impedance is  $100\Omega \pm 10\%$  (standard manufacturing tolerance)

- HCB and MCB nominal impedance is  $100\Omega \pm 5\%$  (justification on slide #12)

- Low host board loss will result in worst case return loss @ TP2 and therefore a 3dB (in backup slides)/1.7dB loss cases were taken (Loss from TP0 to the connector inclusive).

Synthetic

Optimized via structures were included in the analysis (10mil stub) @

device break-out and connector.

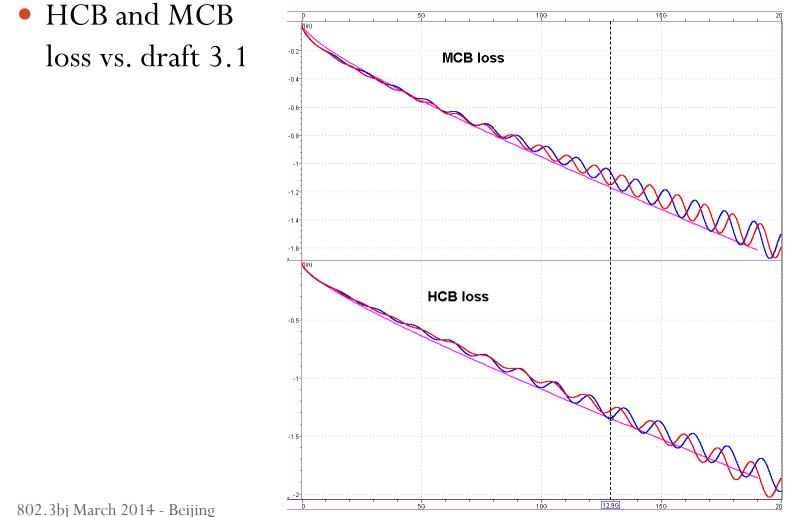

# Models Used for simulation **Compliance Boards**

# Models Used for simulation Mated Compliance Boards

- Mated HCB and MCB Including ±5% impedance manufacturing tolerance (Well justified by the Mated RL result).

- Loss is at the minimum allowed → WC influence on TP2 ret loss.

- Return loss is at the limit, or even with minor violations.

→ WC influence on TP2 ret loss.

- Both conditions above aimed at finding the worst case RL.

- The above justifies that the TP2 suggested RL to be presented on slide #14 is met in worst case conditions provided the host connector is no worse return loss than the MCB connector.

## Examining Extreme Low Host Board Loss

- MCB specification is ~1.2dB @ Nyquist, but MCB, unlike host boards is extremely synthetic and clean.

- Host boards will (the least) have:

- Additional vias (at device break-out and close to the connector)

- Higher trace loss.

- Examining an optimized via structure (Meg6) indicates a loss of ~0.25dB @ Nyquist

- Though further loss may be introduced by ILD (due to vias matching to the trace) let's assume that after concatenating the vias the resulting loss would be the same as an ideal mathematical loss adder → the total loss was tuned to be ~1.7dB @ Nyquist after actually concatenating the vias and the trace.

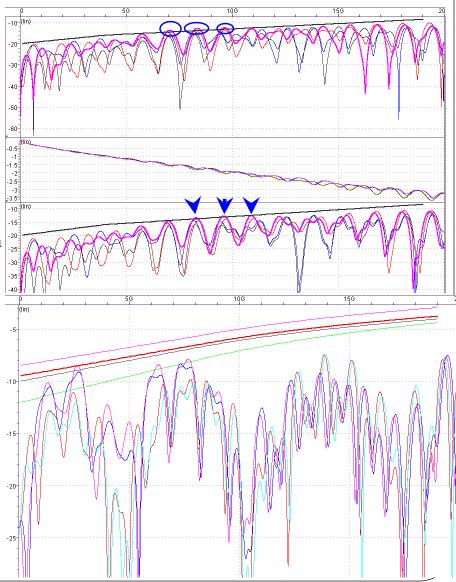

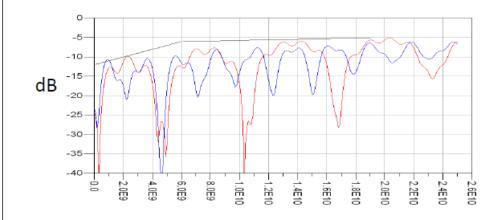

#### Examining Extreme Low Host Board Loss - Cont.

- Initial analysis (The 3dB host loss case see back up) was performed with HCB/MCB tolerance that still had mated RL violations (encircled).

- A further tune to the HCB lowered the amount of violation (It is not reasonable to take margin on top of margin on top on margin... and some violation still exists in this analysis...)

- If this case is to be included a limit is suggested (Red line), Return loss @ TP2 >

9.5 - 0.37\*f

0.01 ≤ f ≤ 8

4.75-7.4\*LOG<sub>10</sub>(f/14)

# Summary, Conclusion and Suggestions

- There is an issue that with a worst case IC and host as used in the COM model for testing cables. The specification for the return loss at TP2 is not met with compliance boards that just meet their specification.

- It is expected that hosts with short traces will perform better than hosts with long traces and therefore should not be an issue. However if there are concerns with this then a cable COM test case could be created to create maximum reflections by using the short package without the TP0 to TP1 transmission line. This new test case would either be in addition to the existing two cases (short and long package with 6.2dBTP0 to TP1 loss) or could replace the existing short package test case.

- A main parameter is the amount of minimal host board loss we define as reasonable. In the analysis a 1.7dB @ Nyquist was considered based on an ideally short trace with two optimized vias.

- To account for impedance variations TP2 return loss limit should be updated. Three possible suggestions were introduced allowing a bit different minimal amount of host trace loss and assumptions.

Suggest Using the equation from slide 14 (Red in graphs), which allows 1.7dB loss with a marginal HCB.

- Since loosening the limit is aimed at allowing low loss host boards to pass with manufacturing tolerance, but will now introduce margin to higher loss boards caution is needed.

- Editorial license granted 802.3bj March 2014 - Beijing

# Backup

802.3bj March 2014 - Beijing

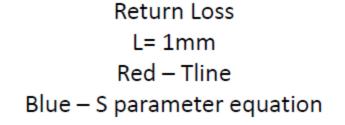

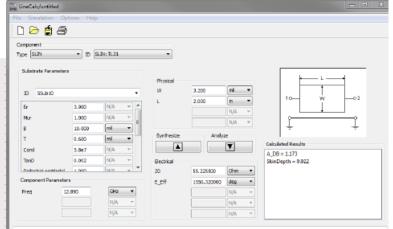

### **Comparing zp Tline vs S-param equations**

| Term<br>Term3<br>Num=1<br>Z=50 Ohm<br>Subst="SSub<br>W=1.000 mil<br>L=1 mm |                                          | Term5<br>Num=4<br>Z=50 Ohm                                                                               |

|----------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------|

|                                                                            | · · · · · · · · · · <del>_</del> · · · · | $\simeq$ S2P19 $\simeq$ |

|                                                                            |                                          | S[1,1]=p0-p1*(1-exp(-j*2*3.142*f*t))                                                                     |

| SSub-                                                                      |                                          | S[1,2]=exp(y0+y1*sqrt(f)+y2*f+y4*pow(f,2))                                                               |

|                                                                            |                                          | S[2,1]=exp(y0+y1*sqrt(f)+y2*f+y4*pow(f,2))                                                               |

| SSUB                                                                       |                                          | S[2,2]=p0-p1*(1-exp(-j*2*3.142*f*t))                                                                     |

| SSub7                                                                      |                                          | Z[1]=                                                                                                    |

| Er=3.3                                                                     |                                          | · Z[2]=· · · · · · · · · · · · · · · · · · ·                                                             |

| Mur=1                                                                      |                                          |                                                                                                          |

| B=60.5 um                                                                  |                                          |                                                                                                          |

| <b>T=15 um</b> .                                                           |                                          | Ver VAR VAR                                                                                              |

| Cond=5.8e7                                                                 |                                          |                                                                                                          |

| Tan D=0.02                                                                 |                                          | p0=0.001 y0=-1.067*1e-3                                                                                  |

| Rough=                                                                     |                                          | p1=0.106 y1=complex(-3.551*1e-4,-3.357*1e-3)                                                             |

| Bbase=                                                                     |                                          | t=1.22e-2 y2=complex(-1.027*1e-3,-3.818*1e-2)                                                            |

| Dpeaks=                                                                    |                                          | y4=complex(-1:179*1e-5;3:36*1e-5)                                                                        |

| ······································                                     |                                          |                                                                                                          |

|                                                                            |                                          |                                                                                                          |

|                                                                            |                                          |                                                                                                          |

|                                                                            |                                          | VAR10                                                                                                    |

|                                                                            |                                          | rana ana ana ana ana ana ang f≂freq/1e9 ana ana ang                                                      |

#### **Comparing zp Tline vs S-param equations**

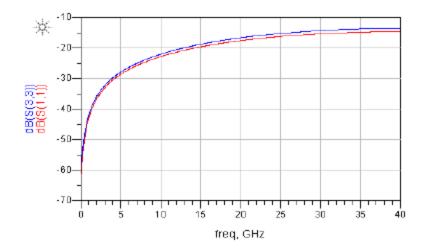

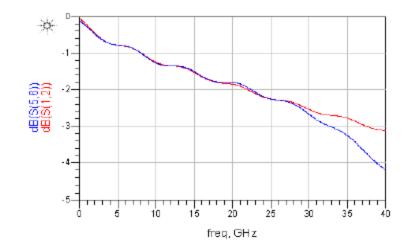

Insertion Loss L= 1mm Red – Tline Blue – S parameter equation

#### Comparing zp Tline vs S-param equations

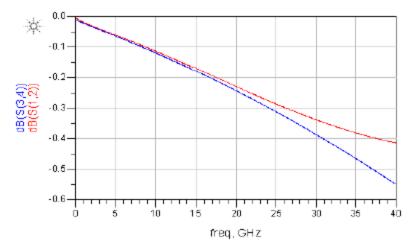

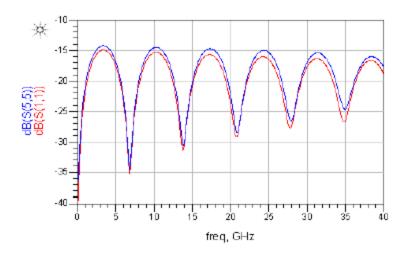

Return Loss L= 12mm Red – Tline Blue – S parameter equation Insertion Loss L= 12mm Red – Tline Blue – S parameter equation

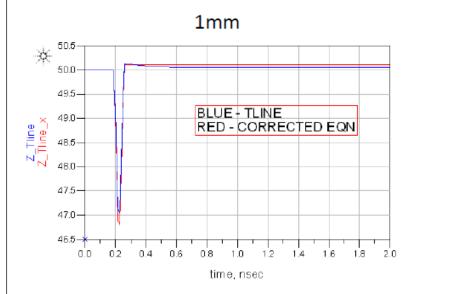

# **TDR Tline vs. S-param**

30ps rise time

time, nsec

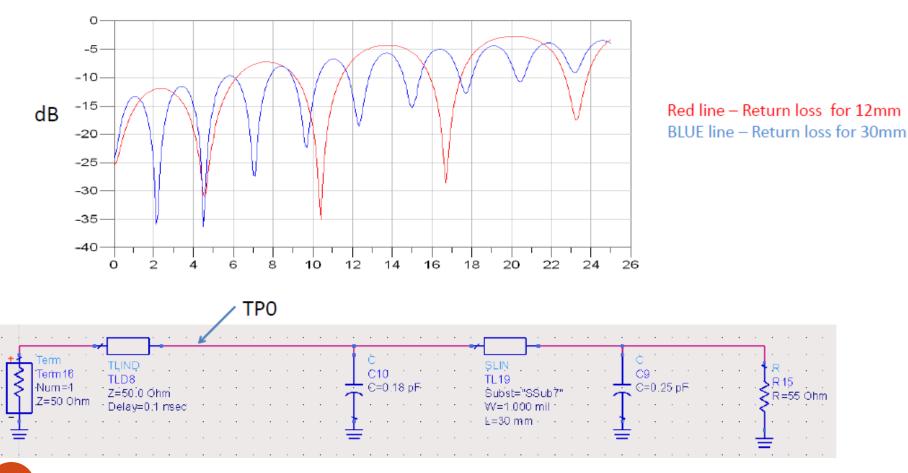

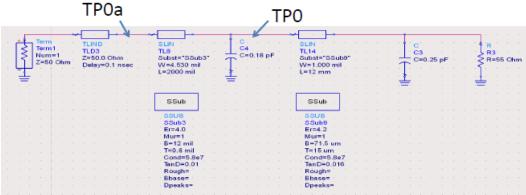

## S11 – TPO – Return loss

R=55.

Ohm

802.3bj March 2014 - Beijing

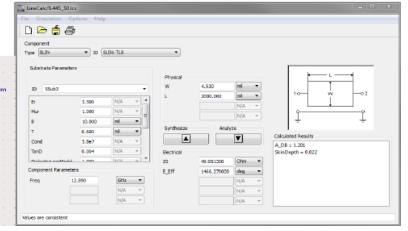

#### S11 – TPOa – Tline test fixture – 50ohms

Dpeaks-

Black line -

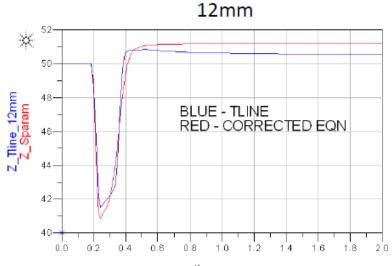

$$RL_d(f) \ge \left\{ \begin{array}{cc} 12.05 - f & 0.05 \le f \le 6 \\ 6.5 - 0.075 f & 6 < f \le 19 \end{array} \right\} dB$$

(93–3)

Red line – Return loss for 12mm BLUE line – Return loss for 30mm

#### 1.2dB loss at 12.89 Ghz for 2" Tline

Dpeaks-

#### S11 – TPOa – Tline test fixture – 550hms

Black line -

$$RL_d(f) \ge \begin{cases} 12.05 - f & 0.05 \le f \le 6\\ 6.5 - 0.075f & 6 < f \le 19 \end{cases} dB$$

(93-3)

Red line – Return loss for 12mm BLUE line – Return loss for 30mm

#### 1.2dB loss at 12.89 Ghz for 2" Tline

Models Used for simulation - Host Board - Method #3

- Host board model targeted at 3dB loss (@12.89GHz) from device pads to connector.

- Optimized vias were included at the device break-out and at the connector footprint.

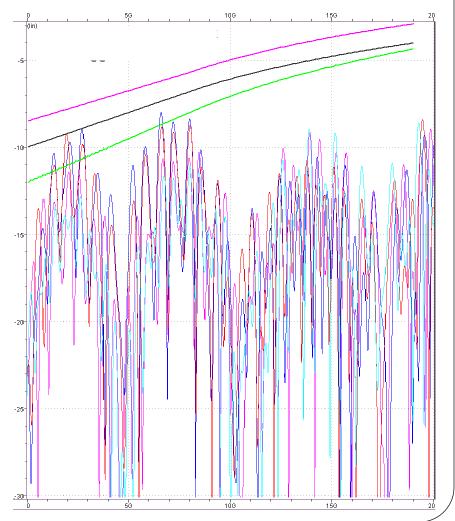

# Return loss @ TP2

- Return loss @ TP2 was simulated taking into account all cross impedance variance combinations.

- Some impedance combinations fail the draft 3.1 return loss spec.

- A new limit is suggested to accommodate these cases (black line):

- Return loss @ TP2 > 10 - 0.4\*f  $0.01 \le f \le 8$ 5-7.4\*LOG<sub>10</sub>(f/14)  $8 \le f \le 19$

# None Cross impedance Cases