## CAUI-4 Ad hoc

Ryan Latchman ryan.latchman@mindspeed.com

# Agenda

- Patent Policy: The meeting is an official IEEE ad hoc. Please review the patent policy at the following site prior to the meeting. http://www.ieee802.org/3/patent.html

- Adhoc objective: chip-chip baseline for March

- Chip to chip draft baseline

- Application space

- Channel

- Transmitter

- Receiver

- Areas of focus

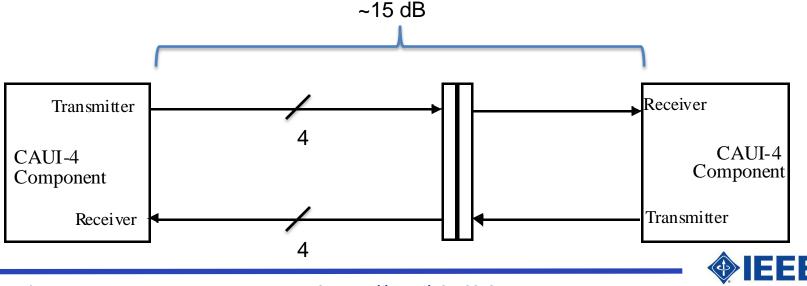

## Application

- Chip to chip interface

- Low power, low latency, AC coupled interface between ICs running at 4 x 25.78Gb/s

- No FEC, No-DFE/or limited DFE (e.g., 1-tap or analog), no transmitter training

- ~15 dB loss target with 1 connector (connector is optional)

- Consistent with 25cm reach target

- See <a href="http://www.ieee802.org/3/bm/public/nov12/palkert\_02\_1112\_optx.pdf">http://www.ieee802.org/3/bm/public/nov12/palkert\_02\_1112\_optx.pdf</a>, <a href="http://www.ieee802.org/3/bm/public/nov12/ghiasi\_03\_1112\_optx.pdf">http://www.ieee802.org/3/bm/public/nov12/ghiasi\_03\_1112\_optx.pdf</a>

- Higher loss channels also under analysis to enable longer links

## CAUI-4 chip to chip transmitter considerations

|                                                                 | KR4 (D1.4, TP0a)                                                                                                                                                                                                                                                                                   | MR                                                                                                             | CAUI-4 chip to chip Potential                                                                |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Signaling rate, per lane                                        | 25.78125+/-100ppm                                                                                                                                                                                                                                                                                  | 19.6 – 28.05                                                                                                   | 25.78125+/-100ppm                                                                            |

| Differential peak-to-peak output voltage (max) with Tx disabled | 30mV                                                                                                                                                                                                                                                                                               |                                                                                                                | 30mVppd                                                                                      |

| Common Mode Voltage (max)                                       | 1.9V                                                                                                                                                                                                                                                                                               | 1.7V                                                                                                           | 1.9V                                                                                         |

| Common Mode Voltage (min)                                       | 0V                                                                                                                                                                                                                                                                                                 | -0.1V                                                                                                          | 0V                                                                                           |

| Differential output return loss<br>(min)                        | RL(f) >=<br>12.05-f for 0.05<=f<=6 GHz<br>6.45 – 0.075f from 6 <f<=19 ghz<="" td=""><td>A0 = -12<br/>fo = 50MHz<br/>f1 = 4.4189<br/>f2 = 25.78125<br/>Slope = 12dB/dec</td><td>RL(f) &gt;=<br/>12.05-f for 0.05&lt;=f&lt;=6 GHz<br/>6.45 – 0.075f from 6<f<=19 ghz<="" td=""></f<=19></td></f<=19> | A0 = -12<br>fo = 50MHz<br>f1 = 4.4189<br>f2 = 25.78125<br>Slope = 12dB/dec                                     | RL(f) >=<br>12.05-f for 0.05<=f<=6 GHz<br>6.45 – 0.075f from 6 <f<=19 ghz<="" td=""></f<=19> |

| Common mode output<br>returnloss (min)                          | RL(f)>= 6dB, 0.05<=f<=19GHz                                                                                                                                                                                                                                                                        | 6dB , f<10GHz<br>4dB, 10G <f<25.78125ghz< td=""><td>RL(f)&gt;= 6dB, 0.05&lt;=f&lt;=19GHz</td></f<25.78125ghz<> | RL(f)>= 6dB, 0.05<=f<=19GHz                                                                  |

| Common-mode AC output<br>voltage (max,rms)                      | 12mV                                                                                                                                                                                                                                                                                               | 12mV                                                                                                           | 12mV                                                                                         |

| Amplitude peak-to-peak (max)                                    | 1200mV                                                                                                                                                                                                                                                                                             | 1200mV                                                                                                         | 1200mV                                                                                       |

| Transition Time (20%-80%, min, no EQ)                           | 8ps                                                                                                                                                                                                                                                                                                | 8ps                                                                                                            | 8ps                                                                                          |

| Max output Jitter                                               |                                                                                                                                                                                                                                                                                                    |                                                                                                                | See following slide                                                                          |

| Output eye mask                                                 |                                                                                                                                                                                                                                                                                                    |                                                                                                                | See following slide                                                                          |

| De-emphasis range                                               |                                                                                                                                                                                                                                                                                                    |                                                                                                                | See following slide                                                                          |

### CAUI-4 chip to chip transmitter leveraging: 802.3ba

- Define output jitter at TPOa

- Effective random jitter: 0.15Ulpp

- Even odd jitter: 0.035Ulpp

- Total jitter: 0.28Ulpp

- No (or default) de-emphasis

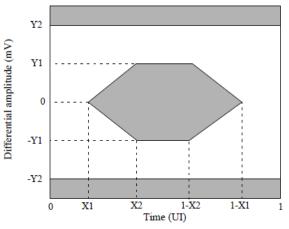

- Define X1, X2, Y1, Y2 (TBD right now)

- X1 = 0.14

- Y2 = 600mV

- X2/Y1 chosen to allow for rise/fall vs. swing trade off

- De-emphasis off

- De-emphasis range

- Minimum de-emphasis: TBD

- Maxim de-emphasis: TBD

- Minimum VMA: TBD

Figure 83A-8—Transmitter eye mask

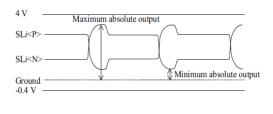

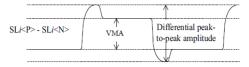

where

is the rise or fall time (whichever is larger) in ps

is de-emphasis value in dB

Figure 83A-5-Driver output voltage limits and definitions

### CAUI-4 chip to chip transmitter leveraging: 802.3bj

#### Table 93-4-Summary of transmitter characteristics at TP0a

| Parameter                                                                                                                                                                                                                        | Subclause<br>reference | Value                           | Units                |                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------|----------------------|------------------------------------------------------------------------------------------------------------|

| Signaling rate                                                                                                                                                                                                                   | 93.8.1.2               | 25.78125±100 ppm                | GBd                  |                                                                                                            |

| Differential peak-to-peak output voltage (max.)<br>Transmitter disabled <sup>a</sup><br>Transmitter enabled                                                                                                                      | 93.8.1.3               | 30<br>1200                      | mV<br>mV             | Table 93–5—Linear fit pulse and equalizer parameters        Description      Symbol      Value      Units  |

| DC common-mode output voltage (max.)                                                                                                                                                                                             | 93.8.1.3               | 1.9                             | v                    | Description      Symbol      Value      Units        Linear fit pulse length      N <sub>p</sub> 8      UI |

| DC common-mode output voltage (min.)                                                                                                                                                                                             | 93.8.1.3               | 0                               | v                    | Linear fit pulse delay $D_p$ 2 UI                                                                          |

| AC common-mode output voltage (RMS, max.)                                                                                                                                                                                        | 93.8.1.3               | 12                              | mV                   | Equalizer length N <sub>w</sub> 8 UI Remove                                                                |

| Differential output return loss (min.)                                                                                                                                                                                           | 93.8.1.4               | Equation (93-2)                 | dB                   | Equalizer delay $D_w$ 2 UI EQ                                                                              |

| Common-mode output return loss (min.)                                                                                                                                                                                            | 93.8.1.4               | Equation (93-3)                 | dB                   |                                                                                                            |

| Transition time (20-80%, min.), no equalization <sup>b</sup>                                                                                                                                                                     | 93.8.1.5               | 8                               | ps                   |                                                                                                            |

| Output waveform<br>Steady-state voltage v <sub>f</sub> (max.)<br>Steady-state voltage v <sub>f</sub> (min.)<br>Linear fit pulse peak (min.)<br>Normalized RMS linear fit error (max.)<br>Normalized coefficient step size (min.) | 93.8.1.6               | 0.6<br>0.4<br>0.8 × Vy<br>0.037 | v<br>v<br>v          |                                                                                                            |

| Normalized coefficient step size (max.)<br>Pre-cursor full-scale range (min.)<br>Post-cursor full-scale range (min.)                                                                                                             |                        | 0.05<br>1.54<br>4               | -                    | De-emphasis setting (s)                                                                                    |

| Far-end output noise (max.)<br>Low insertion loss channel<br>filigh insertion loss channel                                                                                                                                       | 93.8.1.7               | 2                               | mV<br>mV             | CAUI-4 chip –chip is relatively low loss                                                                   |

| Output jitter (max.)<br>Even-odd jitter<br>Effective deterministic jitter excluding data dependent jitter<br>Effective random jitter<br>Total jitter excluding data dependent jitter                                             | 93.8.1.8               | 0.035<br>0.15<br>0.15<br>0.28   | UI<br>UI<br>UI<br>UI |                                                                                                            |

## CAUI-4 chip to chip transmitter leveraging: OIF CEI SR

Table 10-6. Transmitter Electrical Output Specification.

| Characteristic                                                  | Symbol     | Condition                   | MIN.  | TYP. | MAX.  | UNIT   |

|-----------------------------------------------------------------|------------|-----------------------------|-------|------|-------|--------|

| Baud Rate                                                       | T_Baud     |                             | 19.90 |      | 28.05 | Gsym/s |

| Output Differential Voltage                                     | T_Vdiff    | Emphasis off.<br>See Note 4 | 800   |      | 1200  | mVppd  |

| Differential Resistance                                         | T_Rd       |                             | 80    | 100  | 120   | Ω      |

| Differential Termination Resistance<br>Mismatch (see Table 1-2) | T_Rdm      |                             |       |      | 10    | %      |

| Output Rise and Fall Time<br>(20% to 80%)                       | T_tr, T_tf | Emphasis off.<br>See Note 2 | 8     |      |       | ps     |

| Common Mode Noise                                               | T_Ncm      | Note 3                      |       |      | 12    | mVrms  |

| Differential Output Return Loss                                 | T_SDD22    | See Section 10.3.1.3        |       |      |       | dB     |

| Common Mode Output Return Loss                                  | T SCC22    | Below 10 GHz                |       |      | -6    | dB     |

| Common Mode Odlput Return Loss                                  | 1_50022    | 10 GHz to baud rate         |       |      | -4    | uв     |

| Output Common Mode Voltage                                      | T_Vcm      | Load Type 0<br>See Note 1   | -100  |      | 1700  | mV     |

#### Table 10-11. Transmitter output waveform requirements

| Parameter                                     | Condition | Units |                        |

|-----------------------------------------------|-----------|-------|------------------------|

| Steady state output voltage, $2 \times v_f$   | max       | mVppd | 1200                   |

| Steady state output voltage, $2 \times v_f$   | min       | mVppd | 800                    |

| Linear fit pulse peak, <i>p<sub>max</sub></i> | min       | -     | 0.80 x v <sub>f</sub>  |

| RMS error, $\sigma_e$                         | max       | -     | 0.027 x v <sub>f</sub> |

NOTES: 1. Load Type 0 with min. T\_Vdiff, AC-Coupling or floating load.

The transmitter under test is preset such that C0 is its maximum value (C0\_max) and all other coefficients are zero. The 20% and 80% values are of the steady state one and zero. The max value is limited by the linear fit pulse peak value in Table 10-11.

3. Measurement procedure is defined in Section 12.3.

4. T\_Vdiff is two times the steady-state value V<sub>f</sub> as defined in Section 10.3.1.6.2. The value is given as differential p-p voltage.

#### Table 10-7. Transmitter Output Jitter Specification

| Characteristic                               | Symbol  | Condition | MIN. | TYP. | MAX.  | UNIT             |

|----------------------------------------------|---------|-----------|------|------|-------|------------------|

| Uncorrelated Unbounded Gaussian Jitter       | T_UUGJ  |           |      |      | 0.15  | Ulpp             |

| Uncorrelated Bounded High Probability Jitter | T_UBHPJ | Note 2    |      |      | 0.15  | UI <sub>PP</sub> |

| Duty Cycle Distortion (component of UBHPJ)   | T_DCD   | Note 3    |      |      | 0.035 | Ulpp             |

| Total Jitter                                 | T_TJ    | Note 1    |      |      | 0.28  | Ulpp             |

| NOTES:                                       |         |           |      |      |       |                  |

1. T\_TJ includes all of the jitter components measured without any transmit equalization.

2. Measured with all possible values of transmitter equalization, excluding DDJ as defined in 12.1.1.

3. included in T\_UBHPJ

Link budgets in this document assume adaptive TX FIR equalization that is part of the system management function. The specific implementation is outside the scope of this document.

#### CAUI-4 ad hoc Feb 21, 2013

#### Table 10-10. Linear fit pulse and equalizing filter parameters

| Parameter                                      | Value (UI) |

|------------------------------------------------|------------|

| Linear fit pulse length <i>T_N<sub>p</sub></i> | 8          |

| Linear fit pulse delay <i>T_D<sub>p</sub></i>  | 2          |

| Equalizer length T_N <sub>w</sub>              | 8          |

| Equalizer delay <i>T_D<sub>w</sub></i>         | 2          |

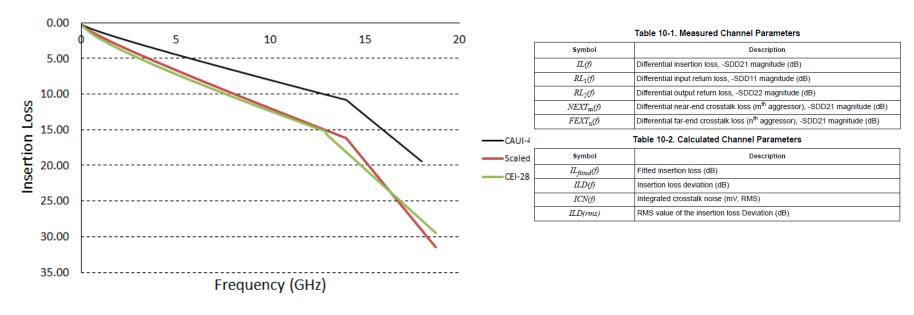

## CAUI-4 chip to chip channel leveraging: "Traditional" / OIF CEI SR

- Insertion Loss = 1.614 (0.075 + .537f^(0.5) + 0.566f)

1.614 (-18+2f)

- 0.01<=f<14 14<=f<18.75

- Return loss = TBD

- ILD = TBD

- ICN = TBD

- ILDrms = TBD

- Or insertion loss increase depending on simulation results with Mike's channel (<u>http://www.ieee802.org/3/bm/public/jan13/li\_01\_0113\_optx.pdf</u>)

CAUI-4 ad hoc Feb 21, 2013

### CAUI-4 chip to chip channel leveraging: 802.3bj

Table 93-9-Channel operating margin parameters

| Parameter                                                                                                               | Symbol                          | Value                                                  | Units          |                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signaling rate                                                                                                          | ſь                              | 25.78125                                               | GBd            | 1                                                                                                                                                                                                                             |

| Maximum start frequency                                                                                                 | $f_{\min}$                      | 0.05                                                   | GHz            | 93.9.1 Channel operating margin                                                                                                                                                                                               |

| Maximum frequency step                                                                                                  | 41                              | 0.01                                                   | GHz            | The channel operating margin (COM) computed using the procedure in Annex 93A and the parameters                                                                                                                               |

| Device package model<br>Single-ended device capacitance<br>Transmission line length<br>Single-ended package capacitance | $C_d$<br>$z_p$<br>$C_p$         | 2.5 × 10 <sup>-4</sup><br>12<br>1.8 × 10 <sup>-4</sup> | nF<br>mm<br>nF | Table 93-9 shall be greater than or equal to 34B. This minimum value allocates margin for practical limit tions on the receiver implementation as well as the largest step size allowed for transmitter equaliz coefficients. |

| Single-ended reference resistance                                                                                       | R <sub>0</sub>                  | 50                                                     | Ω              |                                                                                                                                                                                                                               |

| Single-ended termination resistance                                                                                     | R <sub>d</sub>                  | 55                                                     | Ω              | TBD                                                                                                                                                                                                                           |

| Transmitter differential peak output voltage<br>Victim<br>Far-end aggressor<br>Near-end aggressor                       | $A_{\nu}$<br>$A_{f}$<br>$A_{n}$ | 0.4<br>0.4<br>0.6                                      | v<br>v<br>v    |                                                                                                                                                                                                                               |

| Receiver 3 dB bandwidth                                                                                                 | $f_r$                           | 0.75 × <i>f</i> <sub>b</sub>                           | GHz            |                                                                                                                                                                                                                               |

| Transmitter equalizer, pre-cursor coefficient<br>Minimum value<br>Maximum value<br>Step size                            | c(-1)                           | -0.18<br>0<br>0.02                                     | =              | Modify to fixed setting                                                                                                                                                                                                       |

| Transmitter equalizer, post-cursor coefficient<br>Minimum value<br>Maximum value<br>Step size                           | c(1)                            | -0.38<br>0<br>0.02                                     | =              | Modify to fixed setting                                                                                                                                                                                                       |

| Continuous time filter, DC gain<br>Minimum value<br>Maximum value<br>Step size                                          | 8DC                             | -12<br>0<br>1                                          | dB<br>dB<br>dB | Increase the AC gain of CTLE?                                                                                                                                                                                                 |

| Number of signal levels                                                                                                 | L                               | 2                                                      | -              |                                                                                                                                                                                                                               |

| Number of samples per unit interval                                                                                     | М                               | 32                                                     | -              |                                                                                                                                                                                                                               |

| Decision feedback equalizer (DFE) length                                                                                | $N_b$                           | 14                                                     | UI             | Set to zero                                                                                                                                                                                                                   |

| Normalized DFE coefficient magnitude limit                                                                              | b <sub>max</sub>                | 1                                                      | -              | Remove                                                                                                                                                                                                                        |

| Random jitter, RMS                                                                                                      | σ <sub>RJ</sub>                 | 0.01                                                   | UI             |                                                                                                                                                                                                                               |

| Dual-Dirac jitter, peak                                                                                                 | ADD                             | 0.07                                                   | UI             | ]                                                                                                                                                                                                                             |

| Receiver additive Gaussian noise, RMS                                                                                   | σ,                              | 1                                                      | mV             | 1                                                                                                                                                                                                                             |

| Target detector error ratio                                                                                             | DER <sub>0</sub>                | 10 <sup>-5</sup>                                       | -              | 1e-12 (or 1e-15) - TBD                                                                                                                                                                                                        |

|                                                                                                                         |                                 |                                                        |                |                                                                                                                                                                                                                               |

CAUI-4 ad hoc Feb 21, 2013

EE

## CAUI-4 chip to chip receiver considerations

|                                              | KR4 (D1.4, TP5a)                                                                                                                                                                                                                                                                                   | MR                                                                         | CAUI-4 chip to chip Potential                                                                |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Differential Input Return loss (min)         | RL(f) >=<br>12.05-f for 0.05<=f<=6 GHz<br>6.45 – 0.075f from 6 <f<=19 ghz<="" td=""><td>A0 = -12<br/>fo = 50MHz<br/>f1 = 4.4189<br/>f2 = 25.78125<br/>Slope = 12dB/dec</td><td>RL(f) &gt;=<br/>12.05-f for 0.05&lt;=f&lt;=6 GHz<br/>6.45 – 0.075f from 6<f<=19 ghz<="" td=""></f<=19></td></f<=19> | A0 = -12<br>fo = 50MHz<br>f1 = 4.4189<br>f2 = 25.78125<br>Slope = 12dB/dec | RL(f) >=<br>12.05-f for 0.05<=f<=6 GHz<br>6.45 – 0.075f from 6 <f<=19 ghz<="" td=""></f<=19> |

| Differential to common mode input returnloss | RL(f) = 25-1.44f 0.05<=f<=6.95<br>15 6/95 <f<=19< td=""><td></td><td>RL(f) = 25-1.44f 0.05&lt;=f&lt;=6.95<br/>15 6/95<f<=19< td=""></f<=19<></td></f<=19<>                                                                                                                                         |                                                                            | RL(f) = 25-1.44f 0.05<=f<=6.95<br>15 6/95 <f<=19< td=""></f<=19<>                            |

| Interference Tolerance                       | Table 93-7                                                                                                                                                                                                                                                                                         |                                                                            | RL(f) >=<br>20-1.44*f for 0.01<=f<=6.95<br>15 from 6.95<=f<=13                               |

| Jitter tolerance                             | Table 93-8                                                                                                                                                                                                                                                                                         |                                                                            |                                                                                              |

| Input amplitude (max)                        |                                                                                                                                                                                                                                                                                                    | 1200                                                                       | TBD                                                                                          |

### Receiver Interference/Jitter Tolerance leveraging 802.3bj

| Parameter                                                        | Test values       |

|------------------------------------------------------------------|-------------------|

| Maximum BER*                                                     | 10 <sup>-12</sup> |

| Channel Insertion Loss<br>at 12.89GHz                            | ~15dB             |

| Applied peak-to-peak<br>sinusoidal jitter<br>(covering CDR JTOL) | TBD               |

| Applied peak-to-peak random jitter                               | TBD               |

| Applied even-odd jitter                                          | TBD               |

| Applied RMS<br>broadband noise                                   | TBD               |

\* Maximum BER assumes errors are not correlated to ensure a sufficiently high mean time to false packet acceptance (MTTFPA) assuming 64b/66b coding. Actual implementation of the receiver is beyond the scope of the standard.

### Receiver Interference/Jitter Tolerance leveraging OIF CEI SR

| Characteristic                 | Symbol  | Condition                 | MIN.  | TYP. | MAX.  | UNIT   |  |

|--------------------------------|---------|---------------------------|-------|------|-------|--------|--|

| Baud rate                      | R_Baud  |                           | 19.90 |      | 28.05 | GSym/s |  |

| Input Differential Voltage     | R_Vdiff | Note 1                    |       |      | 1200  | mVppd  |  |

| Differential Input Impedance   | R_Rdin  |                           | 80    | 100  | 120   | Ω      |  |

| Input Impedance Mismatch       | R_Rm    |                           |       |      | 10    | %      |  |

| Differential Input Return Loss | R_SDD11 | See 10.3.2.3              |       |      |       |        |  |

| Common Mode Input Return Loss  | R SCC11 | Below 10 GHz              |       |      | -6    | dB     |  |

|                                | K_SCOTI | 10GHz to baud rate        |       |      | -4    |        |  |

| Input Common Mode Voltage      | R_Vcm   | Load Type 0<br>See Note 2 | -200  |      | 1800  | mV     |  |

#### Table 10-12. Receiver Electrical Input Specifications

NOTES:

The receiver shall have a differential input voltage range sufficient to accept a signal produced at point R by the combined transmitter and channel. The channel response shall include the worst case effects of the return losses at the transmitter and receiver.

2. Load Type 0 with min. T\_Vdiff, AC-Coupling or floating load. For floating load, input resistance shall be  $\geq 1 k \Omega$

#### Table 10-13. Receiver Input Jitter Specification

| Characteristic                                                                                 | Symbol   | Condition                    | MIN. | TYP. | MAX. | UNIT   |

|------------------------------------------------------------------------------------------------|----------|------------------------------|------|------|------|--------|

| Sinusoidal Jitter, Maximum                                                                     | R_SJ-max | See Section<br>2.5.4, note 1 |      |      | 5    | Ulpp   |

| Sinusoidal Jitter, High Frequency                                                              | R_SJ-hf  | See Section<br>2.5.4, note 1 |      |      | 0.05 | Ulpp   |

| NOTES:<br>1. The Receiver shall tolerate the sum of<br>defined in Table 10-13;The effects of a |          |                              |      |      |      | ter as |

# Chip-module methodology

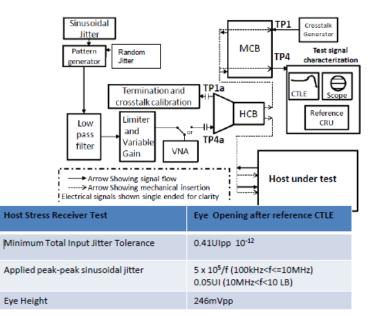

### Host Stress Receiver Test

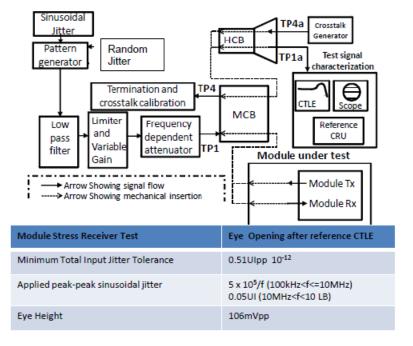

### Module Stress Receiver Test

# **Compliance** points

- See 93.8.2.1 Receiver test fixture from 802.3bj for TP5a

- See 93.8.1.1 Transmitter test fixture from 802.3bj for TP0a

# Straw Poll

- I prefer to specify the transmitter for CAUI chip-chip using the methodology described in

- A. 802.3ba CL 83A

- B. 802.3bj CL93 / OIF CEI 28G SR

- C. CAUI-4 chip-module (TP4)

- D. CAUI-4 chip-module (with software channel)

- I prefer to specify the channel for CAUI chip-chip using the methodology described in

- A. 802.3bj CL93 (COM)

- B. OIF CEI 28G SR

- I prefer to specify the receiver / tolerance for CAUI chip-chip using the methodology described in

- A. 802.3bj CL93

- B. OIF CEI 28G SR

- C. CAUI-4 chip-module

## Minutes

- Discussed IEEE patent policy

- Reviewed latchman 01 0213 caui

- Adhoc should ideally agree on methodology for baseline, but a baseline can still be put together without full agreement (leverage TBDs)

- Discussed chip-chip DC coupling

- Potentially two specs

- Concern with potential interoperability

- Transmitter methodology discussion

- VSR methodology discussed with software channel + CTLE -> look at eye diagram

- Actual far end channel measurements also discussed

- CAUI chip-chip specification ideally should allow designers to trade-off rise/fall, de-emphasis, swing

- 802.3bj CL93 methodology discussed

- Interest in leveraging chip-module methodology, or bj methodology (avoid creating new methodology)

- Can KR spec be a super set?

- Potential to relax amplitude, linear fit error

- Have fixed number of de-emphasis settings to keep solution space manageable (~2 settings), discussed post cursor only emphasis

- Channel methodology discussion

- OIF SR 28G method discussed

- COM method discussed, added reference to COM value with TBD (potentially use 3dB as a starting point)

- **Receiver methodology discussion**

- Discussed OIF and 802.3bj CL93 methodology

- Added chip-module methodology

- Preference to use simpler setup

- Next meeting: 28/02/2013 at 9:00am PT