# Cl 10x.t PHY-Link

# Baseline

Duane Remein (Huawei)

| 100. PMD for EPoC                              | 3 |

|------------------------------------------------|---|

| 100.2. PMD Functional Specifications           | 3 |

| '<br>100.2.8. PHY-Link                         |   |

| 100.2.8.1. PHY-Link resource allocation        |   |

| 100.2.9. PHY-Link DS Preamble                  |   |

|                                                |   |

| 101. RS, PCS, and PMA for EPoC                 |   |

| 101.5. PHY Link                                | 5 |

| 101.5.1. Overview                              | 5 |

| 101.5.2. PHY Link Frame structure and protocol | 5 |

| 101.5.2.1. DS Frame                            | 6 |

| 101.5.2.2. US Frame1                           | 0 |

| 101.5.3. PHY Discovery process1                | 2 |

# List of Tables

| Table 1. PHY-Link preamble for 4K FFT                              | 4  |

|--------------------------------------------------------------------|----|

| Table 2 PHY-Link preamble for 8K FFT                               |    |

| Table 3 PHY DA field values                                        | 7  |

| Table 4 PHY Config ID bits                                         | 8  |

| Table 5 Valid OPCODE command values                                | 8  |

| Table 6 OPCODE Acknowledgement values                              | 10 |

| Table 7 Required parameters for PHY Discovery Response and Link-Up | 13 |

## List of Figures

| Figure 1. PHY-Link spectrum placement        | 3  |

|----------------------------------------------|----|

| Figure 3 PHY Instruction response            | 6  |

| Figure 4 PHY-Link Timestamp reference point. | 7  |

| Figure 5 Config ID bit usage                 | 8  |

| Figure 6 PHY Discovery message exchange      | 14 |

# 100. PMD for EPoC

## 100.2. PMD Functional Specifications

Note: insert below 100.2.7 CLT Receive Requirements renumbering as subsequent sub-clauses

#### 100.2.8. PHY-Link

#### 100.2.8.1. PHY-Link resource allocation

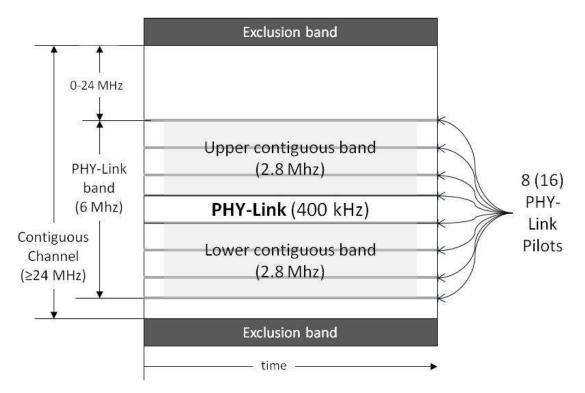

During network setup a specific amount of RF spectrum is allocated for use by the PHY Link in both the US and the DS directions. The allocated spectrum shall reside anywhere within a 24 MHz contiguous OFDM/OFDMA channel spectrum (i.e., 24 Mhz with no internal exclusion bands) and have at least 3 MHz of contiguous spectrum above and below it for a total band of 6 MHz, which includes eight pilot tone sub-carriers placed symmetrically above and below the information sub-carriers. Precise placement of these eight pilot tones is described in {ref}. No additional pilot tones area allowed within this 6 MHz band(see Figure 1).

In the DS direction the PHY Link shall be allocated 400 kHz of spectrum for information.

In the US direction the PHY Link shall be allocated *TBD* kHz of spectrum for information.

Figure 1. PHY-Link spectrum placement

#### 100.2.9. PHY-Link DS Preamble

The CLT shall modulate the subcarriers in the DS PLC preamble using binary phase-shift keying (BPSK), as shown in Table 1 or Table 2 depending on the FFT size and map each of the binary bits shown to a BPSK constellation point in the complex plane using the following transformation:

$0 \rightarrow (1 + j0)$  $1 \rightarrow (-1 + j0).$

| HY-Link preamble for 4K FFT  |

|------------------------------|

| PHY-Link preamble for 4K FFT |

|              | Symbol 1 | Symbol 2 | Symbol 3 | Symbol 4 | Symbol 5 | Symbol 6 | Symbol 7 | Symbol 8 |

|--------------|----------|----------|----------|----------|----------|----------|----------|----------|

| Subcarrier 1 | 0        | 0        | 1        | 0        | 1        | 1        | 0        | 1        |

| Subcarrier 2 | 1        | 0        | 0        | 0        | 1        | 1        | 1        | 0        |

| Subcarrier 3 | 0        | 1        | 1        | 1        | 1        | 0        | 0        | 1        |

| Subcarrier 4 | 0        | 1        | 0        | 0        | 0        | 1        | 1        | 0        |

| Subcarrier 5 | 1        | 1        | 1        | 0        | 1        | 1        | 1        | 1        |

| Subcarrier 6 | 1        | 0        | 0        | 0        | 0        | 0        | 0        | 1        |

| Subcarrier 7 | 0        | 1        | 0        | 1        | 0        | 0        | 1        | 1        |

| Subcarrier 8 | 0        | 0        | 1        | 0        | 0        | 0        | 1        | 1        |

#### Table 2 PHY-Link preamble for 8K FFT

|               | Symbol 1 | Symbol 2 | Symbol 3 | Symbol 4 | Symbol 5 | Symbol 6 | Symbol 7 | Symbol 8 |

|---------------|----------|----------|----------|----------|----------|----------|----------|----------|

| Subcarrier 1  | 1        | 0        | 0        | 1        | 0        | 1        | 0        | 0        |

| Subcarrier 2  | 0        | 1        | 1        | 0        | 0        | 1        | 0        | 0        |

| Subcarrier 3  | 0        | 1        | 1        | 1        | 0        | 0        | 0        | 1        |

| Subcarrier 4  | 0        | 0        | 0        | 1        | 0        | 1        | 1        | 1        |

| Subcarrier 5  | 1        | 1        | 0        | 0        | 1        | 0        | 1        | 0        |

| Subcarrier 6  | 0        | 0        | 0        | 1        | 1        | 0        | 0        | 1        |

| Subcarrier 7  | 0        | 1        | 1        | 1        | 0        | 1        | 1        | 0        |

| Subcarrier 8  | 1        | 1        | 1        | 0        | 0        | 0        | 1        | 0        |

| Subcarrier 9  | 0        | 1        | 1        | 1        | 1        | 0        | 0        | 1        |

| Subcarrier 10 | 1        | 1        | 1        | 1        | 0        | 1        | 1        | 1        |

| Subcarrier 11 | 1        | 1        | 1        | 0        | 0        | 0        | 0        | 0        |

| Subcarrier 12 | 1        | 1        | 0        | 1        | 0        | 1        | 0        | 1        |

| Subcarrier 13 | 1        | 1        | 0        | 0        | 1        | 1        | 0        | 0        |

| Subcarrier 14 | 1        | 0        | 1        | 1        | 1        | 0        | 1        | 0        |

| Subcarrier 15 | 0        | 1        | 0        | 1        | 1        | 0        | 0        | 0        |

| Subcarrier 16 | 0        | 0        | 1        | 0        | 0        | 0        | 0        | 1        |

# 101. RS, PCS, and PMA for EPoC

Note: insert below 101.4 EPoC\_PMD\_Name PMA renumbering subsequent sub-clauses

# 101.5. PHY Link

### 101.5.1. Overview

The PHY Link is a low level communications channel used between CLT PHY and its' subtended CNU PHYs. It is typically used to communicate PHY channel parameters and to negotiate initialization of CNUs that wish to join or rejoin the EPoC network. A small amount of RF spectrum is dedicated to the PHY Link at network setup time for both the US and the DS directions (see 100.2.1). The PHY link uses a simple query response protocol to transfer information in MDIO registers between the CLT and it's subtended CNUs and vice versa. The PHY Link uses a fixed frame format, that is, once it is set-up the PHY Link frame length does not change dynamically based on the data being carried. When operating in TDD mode the PHY Link frame shall be aligned with the TDD Frame. When operating in FDD mode the PHY Frame shall be aligned with the staggered pilot pattern as described in *{ref}*. Each frame is composed of a fixed header, one or more PHY Instructions or PHY Responses, padding and FEC parity.

## 101.5.2. PHY Link Frame structure and protocol

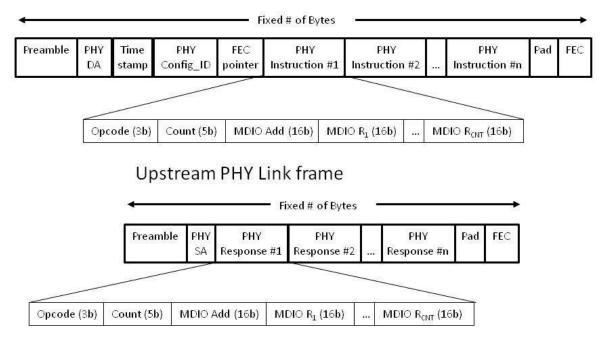

The PHY Link frame is composed of a fixed header, one or more PHY Instructions, padding, and FEC parity as illustrated in Figure 2.

# Downstream PHY Link frame

## Figure 2 PHY Link Frame

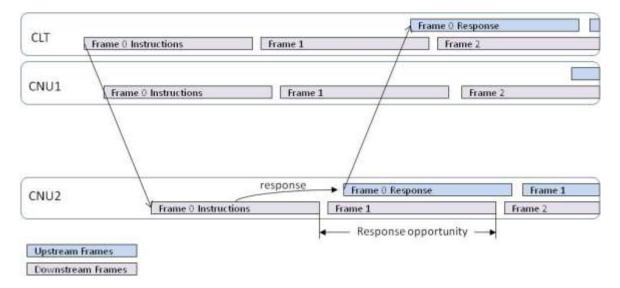

The PHY Link protocol is a query and response protocol where the CLT transmits one or more instructions to a CNU or group of CNUs. Each instruction can perform a read, write or write/verify

operation. PHY Instructions that require a response from the CNU (read & write/verify instructions) cannot be addressed to a group of CNU with the exception of a PHY Link Discovery (see below) Instruction. CNUs receiving PHY Instructions that require a response (read and write/verify operations) shall provide that response in the frame that starts following the end of the frame including the instruction (see Figure 3). When operating in FDD mode, the PHY Link frame shall be longer than the one way transit time, including all PHY delays, to the logically most distant CNU in the network.

EDITORS NOTE: if this frame length requirement is not met PHY Link frames cannot be aligned in a way allowing all CNUs to respond in the next US frame following the end of the DS frame including the instruction.

Figure 3 PHY Instruction response

#### 101.5.2.1. DS Frame

The downstream PHY Link frame is composed of a fixed header, one or more PHY Instructions and an FEC. The fixed header includes a preamble, the PHY DA, a *TBD(16-32)* bit Timestamp, the PHY Config ID, an FEC Pointer and a pad as illustrated in Figure 2. Each PHY Instruction is composed of an OPCODE, a Data Count, an MDIO Address, and 0 to 31 Data fields. The PHY Link frame is protected with an FEC mechanism. These fields are described below.

## 101.5.2.1.1. DS Fixed Header

The downstream Preamble is a fixed pattern of *TBD* bits that fill the first eight symbols of the PHY Link frame. The pattern is selected to enable the CNU to easily ascertain the PHY Link sub-carriers without prior knowledge of the PHY Link's precise location in the RF spectrum range of an EPoC network. Detection of the PHY Link is the first action a CNU must take to join an EPoC network.

EDITORS NOTE: insert additional preamble descriptive text on here based on Motion #10 Geneva July 2013, see montreuil\_3bn\_01\_0713.pdf slides 2, 3, 12, and 13. Leo is encouraged to provide this text.

The PHY Link DA is an address field that identifies the CNU the PHY frame is targeted for. This field is *TBD* {48, 11, 10} bits and may be a unicast address or a broadcast address. {*if we decide to use MAC Address for this field state so here, if not include and reference a table of Unicast/Broadcast values as illustrated below* }. In the CNU if the DA does not match the {*assigned / MAC*} address or the broadcast address then the frame is discarded and no response is made.

| Filed Value | Use                 |

|-------------|---------------------|

| 0x38 0x3F   | Broadcast addresses |

| 0x01 0x27   | Unicast addresses   |

| 0x00        | CLT PHY DA address  |

#### **Table 3 PHY DA field values**

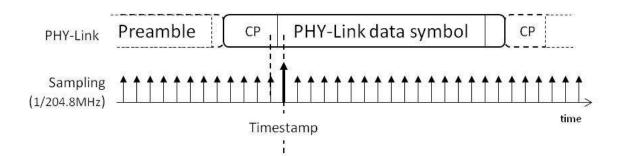

The PHY Timestamp is a TBD (16-32) bit field which the EPoC PHY uses to synchronize the US PHY Link frame and ODFMA symbols. The counter is clocked from the {204.8 MHz} OFDM clock. When the CNU PHY receives a PHY Frame addressed to it or to the broadcast address it shall reset it's local clock to the value in the Timestamp plus the value in it's Offset register (see *ref*). The reference point for the Timestamp shall be the first sample of the PHY-Link symbol immediately following the Preamble (see Figure 4). For additional information on the use of the Timestamp see {*ref*.}.

#### Figure 4 PHY-Link Timestamp reference point.

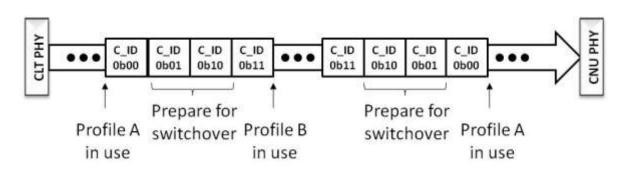

The PHY Config ID is a two bit field used to inform a CNU or group of CNUs to switch from one modulation profile to another. Each CNU contains two profiles, copy "A" and copy "B"; only one of which is active at any given time. The CLT updates the unused profile then, using the PHY Config ID bits, switches the CNU or a group of CNUs to the updated profile. Once the CLT begins the switchover, as indicated by PHY Config ID values 0b01 or 0b10 it shall complete the switchover. During a switchover the value of the PHY Config ID field is either incremented or decremented by one in each successive frame; thus a switchover takes three PHY Link frame times and the new profile is activated at the conclusion of the third frame. Table 4 summarizes the use and meaning of the PHY Config ID bits and their operation is illustrated in Figure 5.

#### Table 4 PHY Config ID bits

| PHY Co | nfigi ID | Mooning                |  |  |

|--------|----------|------------------------|--|--|

| bit 0  | bit 1    | Meaning                |  |  |

| 0      | 0        | Copy 0 in use          |  |  |

| 0      | 1        | proporo for quitchouor |  |  |

| 1      | 0        | prepare for switchover |  |  |

| 1      | 1        | Copy 3 in use          |  |  |

#### Figure 5 Config ID bit usage

EDITORS NOTE: see boyd\_3bn\_02a\_0313.pdf for slides originally describing the PHY Config ID bits.

The FEC Pointer is a 16 bit field used to identify the start of the first FEC codeword in the next PHY Link frame.

#### EDITORS NOTE: see boyd\_3bn\_02\_0513.pdf for slides originally describing the FEC Pointer.

The Pad field is used to fill the PHY frame in the event there are unused bits after the fixed overhead, PHY Instructions and FEC fields have been populated.

#### 101.5.2.1.2. DS PHY Instructions

The CLT can perform read and write operations on the MDIO register space of subtended CNUs via PHY Instructions. Each instruction contains an OPCODE, a Count, an MDIO Address and up to 31 Data fields.

The PHY Link OPCODE is a 3 bit field that conveys the operation of the PHY Instruction in which it resides. The CLT shall only transmit the valid values of the command sub-field as given in Table 5.

| Value | Operation | Description                                                                                                                                  |

|-------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 0b000 | NOP       | no operation, the CNU acknowledges this instruction only                                                                                     |

| 0b001 | read      | The CNU responds with the contents of MDIO registers starting at the address specified by the MDIO Address field and subsequent registers as |

|       |           | specified by the Data Count field                                                                                                            |

#### Table 5 Valid OPCODE command values

| 0b010 | write        | the CNU stores the values given in the data field starting at the register given in the MDIO Address field and subsequent register as specified by the Data Count field |

|-------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0b011 | write/verify | the CNU first writes the MDIO registers as specified by MDIO Address and<br>Data Count field and then responds with the values contained in those<br>same registers     |

| 0b1xx | reserved     | no operation, the CNU ignores these instructions                                                                                                                        |

The Count field specifies the number of 16 bit data words contained in a write or write/verify PHY Instruction or the number of 16 bit MDIO registers that are to be returned in a read or write/verify PHY Instruction. The Data Count field has a value of 0 to 31. The Count field in a NOP instruction always has a value of 0. Whereas, for a read, write or write/verify instruction the Count always has a value between 1 and 31.

The 16 bit MDIO Address field specifies the MDIO register address at which the CNU is to begin the read, write or write/verify operation. The NOP instruction does not include an Address field.

The 16 bit Data fields contain the data values to be written in or read from consecutive MDIO registers starting with the register indicated by the MDIO Address field and continuing for the number of registers indicated by Data Count of the target CNU. The Data fields are valid only for a write or write/verify PHY Instructions; or in the response to a read or write/verify PHY Instruction. In the event there is a discrepancy between the Count field and the number of 16 bit Data fields the CNU shall write no data to it's MDIO register and returns a Nack indication (see Table 6 OPCODE Acknowledgement values).

## 101.5.2.1.3. DS PHY Discovery window

The CLT opens a PHY Discovery window by sending a specific sequence of broadcast instructions addressed to the broadcast DA in a single PHY frame. This sequence includes:

- Write Discovery Preamble

- Read CNU MAC address

- Write/Verify Discovery Window duration

# EDITORS NOTE: at this point the above list is mearly a suggestion by the author to be included in the draft, additional suggestions are solicited from the TF

Once the PHY Discovery window is open the CLT *shall* refrain from sending PHY Instructions to any single CNU over the DS PHY Link, which would elicit a Response from the CNU, to allow sufficient time for joining CNUs to respond to the PHY Discovery window. The exact time period depends on the length of the PHY Discovery window but shall be greater than the maximum one way travel time for the EPoC network.

## 101.5.2.1.4. DS PHY Link FEC

The downstream PHY Link uses a (384,288) binary punctured LDPC code.

EDITORS NOTE: see shen\_3bn\_01\_0713.pdf for original slides describing DS PHY Link FEC. FEC experts, such as BZ Shen, are requested to submit an adequate description of this FEC.

#### 101.5.2.2. US Frame

The upstream PHY Link frame is composed of a fixed header, one or more PHY Responses and an FEC. The fixed header includes a preamble, the PHY SA, and a pad. Each PHY Response is composed of an OPCODE, a Data Count, an MDIO Address, and 0 to 31 Data fields. The PHY Link frame is protected with an FEC mechanism. These fields are described below.

### 101.5.2.2.1. US Fixed Header

The upstream Preamble is a fixed pattern of *TBD* bits that fills the first symbol of the PHY Link frame. The pattern is selected to enable the CLT to easily detect the CNU PHY Link transmission.

#### EDITORS NOTE: insert additional descriptive text here based on final agreed US PHY Link Preamble.

The PHY SA is an address field that identifies the CNU the PHY frame is transmitted from. This field is *TBD (48, 11,10)* bits and is always the unicast address associated with the CNU transmitting in the PHY Link. *{if we decide to use MAC Address for this field state so here, if not refer to table above}.*

The Pad field is used to fill the PHY frame in the event there are unused bits after the fixed overhead, PHY Response and FEC fields have been populated.

### 101.5.2.2.2. US PHY Response

The CNU must respond to PHY Link read and write/verify instructions using the PHY Response. Each Response contains an OPCODE, an MDIO Address and up to 31 data fields.

The PHY Response OPCODE is an 8 bit field separated into two sub-fields; the Acknowledgement sub-field and the Data Count sub-field. The Acknowledgement sub-field is a 3 bit value that conveys the type of PHY Instruction to which the CNU is responding and the success or failure of the PHY Instruction Command. CNUs shall use the valid values of the Acknowledgement sub-field are given in Table 6.

#### Table 6 OPCODE Acknowledgement values

| Value | Operation        | Description                                                         |

|-------|------------------|---------------------------------------------------------------------|

| 0b000 | NOP Ack          | NOP Instruction acknowledge returned in response to a successfully  |

|       |                  | received NOP Instruction                                            |

| 0b001 | read Ack         | read Instruction acknowledge returned in response to a successfully |

|       |                  | received and executed read Instruction along with the requested     |

|       |                  | MDIO registers as specified in the MDIO Address and Data Count      |

|       |                  | fields of the PHY Instruction                                       |

| 0b010 | write Ack        | write Instruction acknowledge returned in response to a             |

|       |                  | successfully received and executed write Instruction                |

| 0b011 | write/verify Ack | write/verify Instruction acknowledge returned in response to a      |

|       |                  | successfully received and executed write/verify Instruction along   |

|       |                  | with the requested MDIO registers as specified in the MDIO          |

|       |                  | Address and Data Count fields of the PHY Instruction                |

| 0b100 | NOP Nack          | NOP Instruction negative acknowledge returned in response to a unsuccessfully received NOP Instruction { <i>might just want to keep this as a reserved value</i> } |

|-------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0b101 | read Nack         | read Instruction negative acknowledge returned in response to an                                                                                                   |

|       |                   | unsuccessfully received or executed read Instruction                                                                                                               |

| 0b110 | write Nack        | write Instruction negative acknowledge returned in response to an                                                                                                  |

|       |                   | unsuccessfully received or executed write Instruction                                                                                                              |

| 0b111 | write/verify Nack | write/verify Instruction negative acknowledge returned in response                                                                                                 |

|       |                   | to an un successfully received or executed write/verify Instruction                                                                                                |

The Data Count field specifies the number of 16 bit MDIO registers that are being returned in response to a read or write/verify PHY Instruction. In the event the CNU is returning a Nack response (Acknowledgement values 0b100 through 0b0111) the Data Count field should {shall?} be set to zero and is ignored at the CLT.

The 16 bit MDIO Address field specifies the first register address for which the CNU is returning data due to a read or write/verify operation or the first register address of the corresponding write Instruction.

The 16 bit Data fields contain the data values read from the MDIO registers due to a read or write/verify PHY Instruction. In the event the CNU is responding to a write instruction this field is omitted. The Data field should {shall?} be omitted in Nack Responses (Acknowledgement values 0b100 to 0v111) and, if included, shall be ignored at the CLT.

#### 101.5.2.2.3. US PHY Discovery Response

The CNU Discovery Response is only allowed after a CNU has completed the Discovery prerequisites (see *ref*.). In the Discovery Response message:

- the preamble used is the special PHY Discovery Preamble {ref CL 45 registers}

- the SA field is set to 0x00 {*if we decide to use the MAC address instead of an ONU ID can set this to MAC address*}

- the a TDB {16-32} bit local clock of the CNU

- the CNU MAC address is carried in the MDIO Data fields.{*assumes using CNU\_ID, if not combine 2<sup>nd</sup> &4<sup>thd</sup> bullets to read "the SA field is set to the CNUs MAC address*}

{Optional description and list of parameters in Discovery Response, in actuality the required response is determined by the PHY Discovery Window, again input is solicited on the precise definition for this message}

101.5.2.2.4. US PHY Link FEC **TDB**

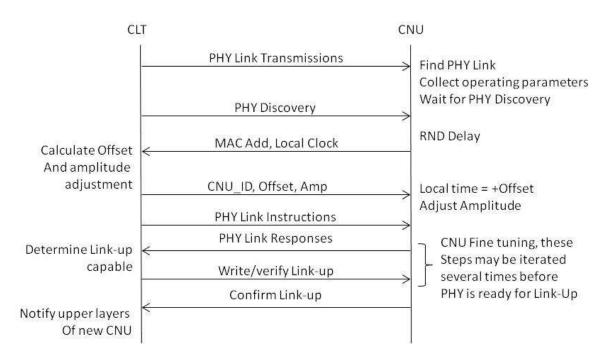

#### 101.5.3. PHY Discovery process

When a CNU first joins the EPoC network it has no prior knowledge of the upstream OFDMA frame and timing necessary to produce transmissions that are orthogonal to the rest of the EPoC network when viewed from the perspective of the CLT receiver. PHY Discovery is the process whereby newly connected or off-line CNUs are provided timing and operating parameters necessary to function properly in the EPoC network.

When a CNU joins an EPoC network it must first locate the downstream PHY Link. This is typically done via a vendor specific correlation algorithm. Prior to any transmission in an EPoC network the CNU shall locate the downstream PHY Link, gather the required Discovery operating parameters listed in Table 7 and synchronize it's local clock to the downstream OFDM clock. Once the CNU has completed the prerequisites for transmission it waits for the CLT to issue a PHY Discovery window.

# EDITORS NOTE: the TF needs to determine precisely how accurately the CNU must be synchronized to the OFDM clock before US transmission is allowed.

The CLT periodically makes available PHY Discovery Windows during which off-line CNUs are given the opportunity to make themselves known to the CLT. The periodicity of these windows is unspecified and left up to the implementer. The CLT signifies that a PHY Discovery period is occurring by broadcasting a PHY Discovery Instruction, which includes the length of the PHY Discovery window *{optionally list other elements of this instruction}* as defined in *{ref}*.

Off-line CNUs, upon receiving a PHY Discovery Instruction, wait for the beginning of the next upstream frame and then transmit a PHY Discovery Response to the CLT. PHY Discovery windows are unique in that they are the only times when multiple CNUs can access the CDN using the same RF spectrum simultaneously, and transmission overlap can occur in both time and frequency. *In order to reduce transmission overlaps, a contention algorithm is used by all off-line CNUs. Measures are taken to reduce the probability for overlaps by artificially simulating a random distribution of distances from the CLT. Each CNU waits a random amount of time before transmitting the PHY Discovery Response that is shorter than the length of the discovery window. It should be noted that multiple valid PHY Discovery Responses can be received by the CLT during a single discovery window.* Included in the PHY Discovery Response is the CNU's MAC address and {*list of other parameters*}.

EDITORS NOTE: the above statements regarding multiple responses to a PHY Discovery window may or may not be true depending on the size of the window and collision mitigation method finally selected by the TF.

#### EDITORS NOTE: the following text is in Cl 102.3.3 but may be more appropriate here.

In order to assure maximum utilization of the upstream channel and to decrease the required size of the guard band between individual data bursts, the registering CNU notifies the CLT of the RF on/off times, by setting appropriate values in the RF On Time and RF Off Time fields, where both values are expressed in the units of time\_quanta.

# EDITORS NOTE: the following text is written assuming we adopt the CNU\_ID concept, if this is not the case the Editor should remove references to CNU\_ID.

Upon receipt of a valid PHY Discovery Response, the CLT updates the CNU by allocating and assigning a new port identity (CNU\_ID). The CLT calculates an OFDMA Timing Offset and adjusts the CNU's amplitude. The CLT also sets the target value of RF on time and RF off time, which may be different than RF on time and RF off time delivered by the CNU in the PHY Discovery Response. These parameters are transmitted to the CNU via the appropriate PHY Instructions.

The next step in the process is for the CLT to perform an upstream channel estimate of the newly discovered CNU using probing or fine ranging as described in *{ref}*. The CLT may further adjust the US amplitude and timing of the CNU as needed. The CLT also ascertains the CNUs capabilities via the appropriate read instructions. Before declaring a CNU is in the link-up state the CLT must ensure that a CNU joining the EPoC network is properly aligned to the US OFDMA timing and is cognizant of all necessary provisioning parameters needed to properly operate in the OFDMA network without adverse impact to the EPoC network or other services operating in RF spectrum unused by the EPoC network. A list of required parameters is given in Table 7.

Once the CLT has enough information to declare the CNU has attained a link-up status. The CNU first informs the CNU and verifies the CNU has transitioned to link-up status. After verifying the CNUs link-up status the CLT informs the upper layers that a new CNU has joined the EPoC network and is ready to be registered by the MAC Control layer. The PHY Discovery message exchange is illustrated in Figure 6.

There may exist situations when the CLT requires that a CNU go through the PHY Discovery sequence again. Similarly, there may be situations where a CNU needs to inform the CLT of its desire to leave the EPoC network. The CNU can then go through the PHY Discovery sequence again.

| Parameter                | MDIO | Required for |                        |

|--------------------------|------|--------------|------------------------|

|                          | Reg. | РНҮ          | Link-Up <sub>(1)</sub> |

|                          |      | Discovery    | ,                      |

| DS OFDM Descriptor       | TBD  |              | Y                      |

| DS PHY Link Descriptor   | TBD  | Y            |                        |

| DS Preamble              | TBD  | Y            |                        |

| DS Profile               | TBD  |              | Y                      |

| DS RF Channel Descriptor | TBD  |              | Y                      |

| TDD/FDD Mode             | TBD  | Y            |                        |

| US OFDMA Descriptor      | TBD  |              | Y                      |

| US PHY Link Descriptor   | TBD  | Y            |                        |

| US Preamble              | TBD  | Y            |                        |

| US Profile               | TBD  |              | Y                      |

| US RF Channel Descriptor | TBD  |              | Y                      |

#### Table 7 Required parameters for PHY Discovery Response and Link-Up

Notes:

1) Parameters required for Discovery are also required for Link-Up.

EDITORS NOTE: The above table is an example only, this will need to be rationalized and cross referenced with CL 45 MDIO Registers at some point. Depending on how detailed we need to get this table may be fairly large. A short description of each entry of the above table follows: OFDM Descriptor – FFT size, CP size, windowing, time/freq interleaving, pilots, etc. PHY Link Descriptor – PHY-Link center Frequency Preamble – bit patter of PHY Link preamble if not fixed in STD Profile – Bit loading, RF Channel Descriptor – center frequency, exclusion bands, TDD/FDD Mode

#### Figure 6 PHY Discovery message exchange

{ Fine ranging to be described elsewhere as this is also a part of ongoing channel maintenance}