# PHY High Level Block Diagrams – R02 16 October 2013

Avi Kliger, Mark Laubach Broadcom

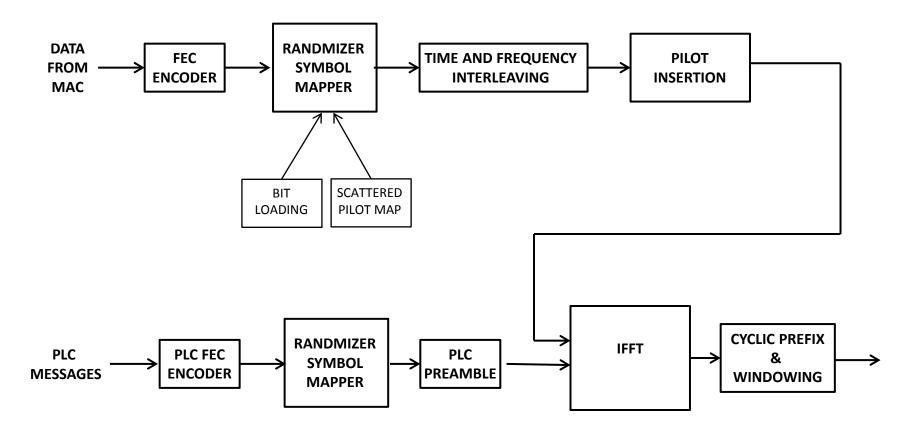

#### Previous (old original):

**EPoC Downstream Transmitter Block Diagram (starting point)**

NOTE: All digital domain

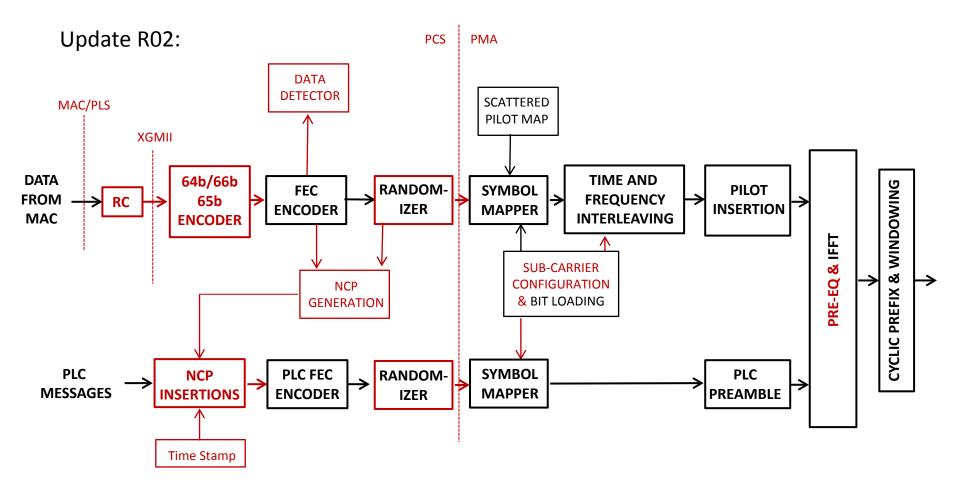

### **EPoC Downstream CLT Transmitter Block Diagram**

**NOTE: All digital domain**

NOTE: Sub-Carrier Configuration includes sub-carrier use and QAM mapping

**NOTE: Not converted yet to IEEE 802 Vertical Form**

Assumption: Upstream PLC will be similar to downstream, with added functionality to control bursts separate from data

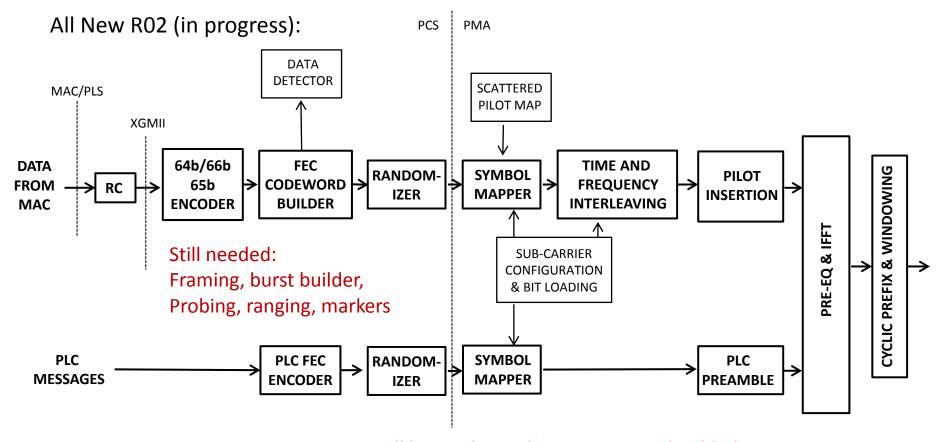

#### **EPoC Upstream CNU Transmitter Block Diagram**

**NOTE: All digital domain**

NOTE: Sub-Carrier Configuration includes sub-carrier use and QAM mapping

**NOTE: Not converted yet to IEEE 802 Vertical Form**

## Summary

- Downstream CLT Transmitter near complete

- Upstream CNU Transmitter

- Work in progress

- Needed: PHY path block delays

- Work in progress

### **THANK YOU**