# IEEE P802.3bs Baseline Summary

John D'Ambrosia, Dell Chair, IEEE P802.3bs 400 GbE Task Force

> July 11, 2015 (Post May, 2015 Summary)

| Topic Matter                        | Motion                                                                                                                                                                                                                           | Reference Presentation                                                  |  |  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|

| Architecture                        | Motion #3, Jan 15: Move to adopt slides 4 and 8 from dambrosia_3bs_02b_0115 as baseline architecture.                                                                                                                            | http://www.ieee802.org/3/bs/public/15_01/dambr<br>osia_3bs_02b_0115.pdf |  |  |

| RS / CDMII                          | Motion #3, July 14: Move to adopt the baseline for the CDMII logical interface as shown in slide 5 of gustlin_3bs_03_0714.pdf.                                                                                                   | http://www.ieee802.org/3/bs/public/14_07/gustlin_3bs_03_0714.pdf        |  |  |

| FEC                                 | Motion #3, Mar 15: Move to adopt RS(544,514,10) as the FEC in the 802.3bs 400GbE architecture                                                                                                                                    |                                                                         |  |  |

| Electrical Interfaces (C2C and C2M) | Motion #4, Sept 14: Move to adopt 16 x 25Gb/s and 8 x 50Gb/s as the basis for the lane rates for any optional C2C and C2M electrical interfaces                                                                                  |                                                                         |  |  |

| C2C / C2M 25G Electrical            | Motion #6, Sept 14: Move to adopt the P802.3bm C2C and C2M specifications with current values (except that the BER requirement is TBD) as a baseline draft for the 16 x 25Gb/s electrical interfaces                             |                                                                         |  |  |

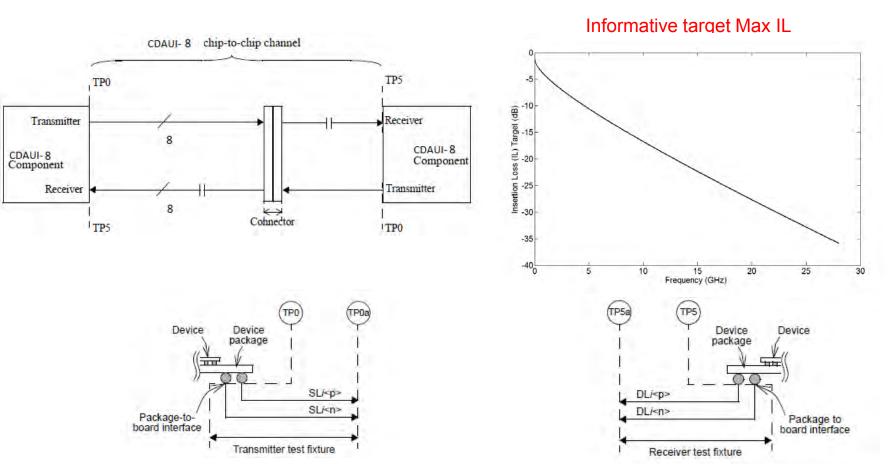

| C2C 50G Electrical                  | Motion #4, Mar 15: Move to adopt li_3bs_01a_0315.pdf as the baseline proposal for CDAUI-8 chip-to-chip electrical I/O interface except for the differential return losses (on slide 11) for the TX and the RX shall be TBD.      | http://www.ieee802.org/3/bs/public/15 03/li 3bs<br>01a 0315.pdf         |  |  |

| C2M 50G Electrical                  | Motion #5, Mar 15:Move to adopt brown_3bs_01a_0315.pdf     as the baseline proposal for CDAUI-8 chip-to-module     electrical I/O interface.                                                                                     | http://www.ieee802.org/3/bs/public/15 03/brown<br>3bs 01a 0315.pdf      |  |  |

| C2C Informative Channel             | Motion #6, Jan 15: Move to adopt the following equation as the informative insertion loss equation for CDAUI-8 chip-to-chip electrical I/O interface  IL <= { 1.083 + 2.543SQROOT(f) + 0.761f                                    |                                                                         |  |  |

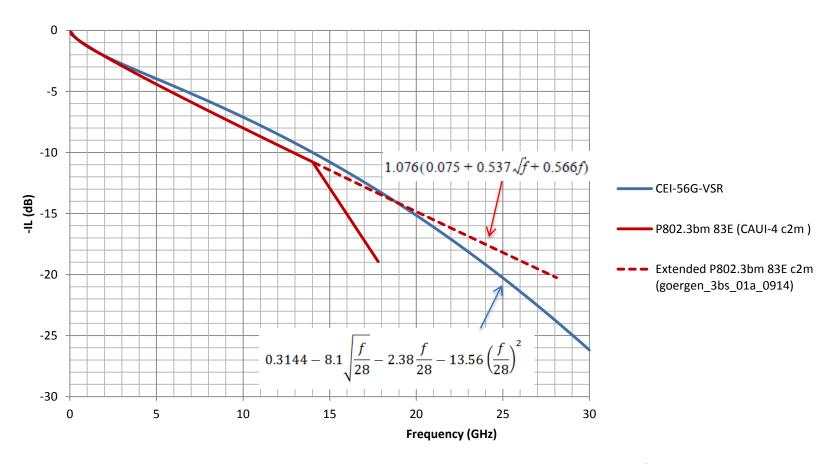

| C2M Informative Channel             | Motion #8, Jan 15: Move to adopt the following equation as the informative insertion loss equation for CDAUI-8 chip-to-module electrical I/O interface  IL <= { 1.076(0.075 + 0.537SQROOT(f) + 0.566f) 0.01 <= f <= 28.05GHz} dB |                                                                         |  |  |

|          | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| EEE      | Motion #4, Jan 15: Move to adopt the EEE baseline proposed in marris_3bs_01_0115.pdf slide 7.                                                                                                                                                                                                                                                                                                                                                                                           | http://www.ieee802.org/3/bs/public/15_01/marris_3bs_01_0115.pdf      |

| OTN      | Motion #5, Jan 15: Move to adopt slide 10 of<br>trowbridge_3bs_01a_0115.pdf as the baseline for the OTN<br>mapping reference point                                                                                                                                                                                                                                                                                                                                                      | http://www.ieee802.org/3/bs/public/15_01/trowbridge_3bs_01a_0115.pdf |

| 100m MMF | Motion #3, Nov 14: Move to adopt the proposal in slides 6 to<br>16 in king_3bs_02a_1114.pdf as the baseline proposal for<br>the P802.3bs objective to "provide physical layer<br>specifications which support link distances of at least 100 m of<br>MMF" (400GBASE-SR16)*                                                                                                                                                                                                              | http://www.ieee802.org/3/bs/public/14_11/king_<br>3bs_02a_1114.pdf   |

| 500m SMF | Motion #12, May 15: Move to adopt 4x100G PAM4 PSM4 as<br>the modulation format for the 500m SMF (single mode fiber)<br>PMD objective                                                                                                                                                                                                                                                                                                                                                    |                                                                      |

| 10km SMF | <ul> <li>Motion #4, July 14: Move that 10km 400GbE SMF PMD will use a duplex fiber solution.</li> <li>Motion #6, May 15: Move to adopt 8 lambda x 50 Gb/s as the basis for the 10 km SMF PMD objective</li> <li>Motion #9, May 15: Move to adopt 8x50G PAM4 as the modulation format for the 10km SMF (single mode fiber) PMD objective</li> <li>Motion #11, May 15: Move to adopt a baseline for the 10km SMF PMD objective based on the 10km proposal in cole_3bs_01a_0515</li> </ul> | http://www.ieee802.org/3/bs/public/15_0<br>5/cole_3bs_01a_0515.pdf   |

# 400GbE Architecture Baseline Proposal (Update)

#### IEEE P802.3bs 400 Gb/s Ethernet Task Force

January 2015

Pete Anslow - Ciena

John D'Ambrosia – Dell

Mark Gustlin – Xilinx

Adam Healey – Avago

David Law – HP

Gary Nicholl - Cisco

Dave Ofelt – Juniper

Steve Trowbridge - ALU

# What Needs to be Supported in the Architecture?

- The coding needs of the electrical interface may vary independently from the PMD interface

- ➤ The requirements for each interface can be different, both the FEC, modulation and number of lanes can change over time for each interface

- ➤ We need a single high level architecture which can support the evolving requirements of the interfaces over time

- This does not mean it requires a complicated implementation

- ➤ A Media Independent interface needs to be specified to enable standardization of different PHYs today and future, "unknown", PHYs tomorrow.

- We need an electrical interface between different devices, CDAUI (C2C & C2M)

- ▶ IEEE 802.3 supports two "levels" of implementers

- The system implementer

- The component implementer

### Sublayer Functions (at a high level)

| Sublayer | 10GbE                                                  | 100GbE                                   | 400GbE (proposed)                      |

|----------|--------------------------------------------------------|------------------------------------------|----------------------------------------|

| MAC      | Framing, addressing, error detection                   | Framing, addressing, error detection     | Framing, addressing, error detection   |

| Extender | XGXS (PCS + PMA function)                              | N/A                                      | CDXS (PCS + FEC function)              |

| PCS      | Coding (X: 8B/10B, R: 64B/66B), lane distribution, EEE | Coding (64B/66B), lane distribution, EEE | Coding, lane distribution, EEE, FEC    |

| FEC      | FEC, transcoding                                       | FEC, transcoding, align and deskew       | N/A                                    |

| PMA      | Serialization, clock and data recovery                 | Muxing, clock and data recovery, HOM     | Muxing, clock and data recovery, HOM?? |

| PMD      | Physical interface driver                              | Physical interface driver                | Physical interface driver              |

Note that there are variations with a single speed, not all are captured in this table

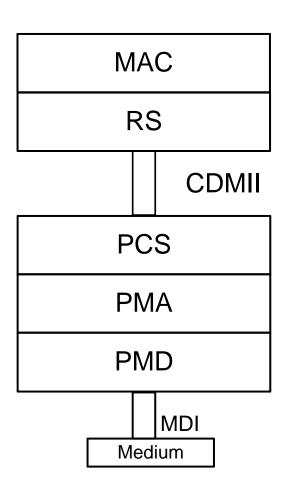

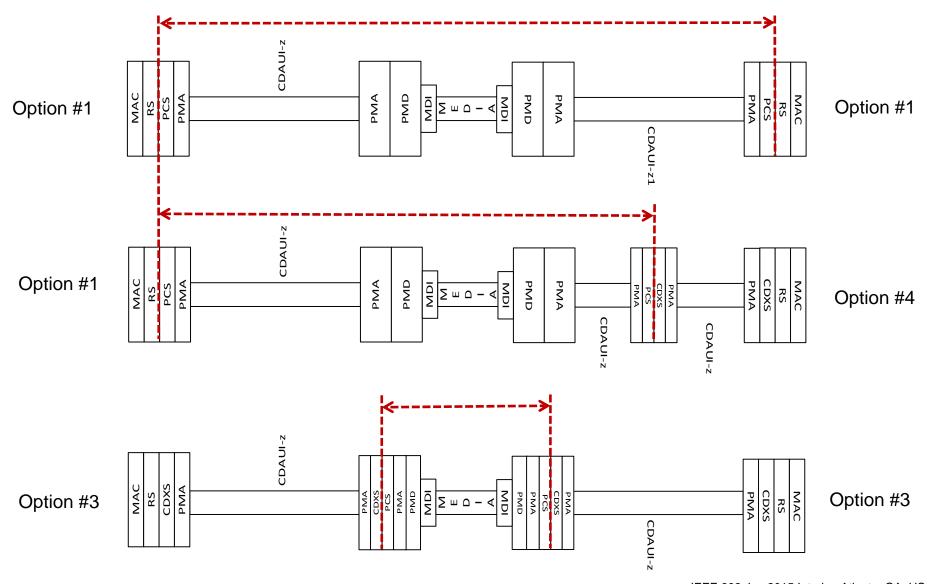

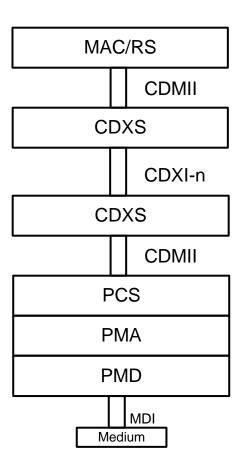

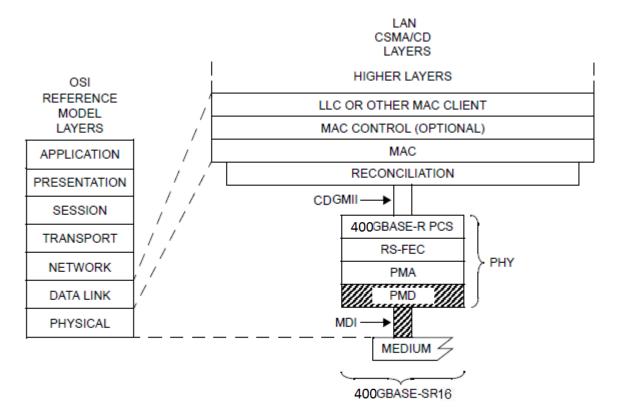

#### The 400GbE Basic Layer Diagram

#### But...

- To enable flexibility for future efforts, an extender sublayer for the CDMII is desirable, but there is no physical instantiation of the CDMII.

- From a standardization perspective, it can leverage a CDAUI, which is a optional physical instantiation of the PMA service interface

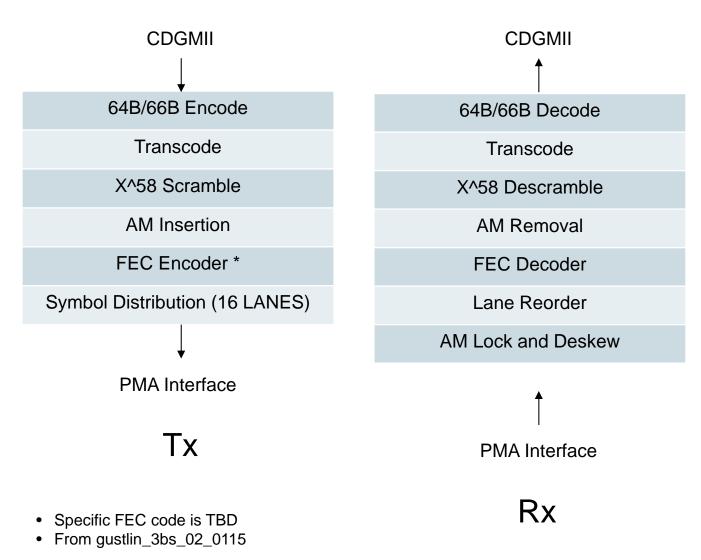

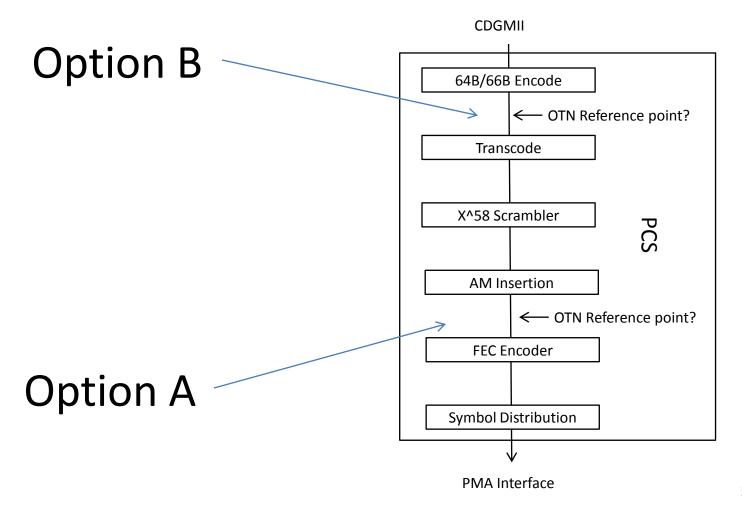

### **PCS Block Diagrams**

#### **PMA**

# The following are the functions performed by the PMA sublayer

- Provide appropriate multiplexing

- Provide appropriate modulation (PAM4 for instance if required)

- Provide per input-lane clock and data recovery

- Provide clock generation

- Provide signal drivers

- Optionally provide local loopback to/from the PMA service interface

- Optionally provide remote loopback to/from the PMD service interface

- Optionally provide test-pattern generation and detection

- Tolerate Skew Variation

- From gustlin\_3bs\_02\_0115

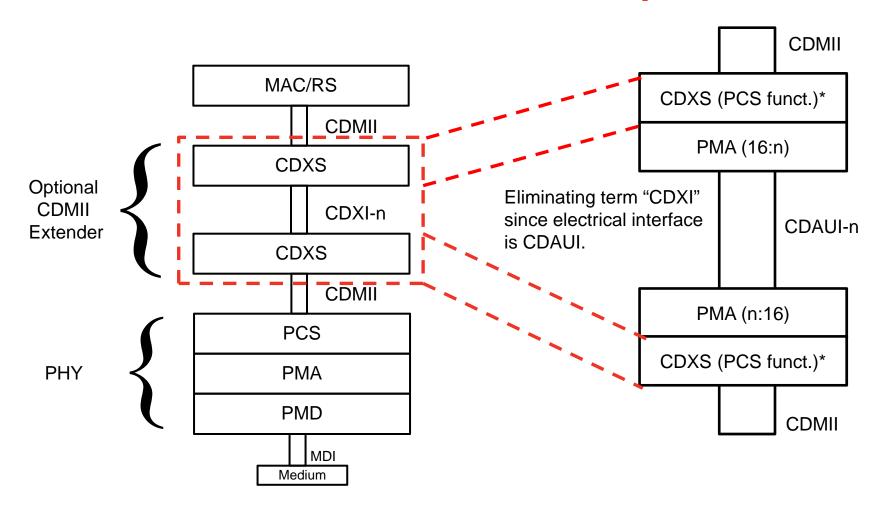

#### **Comments on CDXS**

- ➤ CDMII is the only media independent interface

- ➤ Different implementations or future PHYs may require changing FEC, which would require a return to CDMII (from a standardization perspective)

- ➤ The CDXS, as shown, is an extension of the CDMII.

- ➤ This allows support for new PCS / PMA functionality below the extended CDMII, if needed.

- ➤ The CDXS provides the coding / FEC of the electrical interface, not the coding / FEC of the PHY.

### **CDMII Extender Functional Concept**

**Initial Proposal**

**Updated Proposal**

\* Note - Same as PCS (including FEC) to be defined.

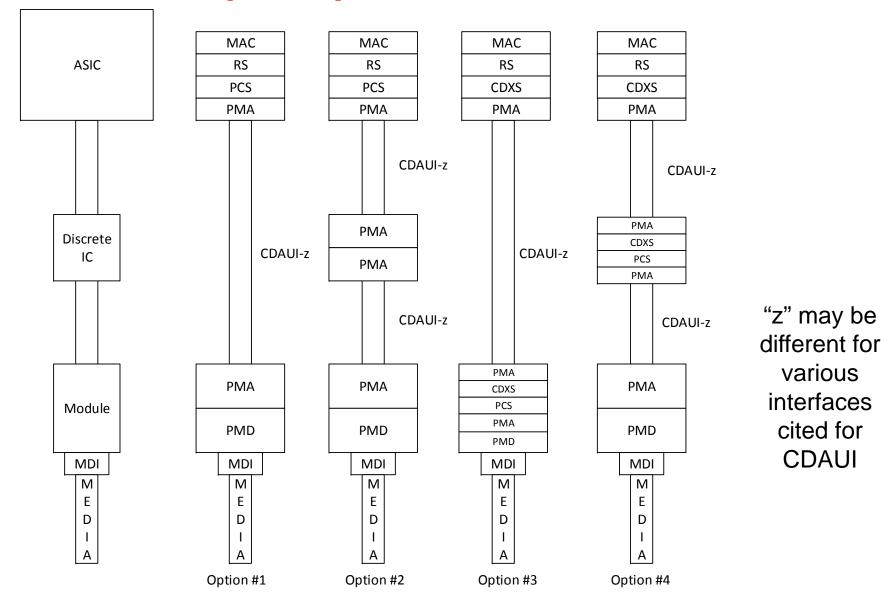

### **400GbE Example Implementations**

### Leveraging the Proposed Architecture

# Thanks!

### **400GbE MII Baseline Proposal**

#### IEEE P802.3bs 400 Gb/s Ethernet Task Force

July 2014 San Diego

Mark Gustlin – Xilinx

### **Supporters**

- ➤ John D'Ambrosia Dell

- ➤ Arthur Marris Cadence

- ➤ Dave Ofelt Juniper

- ➤ Steve Trowbridge ALU

#### **Proposed 400GbE Architecture**

- ➤ The protocol stack diagram shows one possible implementation

- ➤ The CDMII connects the MAC/RS sublayer to the Extender sublayer or the PCS

CDMII is the 400 Gb/s Media Independent Interface CDXS is the 400 Gb/s extender sublayer CDXI is the interface between two extender sublayers

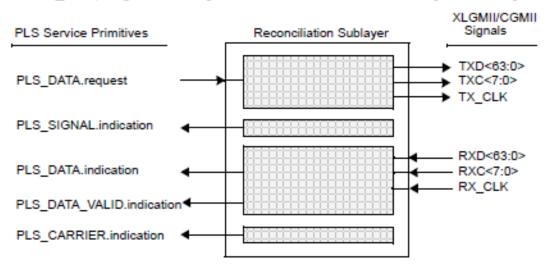

#### **CDMII** Interface

- ➤ Why define it?

- Electrically it won't be directly instantiated, but in the proposed 400GbE architecture it can be extended with an extender sublayer (CDXS) and interface (CDXI-n)

- Some will want it for RTL to RTL connections within devices

- ➤ Define it as a logical Interface only

- Unless it is extended, then there is a physical instantiation via an extender sublayer

#### What is it?

- ➤ Base it directly on clause 81

- ➤ Same signal structure as shown below, just run faster, or in parallel

#### 81.1.6 XLGMII/CGMII structure

The XLGMII/CGMII is composed of independent transmit and receive paths. Each direction uses 64 data signals (TXD<63:0> and RXD<63:0>), 8 control signals (TXC<7:0> and RXC<7:0>), and a clock (TX\_CLK and RX\_CLK). Figure 81-2 depicts a schematic view of the RS inputs and outputs.

Figure 81–2—Reconciliation Sublayer (RS) inputs and outputs

### **Extender Sublayer (CDXS)**

- ➤ The CDXS is the proposed extender sublayer to extend the CDMII

- A typical instantiation is a high speed parallel SerDes interface

- ➤ It is optional, only used if the PCS does not cover both the electrical and optical interface needs

- ➤ The CDXS can contain PCS, FEC, and PMA functionality

# Thanks!

# Baseline Proposal for CDAUI-8 Chip-to-Chip (c2c)

For IEEE 802.3bs

Mike Peng Li, Altera Adam Healey, Avago Technologies Philip Fisher, Avago Technologies Cathy Liu, Avago Technologie Ed Frlan, Semtech David Brown, Semtech

#### \*

#### **CDAUI-8 Baseline Proposal Supporters**

#### **Contributors and Supporters**

David Brown, Semtech

Philip Fisher, Avago Technologies

Ed Frlan, Semtech

Adam Healey, Avago Technologies

Mike Peng Li, Altera

Cathy Liu, Avago Technologies

#### **Supporters**

Thananya Baldwin, Ixia Vipul Bhatt, Inphi Sudeep Bhoja, InPhi Will Bliss, Broadcom Matt Brown, Applied Micro

Wheling Cheng, Ericsson

**Chris Cole, Finisar**

Ali Ghiasi, Ghiasi Quantum LLC

Sacha Corbeil, JDSU

Ian Dedic, Socionext Europe GmbH

John Ewen, IBM

Mike Furlong, Clariphy

Mark Gustlin, Xilinx

**Zhensheng Jia, ZTE**

Scott Kipp, Brocade

Beth Kochuparambil, Cisco

Martin Langhammer, Altera

Ryan Latchman, MACOM

**Greg LeCheminant, Keysight**

**David Lewis, JDSU**

Jon Lewis, Dell

**Kent Lusted, Intel**

Jeffery J. Maki, Juniper Networks

Marco Mazzini, Cisco

Richard Mellitz, Intel

**Gary Nicholl, Cisco**

Mark Nowell, Cisco

**David Ofelt, Juniper Networks**

Andre Szczepanek , InPhi

Jerry Pepper, Ixia

Rick Rabinovich, Alcatel-Lucent

**Enterprise**

Adee Ran, Intel

**Vineet Salunke, Cisco**

Kapil Shrikhande, Dell

**Jeff Slavick, Avago Technologies**

**Bharat Tailor, Semtech**

Vivek Telang, Broadcom

Alan Tipper, Semtech

Pirooz Tooyserkani, Cisco

Francois Tremblay, Semtech

Michael Vitic, JDSU

Xinyuan Wang, Huawei

**David Warren, HP Networking**

Brian Welch, Luxtera

Helen Xu, Huawei

Pavel Zivny, Tektronix

\* Changes since *li\_3bs\_01\_0115* shown in red

## Purposes

Present a PAM4 baseline specification proposal for CDAUI-8 c2c electrical interface in support of the 400 GbE to fulfill its objective of:

Support optional 400 Gb/s Attachment Unit Interfaces for chip-to-chip and chip-to-module applications

P802.3bs Berlin – Mar 2015

# Technology Choice Highlights 1

Channel target/requirement based on the equation of the following:

```

- IL <= { 1.083 + 2.543SQROOT(f) + 0.761f 0.01 <= f <= 28.05GHz} dB

```

as the informative insertion loss equation adopted by 802.3bs in Jan/2015 meeting

Channel equalization based on a transceiver having TX FIR, RX CTLE and DFE

# **Technology Choice Highlights 2**

Raw BER of CDAUI-8 link to be < 1E-6; FEC brings link system BER to < 1E-15</li>

# **Technology Choice Highlights 3**

- Leverage the 100GBASE-KP4 (i.e., KP4) specification from 13.59 GBd to 26.5625 GBd, and is consistent with CEI-56G-MR specification draft<sup>[1]</sup>

- Gray-code proposed, FEC (capable of bringing raw BER from 1e-6 to < 1e-15) assumed. FEC and pre-coding (if needed) specifics be defined by the FEC ad hoc

- Reuse KP4 test patterns, TX and RX methodologies for specifying electrical characteristics and corresponding tests

- Reuse CAUI-4 TX and RX diff and CM RLs, compliance point definitions (i.e., TP0a and TP5a)

- Reuse CAUI-4 link adaptation method (i.e., CL 83D.3.3.2 and 45)

- Reuse/improve 802.3bj COM method channel compliance with PAM4 signaling

### CDAUI-8 c2c Link Topology and IL Target

CDAUI-8 c2c compliance point definitions are the same as those defined in clause 83D.2 (CAUI-4)

# CDAUI-8 c2c Functional Spec

- CDAUI-8 PMA functional spec will be largely base on reusing, extending/modifying Clauses 94.2.2 (TX), 94.2.3 (RX), including

- FEC interface

- KP4 FEC, i.e., RS(544, 514, 10)

- Gray mapping

- PAM4 encoding

- Precoding

- Pending, the need and specifics ought to be studied and determined in the FEC ad hoc

### CDAUI-8 c2c Test Patterns

- CDAUI-8 PMA will reuse test patterns defined in clause 94.2.9, including:

- JP03A test pattern

- JP03B test pattern

- Quaternary PRBS13 test pattern (with the termination block (i.e., 94.2.2.4) removed, this will need to be changed accordingly)

- Transmitter linearity test pattern

## CDAUI-8 c2c TX Spec

| Parameter                                                                                                                                                                                                                                                                                                   | Subclause reference | Value                                                     | Units                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------------------------|----------------------|

| Signaling rate                                                                                                                                                                                                                                                                                              |                     | 26.5625                                                   | Gsym/s               |

| Differential peak-to-peak output voltage<br>(max.)<br>Transmitter disabled<br>Transmitter enabled                                                                                                                                                                                                           |                     | 30<br>1200                                                | mV<br>mV             |

| DC common-mode output voltage (max.)                                                                                                                                                                                                                                                                        |                     | 1.9                                                       | V                    |

| DC common-mode output voltage (min.)                                                                                                                                                                                                                                                                        |                     | 0                                                         | V                    |

| AC common-mode output voltage (RMS, max.)                                                                                                                                                                                                                                                                   |                     | 30                                                        | mV                   |

| Differential output return loss (min.)                                                                                                                                                                                                                                                                      |                     | <u>E.Q.</u> 17-4                                          | dB                   |

| Common-mode output return loss (min.)                                                                                                                                                                                                                                                                       |                     | <b>E.g.</b> 17-5                                          | dB                   |

| Output waveform  Level separation mismatch ratio,RLM(min) Steady-state voltage vf (max.) Steady-state voltage vf (min.) Linear fit pulse peak (min.) Normalized coefficient step size (min.) Normalized coefficient step size (max.) Pre-cursor full-scale range (min.) Post-cursor full-scale range (min.) |                     | 0.92<br>0.6<br>0.4<br>0.80 × vf<br>0.0083<br>0.05<br>1.54 | <br>v<br>v<br><br>   |

| Output jitter and linearity  Clock random jitter, RMS (max.)  Clock deterministic jitter, gg (max.)  Even-odd jitter (max.)  Signal-to-noise-and-distortion ratio (min.)                                                                                                                                    |                     | 0.01<br>0.04<br>0.019<br>31                               | UI<br>UI<br>UI<br>dB |

- TX output waveform definition and test method will reuse clause 94.3.12.5

- TX output jitter definition and test method will reuse clause 94.3.12.6

- TX output noise and distortion definition and test method will reuse clause 94.3.12.7

<sup>\*</sup> Updated to be aligned/consistent with healey\_3bs\_01\_0315

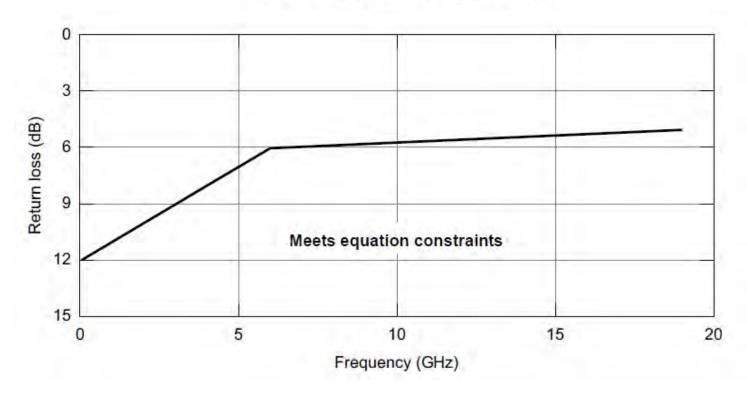

## CDAUI-8 c2c TX Diff RL Spec

$$RL_d(f) \ge \begin{cases} 12.05 - f & 0.05 \le f \le 6 \\ 6.5 - 0.075f & 6 < f \le 19 \end{cases}$$

dB

Reuse Eq. (93-3) and Fig (93-7)

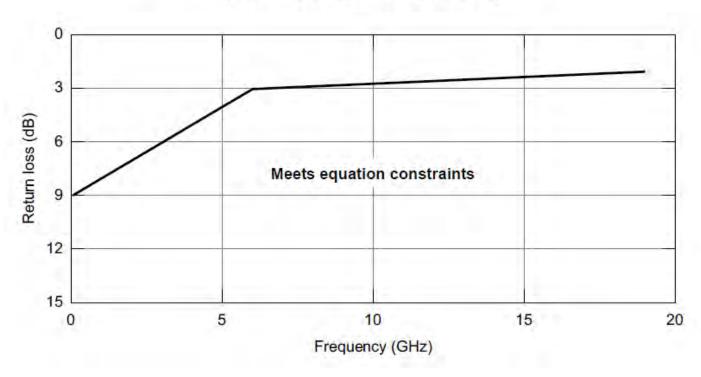

# CDAUI-8 c2c TX CM RL Spec

$$RL_{cm}(f) \ge \begin{cases} 9.05 - f & 0.05 \le f \le 6 \\ 3.5 - 0.075f & 6 < f \le 19 \end{cases}$$

dB

Reuse Eq. (93-4) and Fig (93-8)

# CDAUI-8 c2c RX Spec

| Parameter                                  | Symbol | Value    | Units | Conditions |

|--------------------------------------------|--------|----------|-------|------------|

| Differential Input Return Loss             |        | Slide 11 | dB    |            |

| Differential to Common-Mode<br>Return Loss |        | Slide 14 | dB    |            |

| Interference Tolerance                     |        | Slide 15 | -     |            |

| Jitter Tolerance                           |        | Slide 16 | -     |            |

|                                            |        |          |       |            |

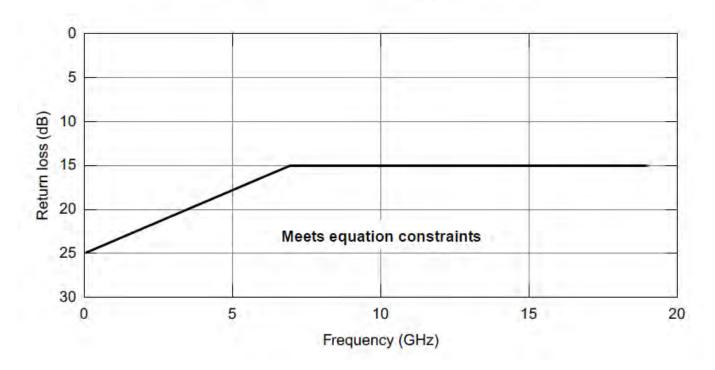

# CDAUI-8 c2c RX D2C RL Spec

$$RL_{cd}(f) = \begin{cases} 25 - 1.44f & 0.05 \le f \le 6.95 \\ 15 & 6.95 < f \le 19 \end{cases} dB$$

Reuse Eq. (93-5) and Fig (93-11)

#### CDAUI-8 c2c RX Interference Tolerance Parameters

| Parameter                                                       | Test 1 values     |                             | Test 2 values |                   | Units                       |        |                                                              |

|-----------------------------------------------------------------|-------------------|-----------------------------|---------------|-------------------|-----------------------------|--------|--------------------------------------------------------------|

|                                                                 | Min               | Max                         | Target        | Min               | Max                         | Target |                                                              |

| Symbol error ratio <sup>a</sup>                                 | _                 | 10 -5                       |               | _                 | 10 -5                       |        | _                                                            |

| Insertion loss at 13.2813 GHz <sup>b</sup>                      | 19.5              | 20.5                        |               | 9.5               | 10.5                        |        | dB                                                           |

| Coefficients of fitted insertion loss c<br>a0<br>a1<br>a2<br>a4 | -1<br>0<br>0<br>0 | 2<br>2.937<br>1.599<br>0.03 |               | -1<br>0<br>0<br>0 | 1<br>0.817<br>0.801<br>0.01 |        | dB<br>dB/GHz <sup>1/2</sup><br>dB/GHz<br>dB/GHz <sup>2</sup> |

| RSS_DFE4 d                                                      | 0.05              | _                           |               | 0.025             | <u> </u>                    |        | _                                                            |

| COM including effects of broad- band noise                      | _                 | _                           | 2             | _                 | _                           | 2      | dB                                                           |

<sup>&</sup>lt;sup>a</sup> The FEC symbol error ratio is measured in step 11 of the receiver interference tolerance method defined in 93C.2

Largely re-use of Table 83D-5 and method in 94.3.13.3

<sup>&</sup>lt;sup>b</sup> Measured between TPt and TP5 (see Figure 93C-4)

$<sup>^{\</sup>circ}$  Coefficients are calculated from the insertion loss measured between TPt and TP5 (see Figure 93C-4) using the method in 93A.3 with fmin = 0.05 GHz, and fmax = 26.5625. GHz, and maximum  $\Delta f$  = 0.01 GHz

<sup>&</sup>lt;sup>d</sup> RSS\_DFE4 is described in 93A.2.

#### CDAUI-8 c2c RX Jitter Tolerance Parameters

| Parameter        | Case A values | Case B values | Units      |

|------------------|---------------|---------------|------------|

| Max Pre-FEC BER  | 1e-6          | 1e-6          |            |

| Jitter frequency | fb/849600     | fb/8496       | same as fb |

| Jitter Amplitude | 5             | 0.05          | UI         |

|                  |               |               |            |

- Largely re-use method in 94.3.13.4

- fb is the BAUD rate

# CDAUI-8 c2c Channel Spec: COM (I)\*

| Parameter                                                                                                                                                                             | Symbol                               | Value                  | Units             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------|-------------------|

| Signaling rate                                                                                                                                                                        | fa.                                  | 26.5625                | GBd               |

| Maximum start frequency                                                                                                                                                               | <i>f</i> min                         | 0.05                   | GHz               |

| Maximum frequency step                                                                                                                                                                | Δf                                   | 0.01                   | GHz               |

| Device package model Single-ended device capacitance Transmission line length, Test 1 Transmission line length, Test 2 Single-ended package capacitance at package-to-board interface | Cd<br>ZR<br>ZR<br>Ca                 | TBD<br>12<br>30<br>TBD | oE.<br>om.<br>oE. |

| Single-ended reference resistance                                                                                                                                                     | R <sub>0</sub>                       | 50                     | Ω                 |

| Single-ended termination resistance                                                                                                                                                   | Rd                                   | TBD                    | Ω                 |

| Receiver 3 dB bandwidth                                                                                                                                                               | fr                                   | 0.75 × fb              |                   |

| Transmitter equalizer, minimum cursor coefficient                                                                                                                                     | c(0)                                 | 0.60                   | _                 |

| Transmitter equalizer, pre-cursor coefficient<br>Minimum value<br>Maximum value<br>Step size                                                                                          | c(-1)                                | -0.15<br>0<br>0.05     | _<br>_<br>_       |

| Transmitter equalizer, post-cursor coefficient<br>Minimum value<br>Maximum value<br>Step size                                                                                         | c(1)                                 | -0.25<br>0<br>0.05     | _<br>_<br>_       |

| Continuous time filter, DC gain<br>Minimum value<br>Maximum value<br>Step size                                                                                                        | gpc                                  | -15<br>0<br>1          | #B.               |

| Continuous time filter, zero frequency                                                                                                                                                | £.                                   | f <sub>b</sub> / 4     | GHz               |

| Continuous time filter, pole frequencies                                                                                                                                              | f <sub>p</sub> 1<br>f <sub>p</sub> 2 | ₽/4<br>₽               | GHz               |

| Transmitter differential peak output voltage<br>Victim<br>Far-end aggressor<br>Near-end aggressor                                                                                     | Ax<br>Ate.<br>Aoe.                   | 0.4<br>0.4<br>0.6      | v<br>v            |

\* Updated to be aligned/consistent with healey\_3bs\_01\_0315

# CDAUI-8 c2c Channel Spec: COM (II)

| I.                                                                               | 0000             |                        | 1.*                 |

|----------------------------------------------------------------------------------|------------------|------------------------|---------------------|

| Number of signal levels                                                          | L                | 4                      | _                   |

| Level separation mismatch ratio                                                  | RLM              | 0.92                   | _                   |

| Transmitter signal-to-noise ratio                                                | SNRTX            | 31                     | dB                  |

| Number of samples per unit interval                                              | M                | 32                     | _                   |

| Decision feedback equalizer (DFE) length                                         | Nb               | 5                      | UI                  |

| Normalized DFE coefficient magnitude limit for n = 1 for n = 2 to N <sub>b</sub> | Dmax(n)          | 1 0.2                  | _                   |

| Random jitter, RMS                                                               | <b>ORJ</b>       | 0.01                   | UI                  |

| Dual- <u>Dirac jitter, peak</u>                                                  | ADD              | 0.02                   | UI                  |

| One-sided noise spectral density                                                 | ηο               | 5.2 × 10 <sup>-8</sup> | V <sup>2</sup> /GHz |

| Target detector error ratio                                                      | DER <sub>0</sub> | 10 <sup>-8</sup>       | _                   |

\* Updated to be aligned/consistent with healey\_3bs\_01\_0315

# Summary

- A baseline proposal based PAM4 signaling for CDAUI-8 c2c electrical interface specification has been developed

- Intent is to support existing CAUI-4 c2c channel and testing infrastructures

- Reused/extended/modified from 100GBase-KP4 and CAUI-4 c2c specifications (i.e., clauses 94, 93A, and 83D)

- Consistent with CEI-56G-MR adopted baseline specification in modulation and in general

# References

[1] oif2014.245.01, www.oiforum.com

(That document was provided as an attachment to the October 28, 2014 liaison from OIF to IEEE 802.3. The liaison and its attachments can be found in the IEEE P802.3bs 400 Gb/s Ethernet Task Force private area)

# Baseline Proposal for CDAUI-8 Chip-to-Module (c2m)

For IEEE 802.3bs

Mike Peng Li, Altera

Adam Healey, Avago Technologies

Philip Fisher, Avago Technologies

Cathy Liu, Avago Technologies

Ed Frlan, Semtech

David Brown, Semtech

#### CDAUI-8 c2m Baseline Document Supporters

#### \*

#### **Contributors and Supporters**

- David Brown, Semtech

- Philip Fisher, Avago Technologies

- Ed Frlan, Semtech

- Adam Healey, Avago Technologies

- Mike Peng Li, Altera

- Cathy Liu, Avago Technologies

#### **Supporters**

Thananya Baldwin, Ixia

Vipul Bhatt, Inphi

Sudeep Bhoja, InPhi

Will Bliss, Broadcom

Matt Brown, Applied Micro

Wheling Cheng, Ericsson

**Chris Cole, Finisar**

Sacha Corbeil, JDSU

**Ian Dedic, Socionext Europe**

John Ewen, IBM

Mike Furlong, Clariphy

Ali Ghiasi, Ghiasi Quantum LLC

Mark Gustlin, Xilinx

Zhensheng Jia, ZTE

Scott Kipp, Brocade

Beth Kochuparambil, Cisco

Martin Langhammer, Altera

Ryan Latchman, MACOM

**Greg Le Cheminant, Keysight**

**David Lewis, JDSU**

Jon Lewis, Dell

**Kent Lusted, Intel**

Jeffery J. Maki, Juniper

**Networks**

Marco Mazzini, Cisco

Richard Mellitz, Intel

Gary Nicholl, Cisco Mark Nowell, Cisco

David Ofelt, Juniper

Jerry Pepper, Ixia

Rick Rabinovich, Alcatel-Lucent

**Enterprise**

Adee Ran, Intel

Vineet Salunke, Cisco

Kapil Shrikhande, Dell

**Jeff Slavick, Avago Technologies**

Andre Szczepanek, InPhi

**Bharat Tailor, Semtech**

Vivek Telang, Broadcom

Alan Tipper, Semtech

Pirooz Tooyserkani, Cisco

François Tremblay, Semtech

Michael Vitic, JDSU

Xinyuan Wang, Huawei

**David Warren, HP Networking**

Brian Welch, Luxtera

Helen Xu, Huawei

**Pavel Zivny, Tektronix**

\* Changes since brown 3bs 01a\_0115 shown in red

# Purpose

Present a baseline specification proposal for CDAUI-8 c2m electrical interface in support of the 400 GbE Task Force to fulfill its objective of:

Support optional 400 Gb/s Attachment Unit Interfaces for chip-to-chip and chip-to-module applications

# **Technology Choice Highlights 1**

Channel target/requirement based on the following equation:

```

IL \le \{ 1.076(0.075 + 0.537SQROOT(f) + 0.566f) \quad 0.01 \le f \le 28.05GHz \} dB

```

as the informative insertion loss adopted by 802.3bs at the Jan/2015 Interim meeting

- Channel equalization based on a transceiver having autonomous Rx CTLE

- Tx FIR or Rx DFE not specified in host or module transceivers. (Allowed, but not mandated.)

# **Technology Choice Highlights 2**

Raw BER of CDAUI-8 c2m link to be < 1e-6; FEC brings link system BER to < 1e-15</li>

#### \*

# **Technology Choice Highlights 3**

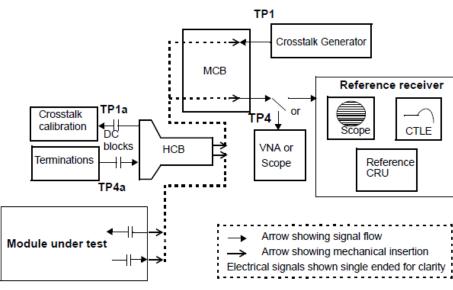

- Leverage the CEI-56G-VSR-PAM4 draft specification<sup>[1]</sup> using one data rate:

- 26.5625GBd

- Gray-code specified, FEC assumed but not specified

- Pre-coding not assumed since CTLE-only

- Reuse CAUI-4 c2m Tx and Rx methodologies for specifying electrical characteristics and corresponding tests

- Diff and CM RLs and compliance point definitions

- HCB/MCB method for channel compliance, adapted for PAM-4 signaling

- Remove "recommended CTLE" mechanism

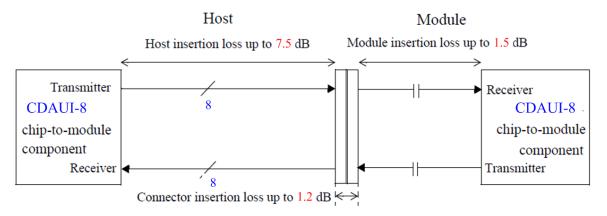

# CDAUI-8 Chip-to-Module Link

|                               | CAUI-4 (83E.3.1 TP1a)     | VSR 56G (15.3.2, TP1a) | CDAUI-8 Chip-Module Potential         |

|-------------------------------|---------------------------|------------------------|---------------------------------------|

| Modulation                    | NRZ                       | PAM-4 (Gray coded)     | PAM-4 (Gray coded)                    |

| Nominal Signaling Rate        | 25.78125 Gb/s +/- 100 ppm | 19.6 ≤ fb ≤ 30 GBd     | 26.5625 GBd +/- 100 ppm               |

| (each lane)                   |                           |                        | 28 GBd (TBD) <sup>a</sup> +/- 100 ppm |

| Unit Interval                 | 38.787879 ps              | 33.33 ps - 51 ps       | 37.647059 ps                          |

|                               |                           |                        | 35.65 ps (TBD)*                       |

| Loss Budget, max <sup>b</sup> | 10 dB                     | 10.8 dB <sup>c</sup>   | 10.3 dB                               |

| Uncorrected BER               | < 1e-15                   | < 1e-6                 | < 1e-6                                |

| Corrected BER                 | n/a                       | n/a                    | < 1e-15                               |

<sup>\*</sup>Two operating signaling rates, with choice of higher rate pending PMA FEC selection.

<sup>c</sup> Informative.

Chip-to-module insertion loss budget at 13.28 GHz

<sup>&</sup>lt;sup>b</sup> At 1/2 symbol rate, comprising host PCB trace, module PCB trace, AC-coupling capacitors and one connector.

- Target IL curve is "extended CAUI-4 c2m" as adopted at Jan/2015 Interim

- Loss at Nyquist (13.28GHz) = 10.27 dB

- Working assumption: all IL curves shown are suitable for PAM4 signaling at 28GBd

- Consider potential to operate over legacy CAUI-4 c2m channels

# **CDAUI-8 Host Transmitter**

|                                                                 | CAUI-4 (83E.3.1 TP1a)                                                 | VSR 56G (15.3.2, TP1a)                                             | CDAUI-8 Chip-Module Potential                                         |

|-----------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------|

| Differential peak-to-peak output voltage (max) with Tx enabled  | 900 mV                                                                | 900 mV                                                             | 900 mV                                                                |

| AC common-mode output voltage (max)                             | 17.5 mVrms                                                            | 17.5 mVrms                                                         | 17.5 mVrms                                                            |

| Differential peak-to-peak output voltage (max) with Tx disabled | 35 mV                                                                 | -                                                                  | 35 mV                                                                 |

| Differential termination mismatch (max)                         | 10 %                                                                  | 10 %                                                               | 10 %                                                                  |

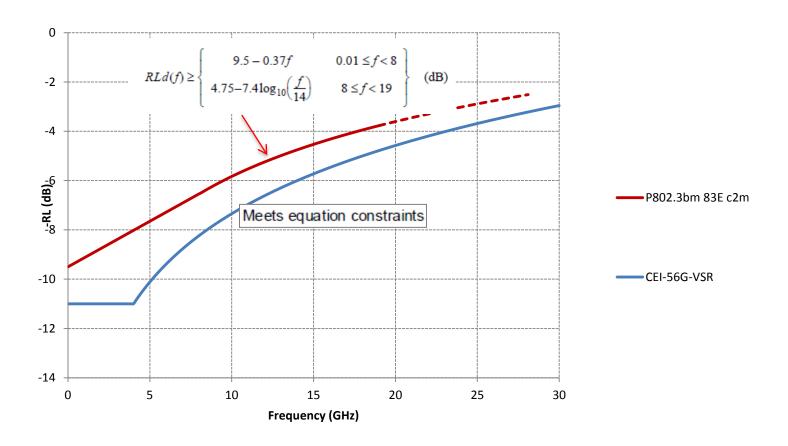

| Differential output return loss (min)                           | ≥ 9.5-0.37f, 0.01≤f≤8 GHz                                             | ≥ 11, 0.05≤f≤fb/7 GHz                                              | ≥ 9.5-0.37f, 0.01≤f≤8 GHz                                             |

|                                                                 | $\geq$ 4.75-7.4log <sub>10</sub> (f/14), 8 $\leq$ f $\leq$ 19 GHz     | $\geq$ 6-9.2log <sub>10</sub> (2f/fb), fb/7 $\leq$ f $\leq$ fb GHz | $\geq$ 4.75-7.4log <sub>10</sub> (†/14), 8 $\leq$ † $\leq$ 19 GHz     |

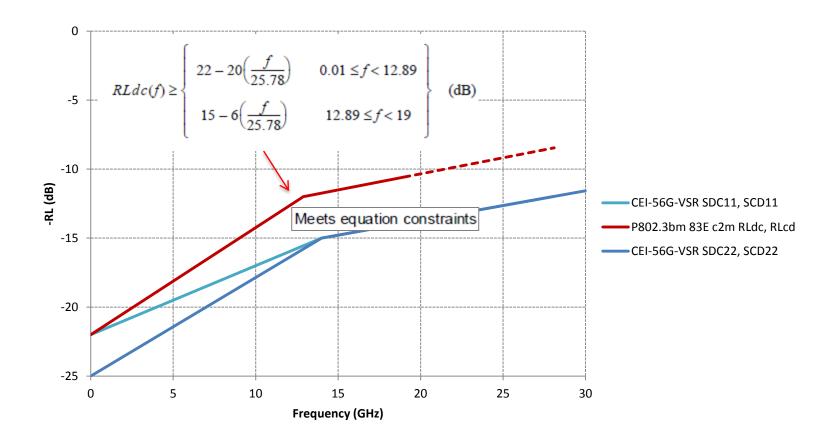

| Common-mode to differential output return loss (min)            | ≥ 22-(20/25.78)f, 0.01≤f≤12.89 GHz<br>≥ 15-(6/25.78)f, 12.89≤f≤19 GHz | ≥ 22-14f/fb, 0.05≤f≤fb/2 GHz<br>≥ 18-6f/fb, fb/2≤f≤fb GHz          | ≥ 22-(20/25.78)f, 0.01≤f≤12.89 GHz<br>≥ 15-(6/25.78)f, 12.89≤f≤19 GHz |

| Common-mode output return loss (min)                            | -                                                                     | 2 dB                                                               | 2 dB                                                                  |

| DC common-mode output voltage (max)                             | 2.8 V                                                                 | 2.8 V                                                              | 2.8 V                                                                 |

| DC common-mode output voltage (min)                             | -0.3 V                                                                | -0.3 V                                                             | -0.3 V                                                                |

| Eye Width (min)                                                 | 0.46 UI at 1e-15                                                      | 0.25 UI at 1e-6                                                    | 0.25 UI at 1e-6                                                       |

|                                                                 |                                                                       | applicable to all three PAM4 eyes                                  | applicable to all three PAM4 eyes                                     |

| Output total jitter (max)                                       | TJ: 0.54Ulpp @ 1e-15                                                  | TJ: 0.75Ulpp @ 1e-6                                                | TJ: 0.75Ulpp @ 1e-6                                                   |

|                                                                 | Measured using CTLE                                                   | Measured using CTLE                                                | Measured using CTLE                                                   |

| Eye Height (min)                                                | 95 mV at 1e-15                                                        | 50 mV at 1e-6                                                      | 50 mV at 1e-6                                                         |

|                                                                 |                                                                       | applicable to all three PAM4 eyes                                  | applicable to all three PAM4 eyes                                     |

| Transition time (min, 20/80%)                                   | 10 ps                                                                 | -                                                                  | -                                                                     |

|                                                                 |                                                                       |                                                                    |                                                                       |

# **CDAUI-8 Module Receiver**

|                                            | CAUI-4 (83E.3.1 TP1)                           | VSR 56G (15.3.2, TP1)                                              | CDAUI-8 Chip-Module Potential                                     |

|--------------------------------------------|------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------|

| Differential peak-to-peak input voltage    | 900 mV                                         | 900 mV                                                             | 900 mV                                                            |

| tolerance (min)                            |                                                |                                                                    |                                                                   |

| Single-ended voltage tolerance range (min) | -0.4 to 3.3 V                                  | -                                                                  | -                                                                 |

| DC common-mode input voltage (max)         | 2.85 V                                         | 2.85 V                                                             | 2.85 V                                                            |

| DC common-mode input voltage (min)         | -0.35 V                                        | -0.35 V                                                            | -0.35 V                                                           |

| Differential termination mismatch (max)    | 10 %                                           | 10 %                                                               | 10 %                                                              |

| Differential input return loss (min)       | ≥ 9.5-0.37f, 0.01≤f≤8 GHz                      | ≥ 11, 0.05≤f≤fb/7 GHz                                              | ≥ 9.5-0.37f, 0.01≤f≤8 GHz                                         |

|                                            | ≥ 4.75-7.4log <sub>10</sub> (f/14), 8≤f≤19 GHz | $\geq$ 6-9.2log <sub>10</sub> (2f/fb), fb/7 $\leq$ f $\leq$ fb GHz | $\geq$ 4.75-7.4log <sub>10</sub> (f/14), 8 $\leq$ f $\leq$ 19 GHz |

| Differential to common mode input return   | ≥ 22-(20/25.78)f, 0.01≤f≤12.89 GHz             | ≥ 22-14f/fb, 0.05≤f≤fb/2 GHz                                       | ≥ 22-(20/25.78)f, 0.01≤f≤12.89 GHz                                |

| loss (min)                                 | ≥ 15-(6/25.78)f, 12.89≤f≤19 GHz                | ≥ 18-6f/fb, fb/2≤f≤fb GHz                                          | ≥ 15-(6/25.78)f, 12.89≤f≤19 GHz                                   |

| Module stressed input test                 | 83E.3.4.1                                      | 15.3.10.2.1                                                        | Same as VSR                                                       |

# **CDAUI-8 Module Transmitter**

|                                          | 1                                              | *                                                                  | •                                              |

|------------------------------------------|------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------|

|                                          | CAUI-4 (83E.3.2 TP4)                           | VSR 56G (15.3.3, TP4)                                              | CDAUI-8 Chip-Module Potential                  |

| Differential peak-to-peak output voltage | 900 mV                                         | 900 mV                                                             | 900 mV                                         |

| (max) with Tx enabled                    |                                                |                                                                    |                                                |

| AC common-mode output voltage (max)      | 17.5 mVrms                                     | 17.5 mVrms                                                         | 17.5 mVrms                                     |

| Differential termination mismatch (max)  | 10 %                                           | 10 %                                                               | 10 %                                           |

| Differential output return loss (min)    | ≥ 9.5-0.37f, 0.01≤f≤8 GHz                      | ≥ 11, 0.05≤f≤fb/7 GHz                                              | ≥ 9.5-0.37f, 0.01≤f≤8 GHz                      |

|                                          | ≥ 4.75-7.4log <sub>10</sub> (f/14), 8≤f≤19 GHz | $\geq$ 6-9.2log <sub>10</sub> (2f/fb), fb/7 $\leq$ f $\leq$ fb GHz | ≥ 4.75-7.4log <sub>10</sub> (f/14), 8≤f≤19 GHz |

| Common-mode to differential mode         | ≥ 22-(20/25.78)f, 0.01≤f≤12.89 GHz             | ≥ 22-14f/fb, 0.05≤f≤fb/2 GHz                                       | ≥ 22-(20/25.78)f, 0.01≤f≤12.89 GHz             |

| output return loss (min)                 | ≥ 15-(6/25.78)f, 12.89≤f≤19 GHz                | ≥ 18-6f/fb, fb/2≤f≤fb GHz                                          | ≥ 15-(6/25.78)f, 12.89≤f≤19 GHz                |

| Common-mode output return loss (min)     | -                                              | 2 dB                                                               | 2 dB                                           |

| DC common-mode output voltage (max)      | 2.85 V                                         | 2.85 V                                                             | 2.85 V                                         |

| DC common-mode output voltage (min)      | -0.35 V                                        | -0.35 V                                                            | -0.35 V                                        |

| Vertical Eye Closure (max)               | 5.5 dB                                         | 5.8 dB                                                             | 5.8dB                                          |

| Eye Width (min)                          | 0.57 UI at 1e-15                               | 0.4 UI at 1e-6                                                     | 0.4 UI at 1e-6                                 |

|                                          |                                                | applicable to all three PAM4 eyes                                  | applicable to all three PAM4 eyes              |

| Output total jitter (max)                | TJ: 0.43Ulpp @ 1e-15                           | TJ: 0.6Ulpp @ 1e-6                                                 | TJ: 0.6Ulpp @ 1e-6                             |

|                                          | Measured using CTLE                            | Measured using CTLE                                                | Measured using CTLE                            |

| Eye Height (min)                         | 228 mV at 1e-15                                | 120 mV at 1e-6                                                     | 120 mV at 1e-6                                 |

|                                          |                                                | applicable to all three PAM4 eyes                                  | applicable to all three PAM4 eyes              |

| Transition time (min, 20/80%)            | 12 ps                                          | -                                                                  | -                                              |

# **CDAUI-8 Host Receiver**

|                                                         | CAUI-4 (83E.3.2 TP4a)                                                                                             | VSR 56G (15.3.2, TP4a)                                                                                       | CDAUI-8 Chip-Module Potential                                                                                     |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Differential peak-to-peak input voltage tolerance (min) | 900 mV                                                                                                            | 900 mV                                                                                                       | 900 mV                                                                                                            |

| DC common-mode input voltage (max)                      | 2.8 V                                                                                                             | 2.8 V                                                                                                        | 2.8 V                                                                                                             |

| DC common-mode input voltage (min)                      | -0.3 V                                                                                                            | -0.3 V                                                                                                       | -0.3 V                                                                                                            |

| Differential termination mismatch (max)                 | 10 %                                                                                                              | 10 %                                                                                                         | 10 %                                                                                                              |

| Differential input return loss (min)                    | $\geq$ 9.5-0.37f, 0.01 $\leq$ f $\leq$ 8 GHz<br>$\geq$ 4.75-7.4log <sub>10</sub> (f/14), 8 $\leq$ f $\leq$ 19 GHz | ≥ 11, $0.05 \le f \le fb/7 \text{ GHz}$<br>≥ 6-9.2log <sub>10</sub> (2f/fb), fb/7 $\le f \le fb \text{ GHz}$ | $\geq$ 9.5-0.37f, 0.01 $\leq$ f $\leq$ 8 GHz<br>$\geq$ 4.75-7.4log <sub>10</sub> (f/14), 8 $\leq$ f $\leq$ 19 GHz |

| Differential to common-<br>mode input return loss (min) | ≥ 22-(20/25.78)f, 0.01≤f≤12.89 GHz<br>≥ 15-(6/25.78)f, 12.89≤f≤19 GHz                                             | ≥ 22-14f/fb, 0.05≤f≤fb/2 GHz<br>≥ 18-6f/fb, fb/2≤f≤fb GHz                                                    | ≥ 22-(20/25.78)f, 0.01≤f≤12.89 GHz<br>≥ 15-(6/25.78)f, 12.89≤f≤19 GHz                                             |

| Host stressed input test                                | 83E.3.3.2                                                                                                         | 15.3.10.2.1                                                                                                  | Same as VSR                                                                                                       |

| Jitter tolerance                                        | -                                                                                                                 | -                                                                                                            | -                                                                                                                 |

#### CDAUI-8 c2m Tx & Rx Differential Return Loss Spec

Same as Annex 83E (CAUI-4 c2m)

# CDAUI-8 c2m Tx Common-Mode to Differential & Rx Differential to Common-Mode Return Loss Specs

Same as Annex 83E (CAUI-4 c2m)

# **Compliance Boards**

- Same as CR4 (Cl. 92)

- No new compliance boards required

## CDAUI-8 c2m Test Patterns

- CDAUI-8 PMA can reuse test pattern defined in clause 94.2.9:

- Quaternary PRBS13 test pattern (if the termination block (i.e., 94.2.2.4) is removed, this will need to be changed accordingly)

- Other KP4 test patterns (JP03A, JP03B) not required

# CDAUI-8 c2m PAM4 Jitter and Eye Height Parameters

See Appendix for measurement procedure

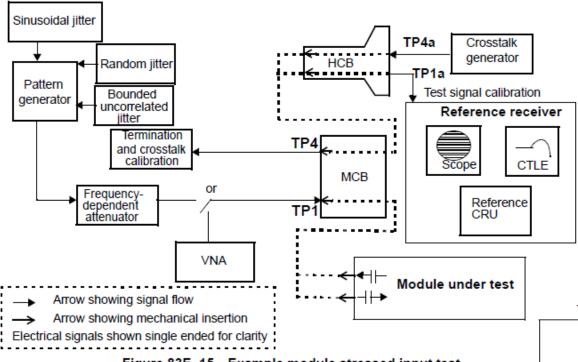

## Module Stressed Receiver Test

- Same test configuration as Annex 83E

- Modified for PAM4 testing consistent with 56G-VSR-PAM4

- CRU and SIJT corner frequencies pending further study

Figure 83E-15—Example module stressed input test

Table 15-7. Sinusoidal jitter frequency for TP4 and TP1 testing

| Frequency Range (Hz)                               | Sinusoidal jitter,<br>Peak to peak<br>(UI) |

|----------------------------------------------------|--------------------------------------------|

| f <fb 849600<="" td=""><td>Not Specified</td></fb> | Not Specified                              |

| fb/849600 < f < fb/8496                            | 5*fb/(849600*f)                            |

| fb/8496 < f < 10xLB                                | 0.05                                       |

| NOTES:LB = Receiver Loop Bandwidth                 |                                            |

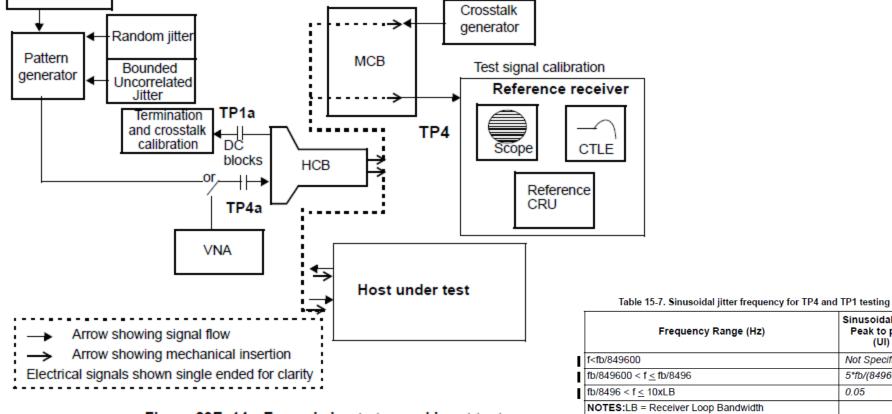

## Host Stressed Receiver Test

Same test configuration as Annex 83E

Sinusoidal jitter

- Modified for PAM4 testing consistent with 56G-VSR-PAM4

- CRU and SIJT corner frequencies pending further study

TP1

Figure 83E-14—Example host stressed input test

Sinusoidal jitter, Peak to peak

Not Specified

5\*fb/(849600\*f)

0.05

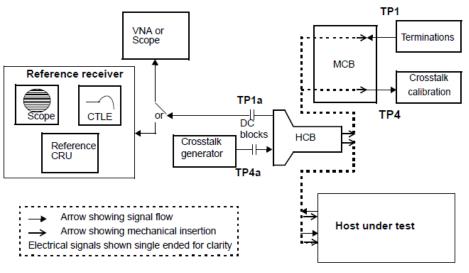

# Host / Module Output Waveform Test

- Same test configuration as Annex 83E

- Modified for PAM4 testing consistent with 56G-VSR-PAM4

- CRU corner frequency pending further study

Figure 83E-9—Example host output test configuration

Figure 83E-11—Example module output test configuration

# Summary

- Baseline proposal using PAM4 signaling for a CDAUI-8 c2m electrical interface specification:

- -Supports CAUI-4 c2m channel

- -Reuses test infrastructures and setup in Annex 83E

- Is consistent with CEI-56G-VSR draft baseline specification

- Straightforward to extend/modify Annex 83E specification for PAM4 signaling

# References

[1] oif.2014.230.01, <a href="www.oiforum.com">www.oiforum.com</a> (This document was provided as an attachment to the October 28, 2014 liaison from OIF to IEEE 802.3. The liaison and its attachments can be found in the IEEE P802.3bs 400 Gb/s Ethernet Task Force private area)

# **Appendix**

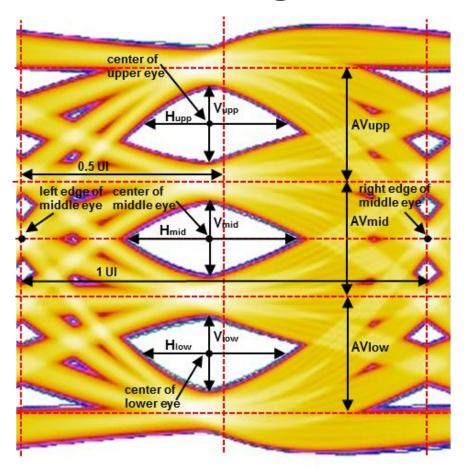

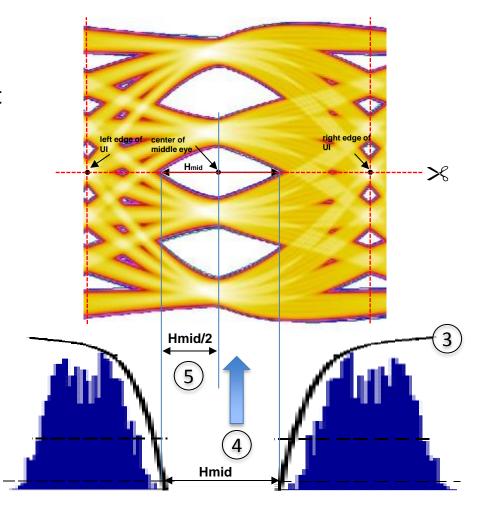

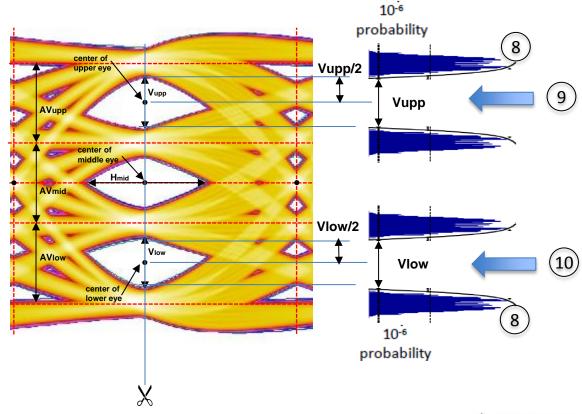

Extracting PAM4 Eye Width and Height

#### Reuse Annex 83E.4.2 method to:

- Capture QPRBS13 pattern (> 4 million symbols)

- 2. Apply reference CTLE

- 3. Construct CDFs of eye edges at zero crossing

- 4. Hmid = 1e-6 inner eye width

- 5. Locate center of middle eye at Hmid/2

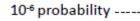

#### Reuse Annex 83E.4.2 method to:

- 6. Construct CDFs of signal voltages of middle eye sampled at Hmid/2

- 7. Vmid = 1e-6 inner eye height

#### Extract upper and lower eye heights

- 8. Construct CDFs of signal voltages of upper and lower eyes at Hmid/2

- 9. Vup = 1e-6 inner height of upper eye at Hmid/2

- 10. Vlow = 1e-6 inner height of lower eye at Hmid/2

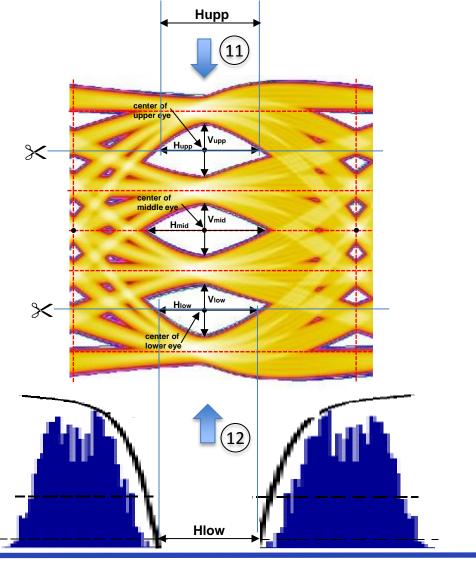

#### Extract upper and lower eye widths

- 11. Hupp = 1e-6 inner width of upper eye sliced at Vupp/2

- 12. Hlow = 1e-6 inner width of lower eye sliced at Vlow/2

10-6 probability -----

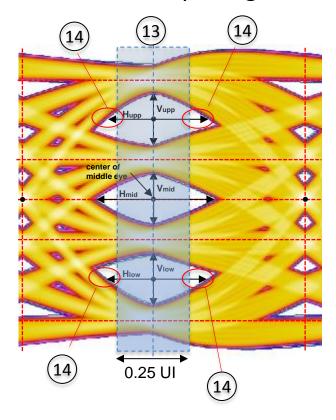

- Check upper and lower eye alignment to middle eye

- 13. Apply 0.25UI-wide mask centered on middle eye

- 14. 1e-6 horizontal openings of upper and lower eyes must extend outside this mask, measured at ½ inner eye height

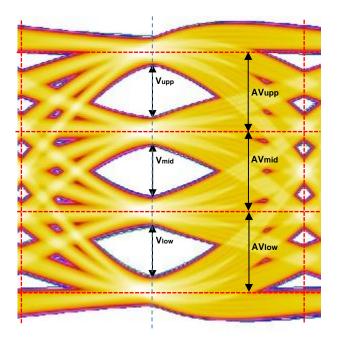

#### Module Output VEC Measurement

15. Calculate VEC as 20log[min(AVupp/Vupp, AVmid/Vmid, AVlow/Vlow)]

Energy Efficient Ethernet (EEE) for 802.3bs Arthur Marris - Cadence

# Supporters

- Mark Gustlin Xilinx

- Andre Szczepanek Inphi

- Dave Ofelt Juniper

- Gary Nicholl Cisco

# Key features of Energy Efficient Ethernet (EEE)

- If a system has nothing to transmit it can power down its transmit path after it has indicated its intention to do so.

- The partner device can also power down its receive path when it detects that the path is going to be powered down.

- The link stays up while in low power mode and no frames are dropped.

- EEE is asymmetric. One direction can be powered up while the other is powered down.

#### How does EEE work?

- The client (i.e. system) requests Low Power Idle (LPI) from the reconciliation sublayer (RS).

- The RS then signals LPI on the MII (media independent interface).

- The transmit PCS (physical coding sublayer) encodes the LPI signal using a special symbol.

- The receive PCS decodes the LPI symbol and signals LPI on the receive MII.

- When the client ceases requesting LPI the RS continues inhibiting transmission for a fixed period to allow time for the local transmit path and remote receive path to recover from their low power modes.

# What is "Fast Wake" mode of operation?

- In Fast Wake mode of operation the transmit and receive path remain active and continuously transmit and receive LPI when it is requested by the client. (However Clause 82 BIP is not calculated)

- Fast Wake is compulsory for 40G and 100G PHYs that support EEE.

- Fast Wake is controlled by LLDP (Link Layer Discovery Protocol) rather than AN (auto-negotiation)

- Fast Wake is suitable for optical PHYs that unable to power up and down quickly and do not support AN.

# What is "Deep Sleep" mode of operation?

- In Deep Sleep mode the transmit path stops transmitting but periodically sends refresh indication while LPI is requested.

- In Deep Sleep mode the receiver checks for the occurrence of refresh indication and will assert link failure if refresh does not appear.

- Deep Sleep mode requires the receive PMA and PCS to resume operation within a determined time period.

- In Deep Sleep mode the transmit and receive PCS generate tx\_quiet and rx\_quiet signals to allow the PHY to periodically power down its transmit and receive path.

- Clause 83 defines a mechanism for sending the tx\_quiet signal over the CAUI/XLAUI interface and for synthesizing the rx\_quiet signal.

- As only optical PHYs are included in the 802.3bs objectives, none of the PHYs specified in 802.3bs will support Deep Sleep operation, however the architecture should not preclude support for Deep Sleep in the future.

#### What should be done for 802.3bs?

- Adopt Fast Wake mode of operation for the 802.3bs PHY types.

- Add these PHY types to "Table 78-1 Clauses associated with each PHY or interface type" and indicate that they do not support deep sleep with the "b" suffix.

- The CDMII will need to be able to signal LPI and the RS will need to include a transmit LPI state machine to defer transmission for the wake time period after de-assertion of LPI.

- The PCS will need to be able to encode and decode LPI.

## Further considerations for supporting EEE in 802.3bs

- Consider whether the receive PCS should have a "RX\_FW" state that it goes into when receiving LPI from its link partner. In this state it could disable error checking.

- When specifying the CDAUI electrical interface consider defining a mechanism for transmitting alert and quiet signalling similar to how it is done in 83.5.11.1 to allow for future support of Deep Sleep, and also consider generation of an energy detect signal.

- To support Deep Sleep mode the PCS needs to achieve synchronization and alignment quickly. This will most likely be done through the use of "rapid alignment markers" so make sure the architecture does not preclude their use in the future.

- If Deep Sleep is supported in the future then the CDXI may need to be powered down. In this case it would be necessary to preserve the MII signalling of LPI to the PCS in the transmit direction and LPI to the MAC in the receive direction until the interface powers up. Also it will be necessary for the CDXI to power up quickly.

### Summary

- 802.3bs will use EEE fast wake functionality which requires the CDMII to signal LPI and the PCS to encode and decode it

- To allow for future support of deep sleep functionality consideration needs to be given to how the PCS and electrical interfaces can resume operation quickly after power down

# OTN Support Proposal P802.3bs 400 Gb/s Ethernet Task Force

Steve Trowbridge

Alcatel-Lucent

#### Supporters

- Pete Anslow (Ciena)

- Gary Nicholl (Cisco)

- Tongtong Wang (Huawei)

- Xinyan Wang (Huawei)

- David Ofelt (Juniper)

- Andre Szczepanek (Inphi)

### Key Elements of OTN Support

- See "OTN Support: What is it and why is it important?", July 2013

- A new rate of Ethernet (e.g., 400 Gb/s) fits into the corresponding rate OTN transport signal

- All Ethernet PHYs of a given rate are mapped the same way and can be interconnected over the OTN (e.g., same PCS for all 100 Gb/s PHYs gives a single canonical format ("characteristic information" in ITU-T terminology) that can be mapped

- Optical modules for Ethernet can be reused for OTN IrDI/client interfaces at the corresponding rate

### A new rate of Ethernet (e.g., 400 Gb/s) fits into the corresponding rate OTN transport signal

- Assumption the OTN mapper/demapper will terminate and regenerate any Ethernet FEC code, correcting errors at the OTN ingress since the FEC is chosen to correct singlelink errors but not double-link errors

- Assumption the OTN mapper/demapper may transdecode/trans-encode back to 64B/66B to avoid MTTFPA reduction for OTN transported signal

- Based on these assumptions, the encoded data rate of the OTN-mapped 400 Gb/s Ethernet would be no more than 400 Gb/s x 66 / 64 = 412.5 Gb/s ±100ppm. Since the 400 Gb/s OTN container would presumably be designed to also transport four "lower order" ODU4s, there should be no concern that it is large enough to carry 400 Gb/s Ethernet based on the assumption that the canonical form is near this rate.

- Any Ethernet bits in excess of this rate are likely to be part of a FEC that is not carried over OTN

# All PMDs of a given rate are mapped in the same way into OTN:

Candidate Locations for the OTN Reference point

### OTN Reference Point Option A

#### Pro

- Most similar to what ITU-T chose for mapping of 40GbE into OPU3 and 100GbE into OPU4 based on 802.3ba assumption that all PMDs of a given rate used exactly the same logical lane striping

- Capable of carrying end-to-end information in the alignment markers if all PMDs are striped the same

#### Con

- Even if all P802.3bs PMDs use the same logical lane striping, if all future 400GbE PMDs are not striped in the same way, requires re-striping into the canonical format before mapping into OTN

- Relies on OTN FEC for satisfactory MTTFPA

### **OTN Reference Point Option B**

#### Pro

- High certainty to be a common format regardless of whether all 400GbE PMDs (P802.3bs and future) use the same logical lane striping

- No need to convert between logical lane formats in OTN mapper/demapper

- Robust MTTFPA regardless of what ITU-T does with FEC

#### • Con

- Can't carry end-to-end information in alignment markers.

But note that there doesn't seem to be a compelling reason to support BIP inside of FEC-enabled Ethernet PMDs

- Higher bit-rate to map as 64B/66B rather than mapping the transcoded signal.

#### Straw Polls relevant to OTN support

- Straw Poll #1 I support FEC for optical PMDs

- FEC mandatory 69

- FEC optional 7

- Some PMDs may not need FEC 0

- Mandatory for some, optional for others 10

- Need more information 10

- Straw Poll #9 If all PMDs developed in P802.3bs include mandatory FEC and FEC error statistics are available, do we also require BIP?

- Y: 4; N: 24; A: 69

- Straw Poll #10 If BIP is required, should it be:

- Segment by segment (optimized for fault isolation) 2

- End to end (optimized for service assurance) 6

- Need more information 35

- Not required/don't care 33

#### Observations

- Strong majority believe that all optical PMDs developed by P802.3bs will have mandatory FEC

- Most think that if all optical PMDs have mandatory FEC, that BIP is not necessary, i.e., you get a better view of link quality from FEC corrected errors

- Note that any BIP inside of a FEC exhibits a "cliff" behavior, going from zero errors to quite a lot the instant the error ratio exceeds the correction capability of the FEC. In addition, this information is available from the FEC uncorrected codewords counter

- For those who still think there would be BIP, the number who express an opinion on how it is used (fault isolation or service assurance) is statistically insignificant

- For those who still think they need more information, please study slides 5-12 of <u>trowbridge 3bs 01 0714.pdf</u> and ask questions!

#### **OTN Reference Point Proposal**

- Propose that the OTN reference point for 400GbE is a logically serial stream of 64B/66B blocks, unstriped, without lane alignment markers (<u>Option B</u>). An implication of this choice is that there is no BIP carried end-to-end (note that a segment BIP for a particular lane striping and FEC would still be possible).

- Any idle insertion/deletion to provide room for striping overhead must occur between the CDGMII and the OTN reference point. No idle insertion/deletion should occur between the OTN reference point and the PMD. Assuming 16K frequency of lane markers (regardless of the lane count or lane rate), the effective rate of this logical interface is the nominal MAC rate x 66/64 x (1-1/16384) so that any physical instantiation has room to insert lane markers as needed without idle insert/delete elsewhere in the stack

#### Module Reuse

- Module reuse was facilitated by the fact that nothing below a CAUI chip-to-module interface cared about the or manipulated the bit values on the lanes – as long as OTN was striped into the same number of logical lanes as Ethernet, everything would work

- The following likely can be preserved: no idle insertion/deletion occurs below a CDAUI chip-to-module interface

- The following are possibly not be precluded by the 400GbE architecture:

- Logical to physical lane multiplexing in a module may be on a block or FEC symbol basis rather than a bit basis

- One (possibly Ethernet Frame Format dependent) FEC code may be replaced with another)

#### Options for Module Reuse

- Option I: Preserve the 802.3ba rule that no sublayers below a CDAUI care about bit values or manipulate the bit values on logical lanes (bit multiplexing only). Any FEC is done on the host board above a CDAUI. OTN may use a different FEC than Ethernet if it needs a stronger FEC to compensate for the higher bit-rate

- Option II (most general, described in Norfolk) encode the OTN frame as 66B blocks (all data) and use whatever striping and FEC encoding mechanisms are used for Ethernet. OTN and Ethernet use the same FEC

- Option III (potentially very complex) Allow OTN to use a different (stronger) FEC than Ethernet but do not require bit multiplexing of logical lanes. This would constrain that OTN and Ethernet choose FEC (or pairs of FECs, if not all 400GbE PMDs use the same FEC) with the same symbol size and that the marking to discover the FEC symbol alignment is common between OTN and Ethernet

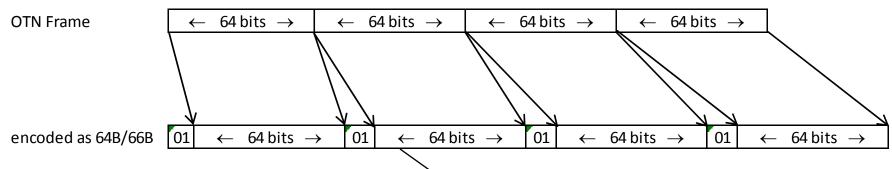

#### **Option II Amplification**

- Use the fact that the OTN reference point, as proposed, is a logically serial stream of 64B/66B blocks.

- Note that before this reference stream can be physically instantiated, it must be striped over multiple physical or logical lanes

- Maintain the principle, as in 802.3ba, that idle insertion/deletion is not done below this reference point.

#### Option II Example

Example physical instantiation could be something like gustlin 400 02a 1113.pdf, produced by transcoding 64B/66B to 256B/257B, striping first into 100G groups, striping within each 100G group into 4 logical lanes on 10-bit symbol boundaries, inserting alignment markers on each lane, and applying an RS(528,514) code based on 10-bit symbols with alignment markers appearing in the first of each of 4096 Reed Solomon code blocks (essentially 4 instances of P802.3bj 100G FEC)

#### Option II Implications for OTN

- Likely only possible if the same FEC code can be used for OTN applications as for Ethernet applications at about 6% higher bit-rate

- Would need to make OTN look like 66B blocks. Easiest way to do this and not lose any information in transcoding is to insert a "01" sync header after every 64 bits (all data)

- Since this is just part of the logical frame format, this doesn't waste as many bits as it appears. 8 sync header bits are added to every 256 data bits in the "logical" frame format, but 7 of those bits are immediately recovered in 256B/257B transcoding and reused for the FEC code. So 0.39% net is added to the OTN frame to make it look like 66B blocks, then 2.724% overhead RS FEC added

# Option II - Illustration of turning OTN frame into 64B/66B blocks

Use the Ethernet Stack to stripe and FEC encode the OTN frame when carrying over an Ethernet Module for an OTN IrDI or client interface

Could be OTN frame aligned as an OTUC4 frame without FEC is exactly 7648×64 bits, but not essential with scrambling

#### Option II: OTN Bit-rates using this scheme

| Working Assumption Bit-Rate |

|-----------------------------|

| 422.904 Gb/s                |

| 436.120 Gb/s                |

| 424.556 Gb/s                |

| 424.582 Gb/s                |

| 436.146 Gb/s                |

| 27.259 Gb/s                 |

| 412.5 Gb/s                  |

| 5.73 %                      |

|                             |

|                             |

| 100G OTN Increase in bit-rate | 8.42 % |

|-------------------------------|--------|

|-------------------------------|--------|

Smaller increase for 400G than for 100G, mainly due to RS(528,514) FEC rather than RS(255,239) FEC. Proportion remains the same even for Ethernet PMDs that use a higher overhead FEC

#### Option II – Recommended module reuse mechanism for OTN

- There is an Ethernet sublayer reference point such as the that is logically equivalent to a serial stream of 64B/66B blocks (the same as the recommended OTN reference point)

- No idle insertion/deletion occurs below the that reference point, and hence the rest of the stack can deal with a constant-bit-rate (CBR) bitstream that is effectively an infinite-length packet.

- Note that any logical to physical lane interleaving that works for Ethernet also works for OTN since they are encoded the same way

- The link parameters and FEC coding gain have sufficient margin to meet the error performance target when running at approximately 5.73% higher bit-rate than necessary for 400G Ethernet

### THANKS!

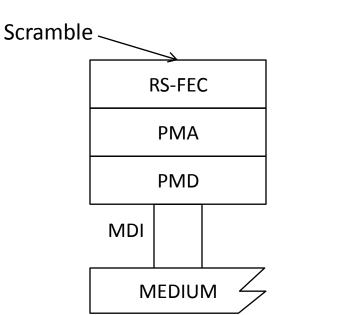

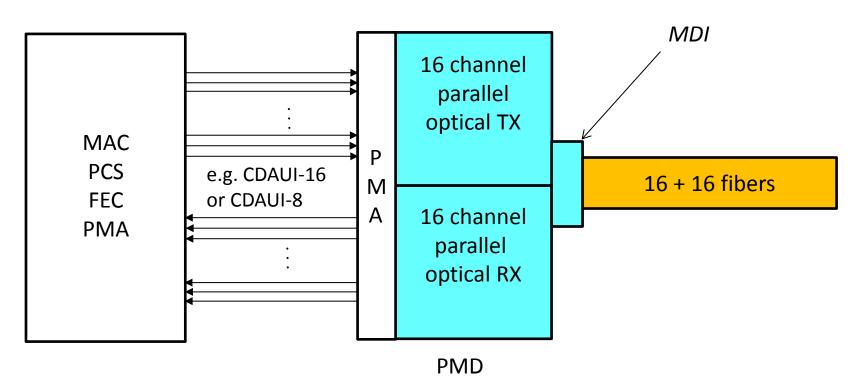

## 400 Gb/s 100 m MMF reach objective draft baseline proposal

MMF ad hoc

IEEE P802.3bs, San Antonio, TX, Nov 2014

#### Outline

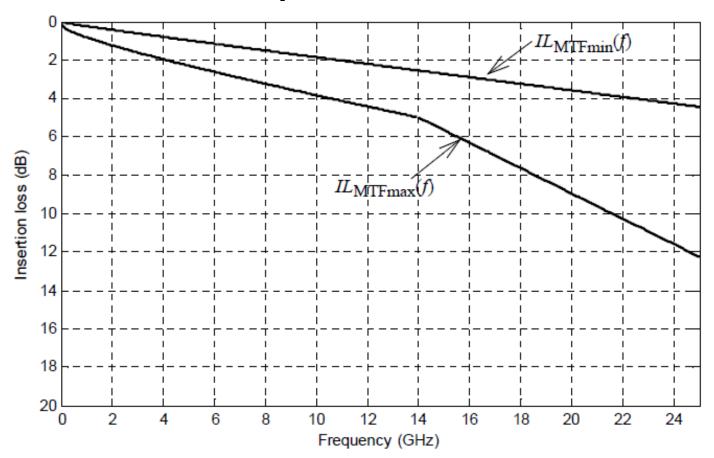

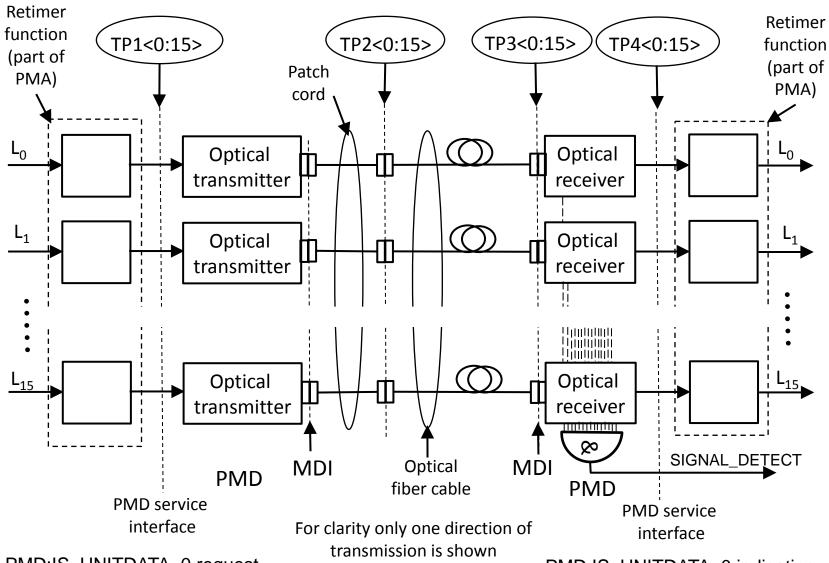

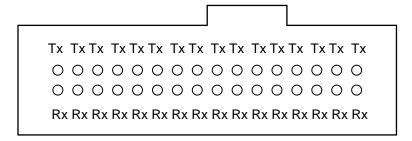

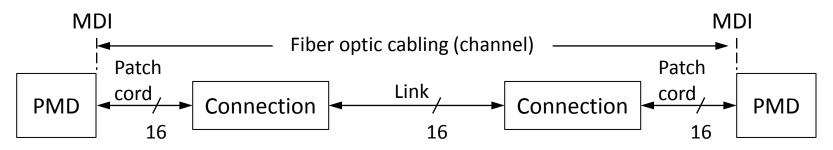

- Baseline proposal of a retimed PMD to address the 802.3bs objective to 'Provide physical layer specifications which support link distances of at least 100 m over MMF'

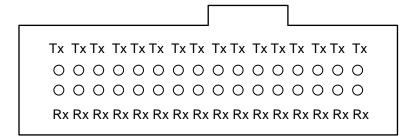

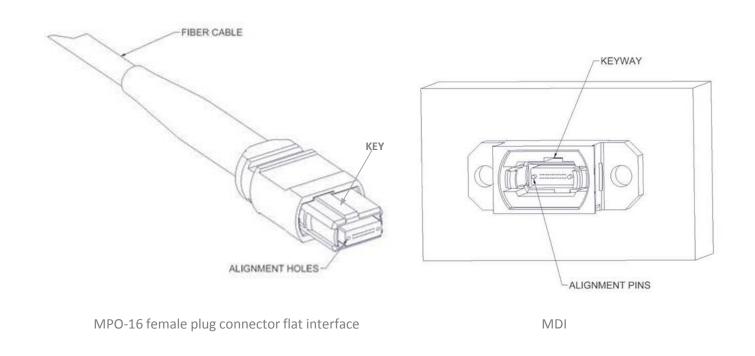

- 16 lane parallel, short wavelength based PMD for 400GBASE-SR16.

- Leveraging 100GBASE-SR4 technology, compatible with 16 x 25 Gb/s electrical interface, and breakout applications.

- Assumed use of 100GBASE-SR4 FEC, or similar strength FEC (to be defined in 802.3bs), to enable 100 m reach.

- Architecture, parameters and specifications for optical interfaces, and the proposed MDI, follow.

#### Supporters and contributors

- John Abbott, Corning

- Piers Dawe, Mellanox

- Mike Dudek, QLogic

- Ali Ghiasi, Ghiasi Quantum LLC

- Mark Gustlin, Xilinx

- Jack Jewell, Commscope

- Jonathan King, Finisar

- Scott Kipp, Brocade

- Paul Kolesar, Commscope

- Brett Lane, Panduit