#### FEC based AM unlock (Comment #67)

Pete Anslow, Ciena Mark Gustlin, Xilinx Jeff Slavick, Broadcom Phil Sun, Credo

#### **AM** unlock

For the Clause 91 and Clause 119 FEC receivers, AM lock is found according to Figure 91-8 or Figure 119-12. These state machines look for two consecutive valid alignment markers in a row.

Once AM lock is achieved, these state machines do not continue to look at the AMs, but only go out of AM lock when 3 consecutive FEC codewords are uncorrectable (Figure 91-9 and Figure 119-13).

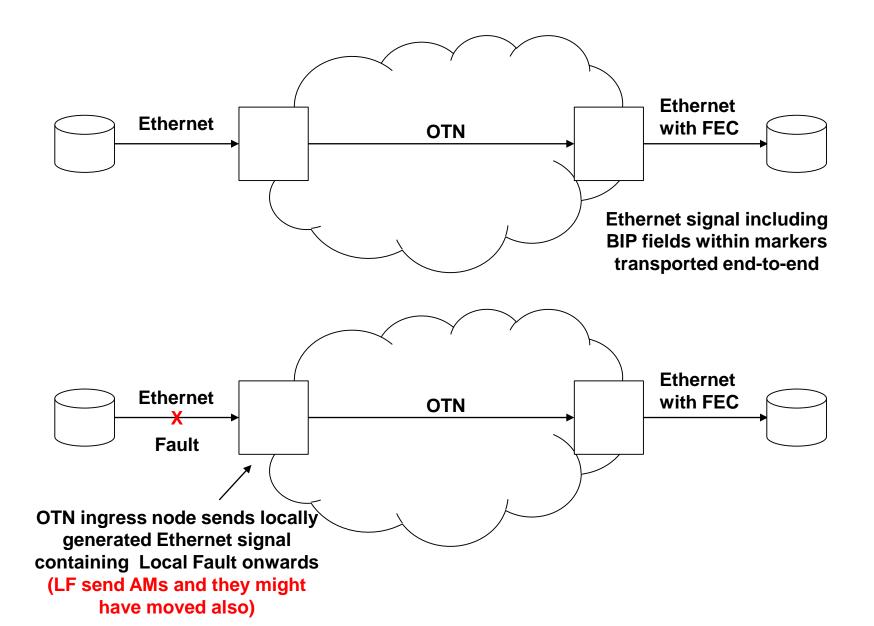

## Ethernet signal transported via OTN

### **OTN** egress node

When fault is repaired, signal here changes from Ethernet containing LF generated at ingress node to Ethernet from remote client

Position of the AMs in the two signals is different

Reed-Solomon encoder may continue to send valid codewords throughout transition

#### **Ethernet receiver**

PCS sees sync header violations from transcoder, an invalid BIP ratio of 0.996 and loses some frames, but the link stays up

Transcoder "decodes" the AM block

Reed-Solomon decoder see continuous stream of valid codewords

Alignment lock is only lost for 3 consecutive uncorrectable codewords

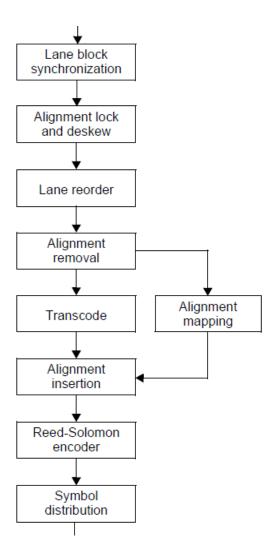

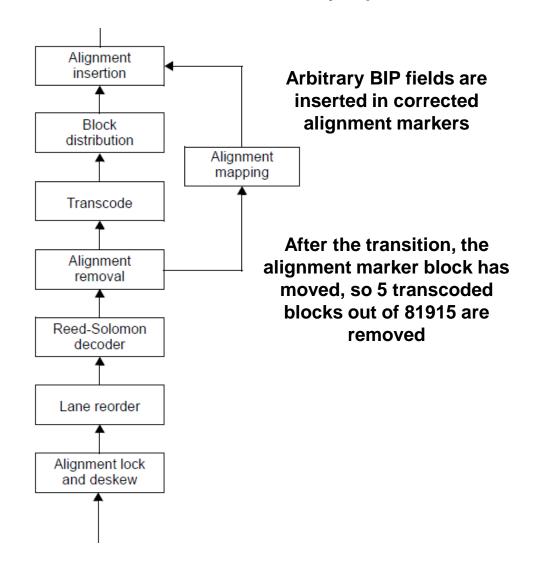

# Proposed Solution for 802.3bs

#### **Proposed Solution for 802.3bs Cont**

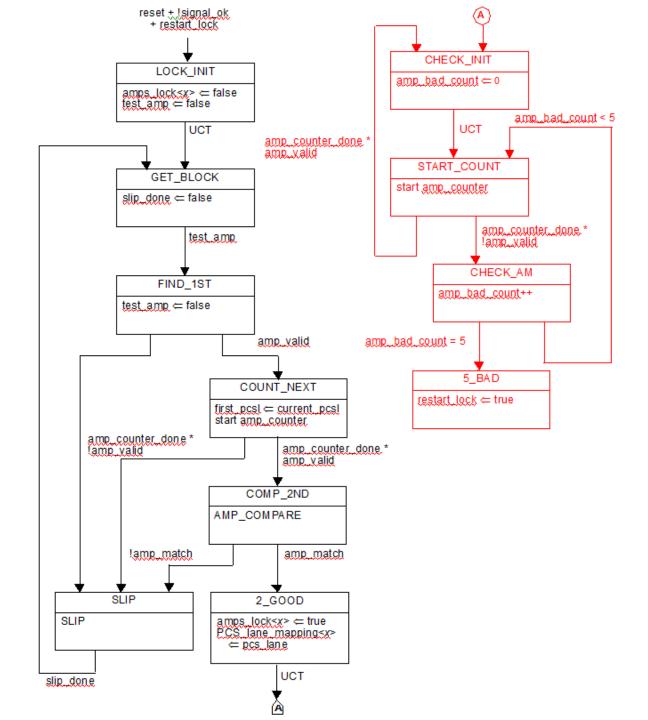

#### restart lock

Boolean variable that is set by the PCS alignment process to reset the synchronization process on all PCS lanes. It is set to true after 3 consecutive uncorrected codewords are received (3\_BAD state) or when 5 Alignment Markers in a row fail to match (5\_BAD state) and set to false upon entry into the LOSS\_OF\_ALIGNMENT state.

#### amp bad count

Counts the number of consecutive alignment markers that don't match the expected values for a given PCS lane.

#### 119.2.6.3 State diagrams

The 200GBASE-R PCS shall implement eight alignment marker lock processes and the 400GBASE-R PCS shall implement sixteen alignment marker lock processes as depicted in Figure 119–12. An alignment marker lock process operates independently on each lane. The alignment marker lock state diagram shown in Figure 119–12 determines when the PCS has obtained alignment marker lock to the received bit stream for a given lane of the service interface. Each alignment marker lock process looks for two valid alignment markers  $i \times 10$ -bit Reed-Solomon symbols apart (on a per PCS lane basis, where  $i = 139\,264$  for a 200GBASE-R PCS and  $i = 278\,528$  for a 400GBASE-R PCS) to gain alignment marker lock. Once in lock, a lane goes out of alignment marker lock only when restart lock is signaled. This occurs when the PCS synchronization process determines that three uncorrectable codewords in a row are seen, or when the alignment marker lock process sees five alignment markers in a row that fail to match the expected pattern on a given lane. When the alignment marker lock process achieves lock for a lane, and if a Clause 45 MDIO is implemented, the PCS shall record the number of the PCS lane received on that lane of the service interface in the appropriate lane mapping register (3.400 to 3.415).

## Why Look for 5 in a row?

- Wanted to reuse pre FEC AM detection logic

- Triggering after 5 mismatches in a row give you a mean time to false unlock of > AOU

| Scheme                  |       | Α                                 | В               | С               | D               | E               | F                 | G               | н                                 | 1                                   |  |

|-------------------------|-------|-----------------------------------|-----------------|-----------------|-----------------|-----------------|-------------------|-----------------|-----------------------------------|-------------------------------------|--|

| MTTFU                   | Years | 1.1e7                             | 5.2e8           | 2.0e8           | 3.2e9           | 5.8e12          | 3.5e13            | 5.5e14          | 2e16                              | 1.1e39                              |  |

|                         | AOU   | 8e-4                              | 3.8e-2          | 1.4e-2          | 2.3e-1          | 4.2e2           | 25e3              | 4.0e4           | 1.45e6                            | 8.0e28                              |  |

| Pre/Post FEC            |       | Post<br>One Lane                  | Pre<br>All Lane | Pre<br>Any Lane | Pre<br>One Lane | Pre<br>All lane | Pre<br>Any Lane   | Pre<br>One Lane | Post<br>One Lane                  | Post<br>One Lane                    |  |

| Number of AM<br>checked |       | 2                                 | 5               | 4               | 4               | 6               | 5                 | 5               | 3                                 | 2                                   |  |

| Mechanism Details       |       | No FEC<br>Decode<br>Failure check |                 |                 |                 |                 |                   |                 | No FEC<br>Decode Failure<br>check | With FEC<br>Decode Failure<br>Check |  |

| Pros                    |       |                                   |                 |                 |                 |                 |                   | Easy            |                                   |                                     |  |

| Cons                    |       |                                   |                 | One bad<br>Lane | One bad<br>Lane |                 | More counters     |                 |                                   | Works for FEC<br>Mode A only        |  |

| ← Shorter than AOU Lo   |       |                                   |                 |                 |                 |                 | Longer than AOU → |                 |                                   |                                     |  |

## Thanks!