### Improvements for Mated Test Fixture Consistency and Quality (ref: comment #92)

**Richard Mellitz, Samtec**

IEEE 802.3bs 200 Gb/s and 400 Gb/s Ethernet Task Force

IEEE P802.3 50 Gb/s, 100 Gb/s, and 200 Gb/s Ethernet Task Force

□ Vittal Balasubramanian, Dell

### TOC

- Test fixture background and specifications

- □ Test fixture considerations

- Examples of test fixture with COM and Vertical Eye Opening (VEO) results

- □ Recommendation

## **Test fixture**

#### Purpose of a well specified test fixture

- Eliminate de-embedding

- <u>Consistency</u> in measurement across the market place

- de-embedding was perceived as poor

- Time domain de-embedding was perceived as even worse

#### □ Cable test fixture (92.11.2) and Host test fixture (92.11.1.2)

- "The effects of differences between the insertion loss of an actual test fixture and the reference insertion loss are to be accounted for in the measurements."

- "Accounted for" is not well defined

#### □ Loss historically recognized as not the only indicator for test fixture performance

- The 10GBase-KR Rx testing was one of the first attempts to address this

- See Clause 69A.2.2 for  $m_{tc}$  and  $b_{tc}$  which checks that shape of the loss curve

- COM was developed as a recognition of this for 100GBase-KR4/CR4

### **Simple Test Fixture Spec?**

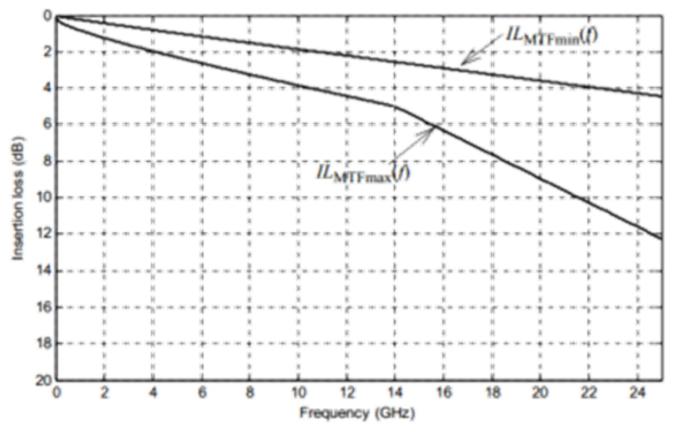

The mated test fixtures insertion loss limits are illustrated in Figure 92-19.

Figure 92–19—Mated test fixtures Insertion loss

There are also common mode and crosstalk specs but we will focus on insertion loss (IL) for now

Now for the rest of the story ...

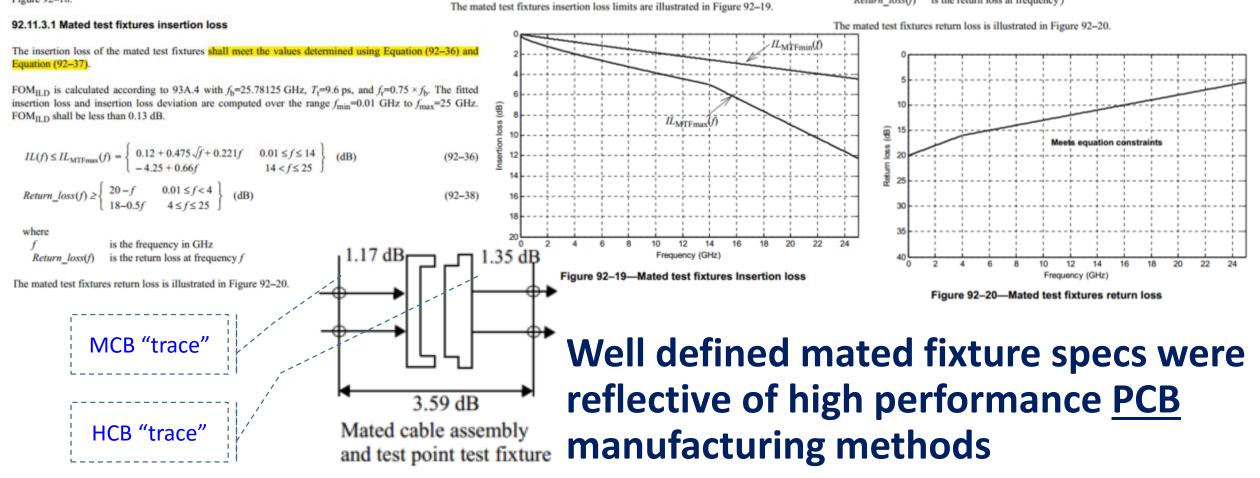

#### 92.11.3 Mated test fixtures

The test fixtures of Figure 92–15 and Figure 92–17 are specified in a mated state illustrated in Figure 92–18. The mated test fixtures specifications shall be verified in both directions indicated by the arrows illustrated in Figure 92–18 except insertion loss, which shall be verified at either test interface illustrated in Figure 92–18.

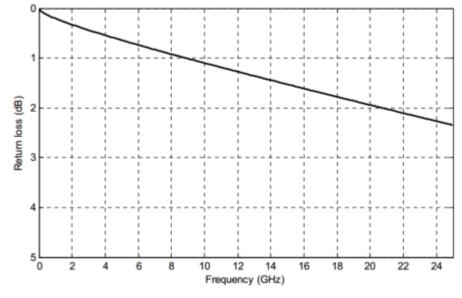

$$Return\_loss(f) \ge \begin{cases} 20 - f & 0.01 \le f < 4 \\ 18 - 0.5f & 4 \le f \le 25 \end{cases}$$

(dB)

where f is the frequency in GHz Return\_loss(f) is the return loss at frequency f

NOTE—The connector insertion loss is 1.07 dB for the mated test fixture. The host connector is allocated 0.62 dB of additional margin.

#### Figure 92A–2—35 dB channel insertion loss budget at 12.8906 GHz

IEEE P802.3 50 Gb/s, 100 Gb/s, and 200 Gb/s Ethernet Task Force

#### HCB and MCB "trace" insertion loss specs are not so testable

$IL_{tfref}(f) = -0.00144 + 0.13824\sqrt{f} + 0.06624 f$  (dB)

(92-34

for  $0.01 \le f \le 25 \text{ GHz}$

where

is the frequency in GHz

$IL_{thref}(f)$  is the reference test fixture PCB insertion loss at frequency f

The reference test fixtures PCB insertion loss is illustrated in Figure 92-16.

Figure 92–16—Reference test fixture insertion loss

#### 92.11.1.2 Test fixture insertion loss

The test fixture printed circuit board insertion loss values determined using Equation (92–34) shall be used as the reference test fixture insertion loss. The effects of differences between the insertion loss of an actual test fixture and the reference insertion loss are to be accounted for in the measurements.

#### 83E.4.1 HCB/MCB characteristics

HCB characteristics are described in 92.11.1 where the HCB performs the equivalent function as the TP2 or TP3 test fixture. The MCB characteristics are described in 92.11.2 where the MCB performs the equivalent functionality as the cable assembly test fixture.

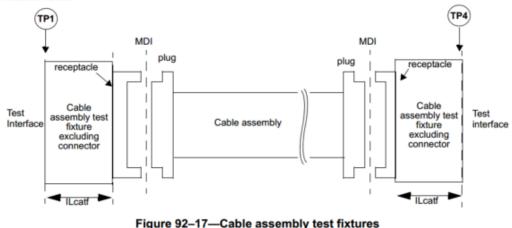

#### 92.11.2 Cable assembly test fixture

The test fixture of Figure 92–17 (also known as Module Compliance Board) or its equivalent, is required for measuring the cable assembly specifications in 92.10 at TP1 and TP4. The TP1 and TP4 test points are illustrated in Figure 92–2 and Figure 92–17. The test fixture return loss is equivalent to the test fixture return loss specified in 92.11.3.2. The test fixture printed circuit board insertion loss values determined using Equation (92–35) shall be used as the reference test fixture insertion loss. The effects of differences between the insertion loss of an actual test fixture and the reference insertion loss are to be accounted for in the measurements.

$$IL_{out}(f) = -0.00125 + 0.12\sqrt{f} + 0.0575f$$

(dB)

for 0.01 GHz  $\leq f \leq$  25 GHz

where

is the frequency in GHz

$IL_{catf}(f)$  is the reference test fixture printed circuit board insertion loss at frequency f

#### What do we have so far?

□ MCB/HCB trace insertion loss is specified

- However there are no test points to verify

- Mated fixture insertion loss is specified

- There are test points to verify

- Mated fixture specifications were based on maximum and minimum perceived manufacturing PCB technology

# **Consider this**

- □ The new value in table 120e of 30 mV for eye height is more sensitive to test fixture limitations

- A.K.A VEO, vertical eye opening

- There is precedent in the industry for using higher precision interconnect for testing

- IPC TDR specifications use a high precision rigid co-axial air dielectric transmission lines

- □ A maximum-minimum loss for mated fixture can lead to confusion

Following are a set of experiments

- They are not indented to be any specific fixture, but illustrate the mathematical variability

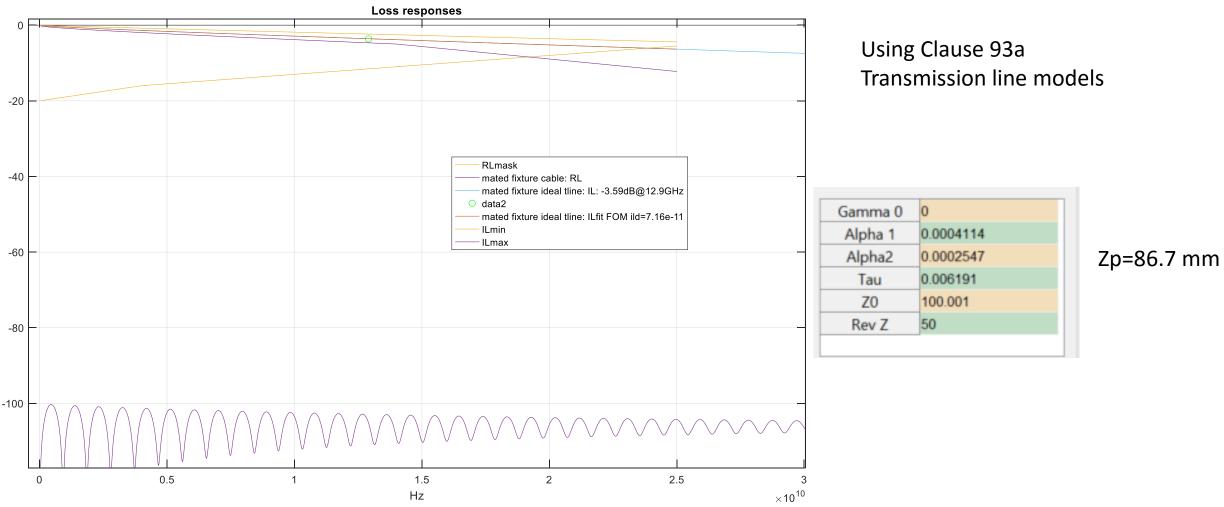

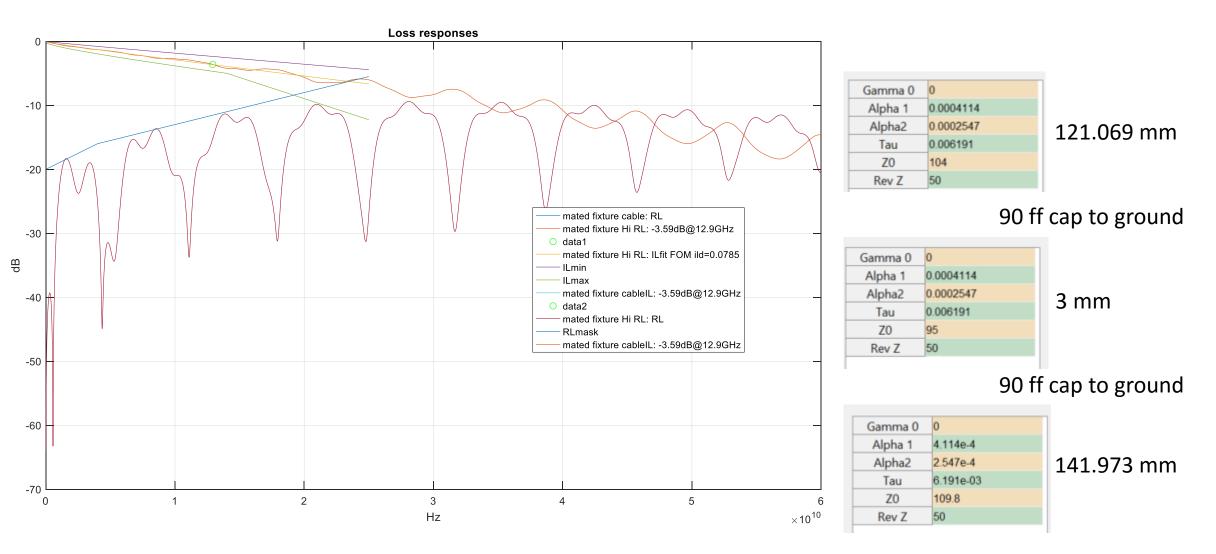

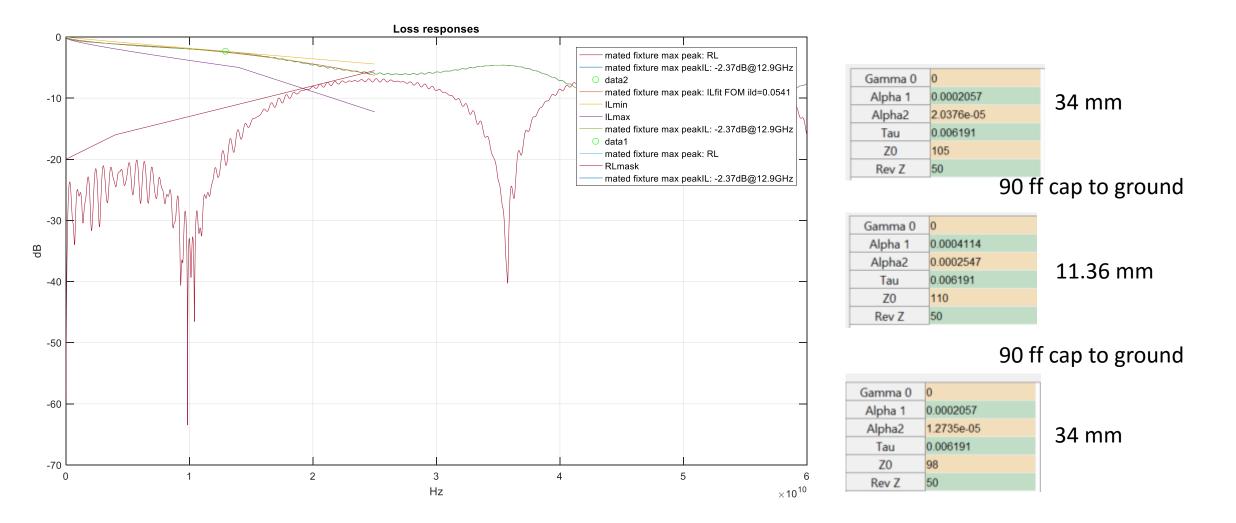

- Fixture models used are constructed of out clause 93a transmission line and component elements

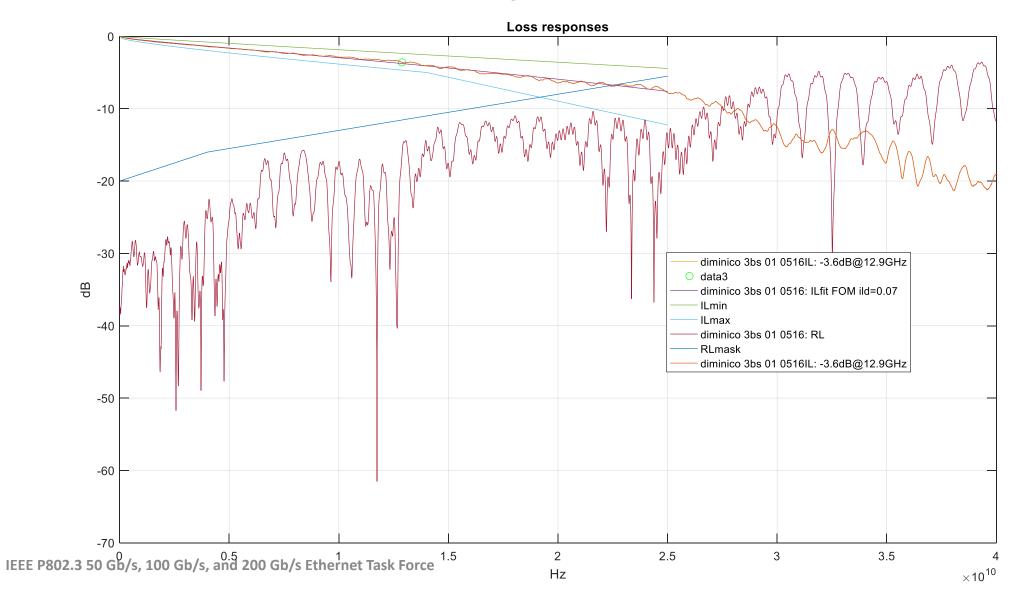

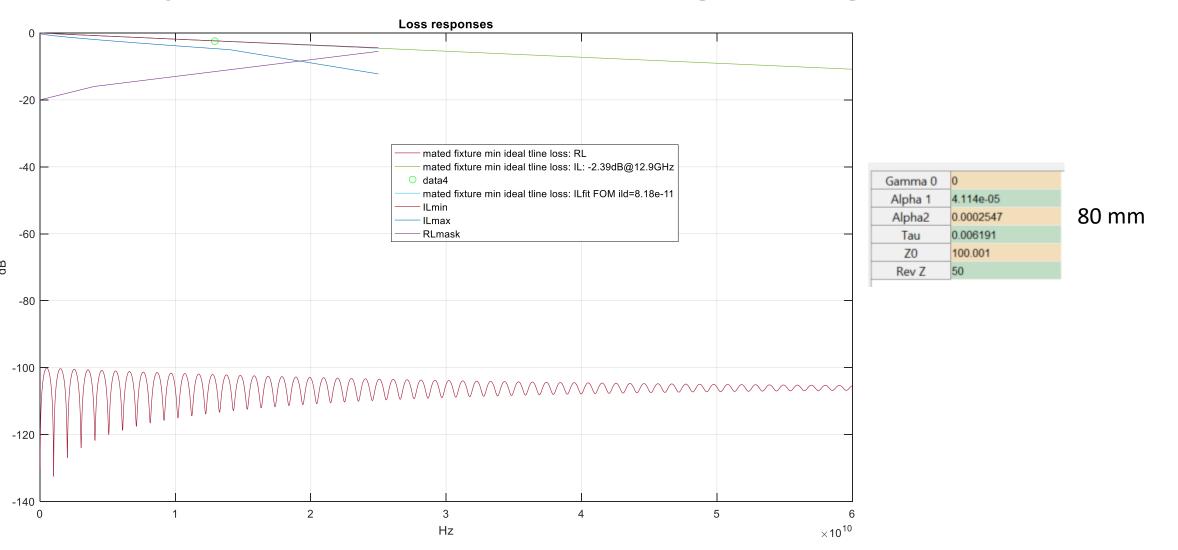

# "diminico\_3bs\_01\_0516\_c2m" is right on the reference mated fixture spec line

10

# "Ideal transmission line" mated fixture is right at 3.59 dB

#### "Max return loss mated fixture" still passes FOM\_ILD

#### "Max pulse peak mated" fixture passes FOM\_ILD too

#### "Minimum loss ideal transmission line" mated fixture may creates a maximum voltage swing

# **Simulation: Using COM Version 1.64**

- □ As in healey\_3bs\_01\_0916

- COM version 1.64 is a change from version 1.63 with the addition of a continuous time linear equalizer (CTLE) defined in IEEE P802.3bs/D2.0 120E.3.1.7

### **Results for test fixtures (all passing mated fixture specs)**

| Mated test fixtures                                | COM (dB) | VEO (mV) | Loss (dB) @ 12.89 GHz |

|----------------------------------------------------|----------|----------|-----------------------|

| diminico_3bs_01_0516_c2m [1]<br>mated test fixture | 5.1571   | 33.5641  | 3.6                   |

| Ideal transmission line mated test fixture         | 5.1206   | 34.6959  | 3.59                  |

| Max return loss mated fixture                      | 4.9469   | 30.5288  | 3.59                  |

| Max pulse peak mated fixture                       | 5.2348   | 37.1493  | 2.37                  |

| Minimum loss ideal transmission line mated fixture | 5.5293   | 44.4342  | 2.46                  |

#### [1] DiMinico, Chris, "QSFP28 MTF", IEEE P802.3bs Task Force, May 2016

## **Observations:**

- □ How is a better fixture judged?

- □ "Account for" is ill defined.

- New fixtures may use other than PCB methods (laser trimming, cabling, etc.)

- Fixture variation within specs may result in a fairly wide range of COM and VEO (voltage eye opening)

### Recommendation

- Since the intent was that fixtures should be as close a possible to the ref IL with as small as possible reflections (ILD), use COM or COM VEO (vertical eye opening) as a metric to further qualify the mated test fixture.

- A specification for a mated fixture's COM VEO to be 33 mv +/-1 mv without crosstalk considerations.