## Resolving SNDR

Richard Mellitz

**Intel Corporation**

2/01/15

#### **SNDR** is challenges for PAM4

The fitted peak voltage should divided by 3 or noise should be multiplied by 3

•

$$SNDR = \frac{Vpeak/3}{\sqrt{\sigma_e^2 + \sigma_n^2}}$$

No change in the way Vf is found or  $\sigma_e$

MENDMENT TO IEEE Std 802 3-2012: Etherne

Table 94-13-Summary of transmitter characteristics at TP0a

| Parameter                                                                                                                                                                                                                                                                                                                | Subclause<br>reference                                                                                | Value                                                                 | Units                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------|

| Signaling rate                                                                                                                                                                                                                                                                                                           | 94.3.12.2                                                                                             | 13.59375<br>± 100 ppm                                                 | GBd                  |

| Differential peak-to-peak output voltage (max.)<br>Transmitter disabled<br>Transmitter enabled                                                                                                                                                                                                                           | 94.3.12.3                                                                                             | 30<br>1200                                                            | mV<br>mV             |

| DC common-mode output voltage (max.)                                                                                                                                                                                                                                                                                     | 94.3.12.3                                                                                             | 1.9                                                                   | v                    |

| DC common-mode output voltage (min.)                                                                                                                                                                                                                                                                                     | 94.3.12.3                                                                                             | 0                                                                     | v                    |

| AC common-mode output voltage (RMS, max.)                                                                                                                                                                                                                                                                                | 94.3.12.3                                                                                             | 30                                                                    | mV                   |

| Differential output return loss (min.)                                                                                                                                                                                                                                                                                   | 94.3.12.4                                                                                             | Equation (94-7)                                                       | dB                   |

| Common-mode output return loss (min.)                                                                                                                                                                                                                                                                                    | 94.3.12.4                                                                                             | Equation (94-8)                                                       | dB                   |

| Output waveform Level separation mismatch ratio, R <sub>LM</sub> (min) Steady-state voltage by (max.) Steady-state voltage by (min.) Linear fit pulse peak (min.) Normalized coefficient step size (min.) Normalized coefficient step size (max.) Pre-cursor full-scale range (min.) Post-cursor full-scale range (min.) | 94.3.12.5.1<br>94.3.12.5.3<br>94.3.12.5.3<br>94.3.12.5.5<br>94.3.12.5.5<br>94.3.12.5.6<br>94.3.12.5.6 | 0.92<br>0.6<br>0.4<br>0.85 × v <sub>f</sub><br>0.0083<br>0.05<br>1.54 | -<br>v<br>v<br>v     |

| Output jitter and linearity Clock random jitter, RMS (max.) Clock deterministic jitter, peak-to-peak (max.) Even-odd jitter (max.) Signal-to-noise-and-distortion ratio (min.)                                                                                                                                           | 94.3.12.6.1<br>94.3.12.6.1<br>94.3.12.6.2<br>94.3.12.7                                                | 0.005<br>0.05<br>0.019<br>31                                          | UI<br>UI<br>UI<br>dB |

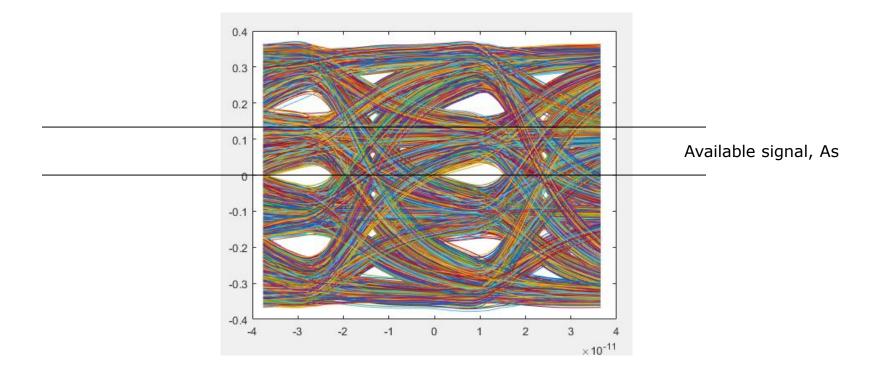

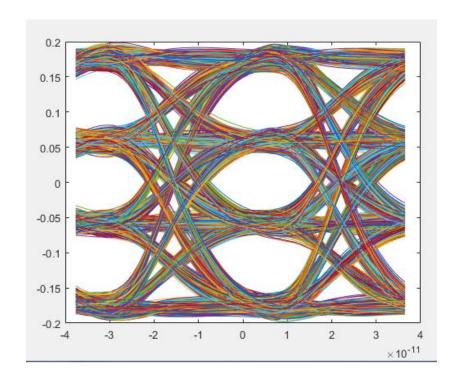

### 30 mm package

#### 30 mm package with CTLE Gdc=-6dB

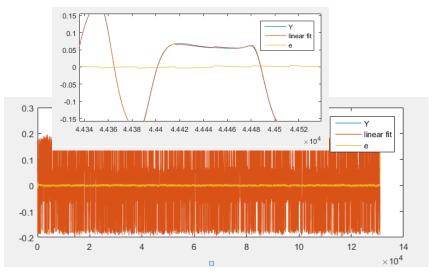

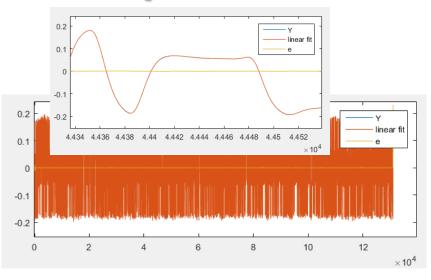

#### Measurement vs fit and error plots

Fit length: 13 UI

Fit length: 67 UI

# Suggestion to compensate for reference equalization in COM computation

- Find best Vf for any tx ffe setting

- Fit over 67 UI

- Use this setting

- Find CTLE setting which yields best SNDR using a fit over 67 UI

- vpeak/vf is loss spec

- remember these  $g_{dc1}$ ,  $\sigma_{e1}$

- Perform fit for ndfe+1+dp with CTLE using g<sub>dc1</sub>

- Determine  $\sigma_{e2}$

- $\sigma_e = \sqrt{\sigma_{e2}^2 \sigma_{e1}^2}$

- $SNDR = \frac{Vpeak/3}{\sqrt{\sigma_e^2 + \sigma_n^2}}$