## **Electrical Interface Update**

EA Meeting / Brocade Center 15 Oct 2014 Version r2

This is the personal view of Joel Goergen and not the view of IEEE P802.3bs. Joel Goergen makes no attempt to speak on behalf of the task force in any manor.

Please note the incredible work being done at this URL http://www.ieee802.org/3/bs/public/adhoc/index.shtml

## The Process Steps

The following simplified process steps are used to build consensus:

- Defining / Discussing Reach

- System Architecture

- Channel Loss

We Are Here

- Equalization

- Error Correction

- Power

## From Sept 2014 Unapproved Minutes

Motion 4 (as modified by motion #5):

Move to adopt 16 x 25Gb/s and 8 x 50Gb/s as the basis for the lane rates for any optional C2C and C2M electrical interfaces

- - M: J. Goergen

- - S: V. Parthasarathy

- - Technical (>= 75%),

- - Y:102 ,N:0 ,A:4

#### Motion #6:

Move to adopt the P802.3bm C2C and C2M specifications with current values (except that the BER requirement is TBD) as a baseline draft for the 16 x 25Gb/s electrical interfaces

- - M: J. Goergen

- - S: V. Parthasarathy

- - Technical (>= 75%),

- - Y:78 ,N:0 ,A:18

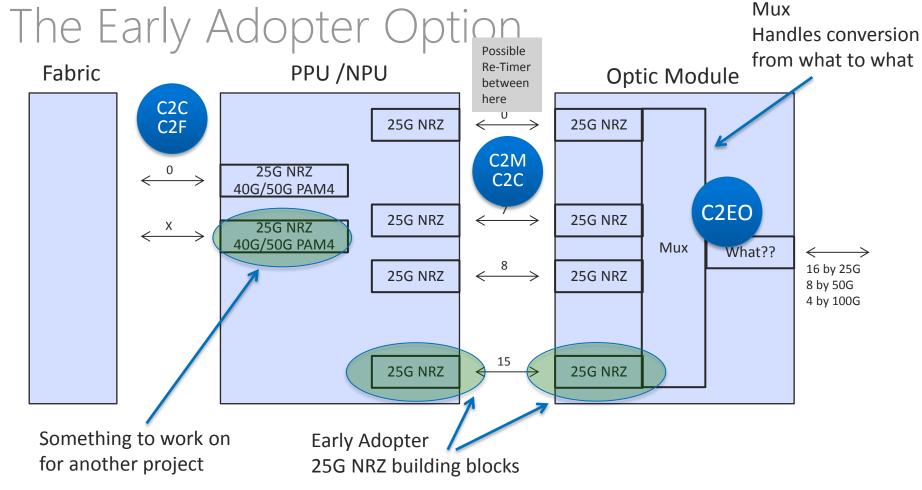

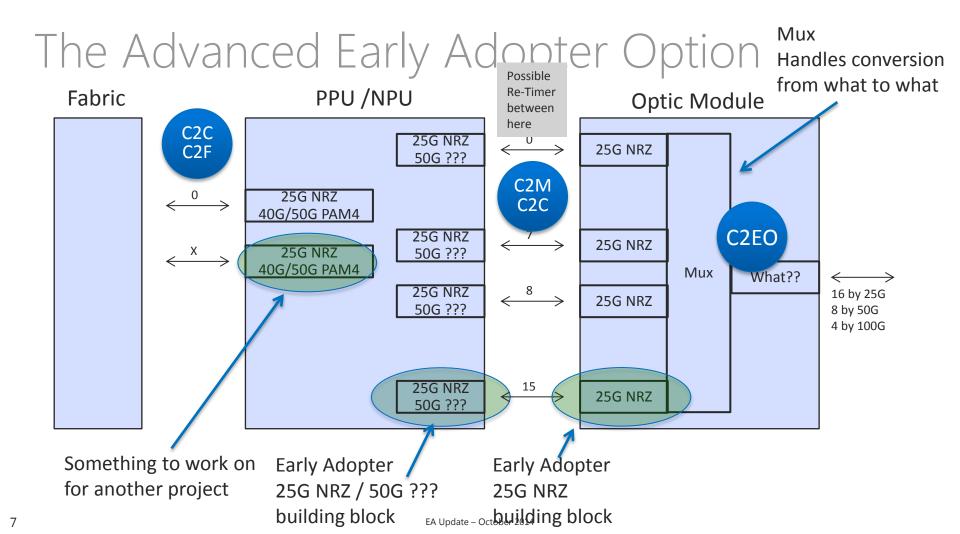

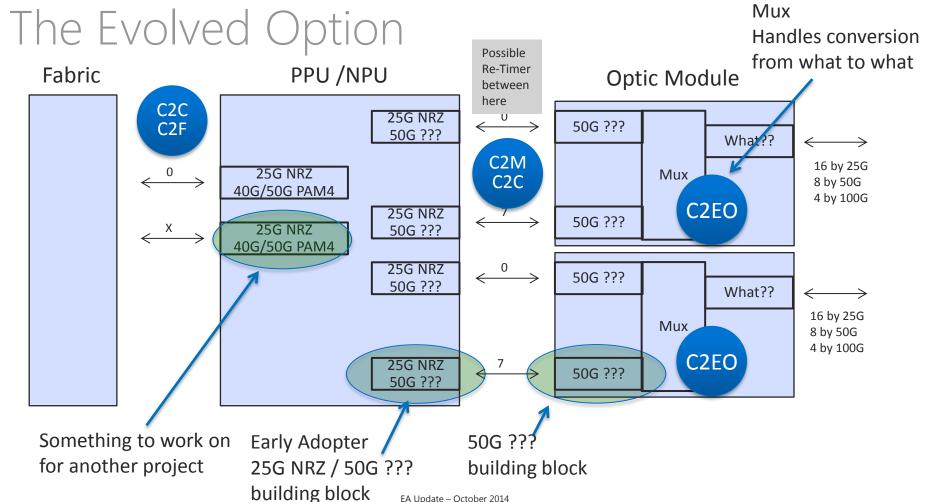

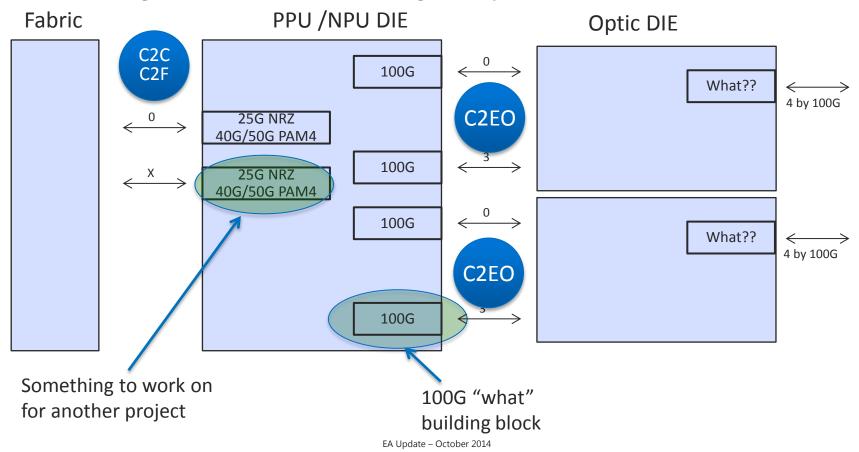

## System Architectures

System building blocks at a high level

####

### The Maybe-Some-day Option

## Reach and Modulation

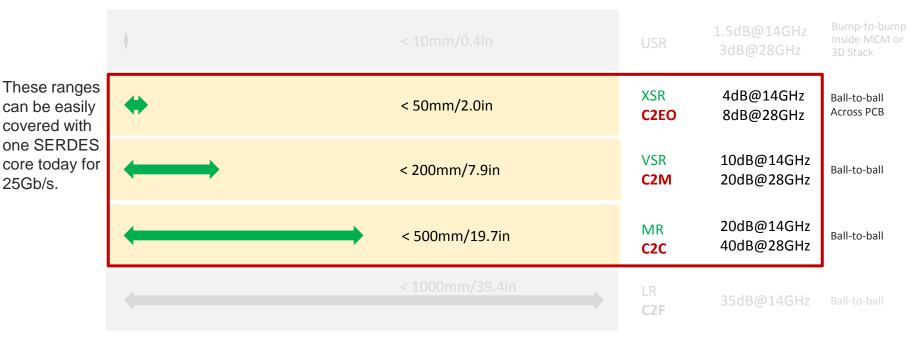

Looking at the 5 basic reach definitions talked about most How to cover reach with the best coverage of SERDES cores

#### Length, Loss & Applications

#### IL

| •        | < 10mm/0.4in    | USR         | 1.5dB@14GHz<br>3dB@28GHz | Bump-to-bump<br>Inside MCM or<br>3D Stack |

|----------|-----------------|-------------|--------------------------|-------------------------------------------|

| <b>*</b> | < 50mm/2.0in    | XSR<br>C2EO | 4dB@14GHz<br>8dB@28GHz   | Ball-to-ball<br>Across PCB                |

| ← →      | < 200mm/7.9in   | VSR<br>C2M  | 10dB@14GHz<br>20dB@28GHz | Ball-to-ball                              |

| ← →      | < 500mm/19.7in  | MR<br>C2C   | 20dB@14GHz<br>40dB@28GHz | Ball-to-ball                              |

| •        | < 1000mm/39.4in | LR<br>C2F   | 35dB@14GHz               | Ball-to-ball                              |

#### Length, Loss & Applications: Today a single 25GB/s SERDES core can cover all these ranges

IL

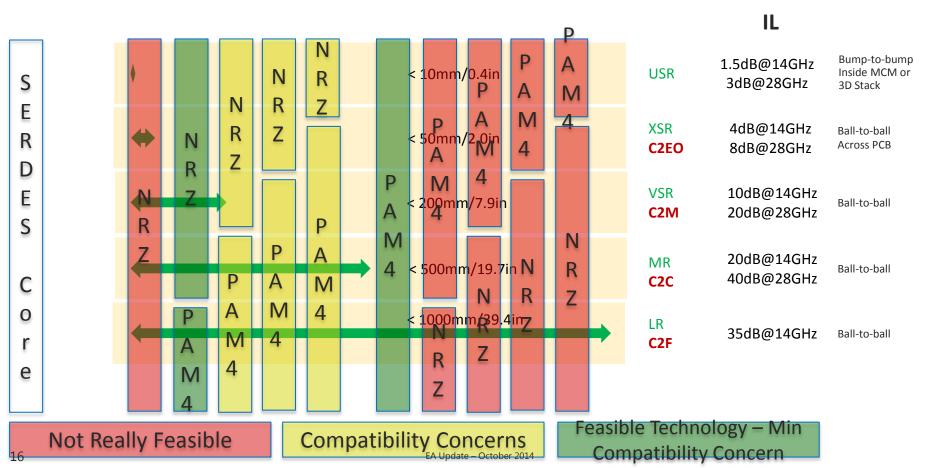

#### Length, Loss & Applications: Grouping (Perspective 1) How does a 50Gb/s SERDES core cover these ranges optimally?

|                                   | •            | < 10mm/0.4in    | USR              | 1.5dB@14GHz<br>3dB@28GHz | Bump-to-bump<br>Inside MCM or<br>3D Stack |

|-----------------------------------|--------------|-----------------|------------------|--------------------------|-------------------------------------------|

| one SERDES<br>core for<br>50Gb/s. | *            | < 50mm/2.0in    | XSR<br>C2EO      | 4dB@14GHz<br>8dB@28GHz   | Ball-to-ball<br>Across PCB                |

|                                   |              | < 200mm/7.9in   | VSR<br>C2M       | 10dB@14GHz<br>20dB@28GHz | Ball-to-ball                              |

| one SERDES<br>core for<br>50Gb/s. | $\leftarrow$ | < 500mm/19.7in  | MR<br>C2C        | 20dB@14GHz<br>40dB@28GHz | Ball-to-ball                              |

|                                   |              | < 1000mm/39.4in | LR<br><b>C2F</b> | 35dB@14GHz               | Ball-to-ball                              |

Unconfirmed but ... Under the impression from the group the cores should be compatible

#### Length, Loss & Applications: Grouping (Perspective 2) How does a 50Gb/s SERDES core cover these ranges optimally?

|                                   | •        | < 10mm/0.4in    | USR         | 1.5dB@14GHz<br>3dB@28GHz | Bump-to-bump<br>Inside MCM or<br>3D Stack |

|-----------------------------------|----------|-----------------|-------------|--------------------------|-------------------------------------------|

| one SERDES<br>core for<br>50Gb/s. | <b>*</b> | < 50mm/2.0in    | XSR<br>C2EO | 4dB@14GHz<br>8dB@28GHz   | Ball-to-ball<br>Across PCB                |

| one SERDES<br>core for<br>50Gb/s. | ← →      | < 200mm/7.9in   | VSR<br>C2M  | 10dB@14GHz<br>20dB@28GHz | Ball-to-ball                              |

|                                   |          | < 500mm/19.7in  | MR<br>C2C   | 20dB@14GHz<br>40dB@28GHz | Ball-to-ball                              |

|                                   |          | < 1000mm/39.4in | LR<br>C2F   | 35dB@14GHz               | Ball-to-ball                              |

Unconfirmed but ... Under the impression from the group the cores should be compatible

#### Length, Loss & Applications: Future: a single 50GB/s SERDES core to cover all these ranges

IL

|                                                    | •        | < 10mm/0.4in    | USR         | 1.5dB@14GHz<br>3dB@28GHz | Bump-to-bump<br>Inside MCM or<br>3D Stack |

|----------------------------------------------------|----------|-----------------|-------------|--------------------------|-------------------------------------------|

| These ranges<br>should be<br>covered with          | <b>*</b> | < 50mm/2.0in    | XSR<br>C2EO | 4dB@14GHz<br>8dB@28GHz   | Ball-to-ball<br>Across PCB                |

| one SERDES<br>core in the<br>future for<br>50Gb/s. | ← →      | < 200mm/7.9in   | VSR<br>C2M  | 10dB@14GHz<br>20dB@28GHz | Ball-to-ball                              |

| 5000/5.                                            |          | < 500mm/19.7in  | MR<br>C2C   | 20dB@14GHz<br>40dB@28GHz | Ball-to-ball                              |

|                                                    |          | < 1000mm/39.4in | LR<br>C2F   | 35dB@14GHz               | Ball-to-ball                              |

#### I think the discussion comes down to this – even though we are only focused on C2C and C2M

#### Confirming Action Item from Sept 2014 Meeting Length, Loss & Application: Technologies for 50Gb/s

These Values are under discussion

| Application      | Length        | Loss          | Modulation | pJ/bit | DFE? | FEC? |

|------------------|---------------|---------------|------------|--------|------|------|

| C2EO (XSR) < 2in | <4dB@14GHz    | PAM-4         | TBD        | TBD    | TBD  |      |

|                  | <8dB@28GHz    | NRZ           | TBD        | TBD    | TBD  |      |

|                  |               | 4-10dB@14GHz  | PAM-4      | TBD    | TBD  | TBD  |

| C2M (VSR) 2-8in  | 8-20dB@28GHz  | NRZ           | TBD        | TBD    | TBD  |      |

| C2C (MR) 8-20in  | 10-20dB@14GHz | PAM-4         | TBD        | TBD    | TBD  |      |

|                  | 8-20IN        | 20-40dB@28GHz | NRZ        | TBD    | TBD  | TBD  |

Knowing the reach definition allows us to begin understanding the next steps in the consensus building process

- System Architecture

- Channel Loss

- Modulation

- Equalization

- Error Correction

- Power

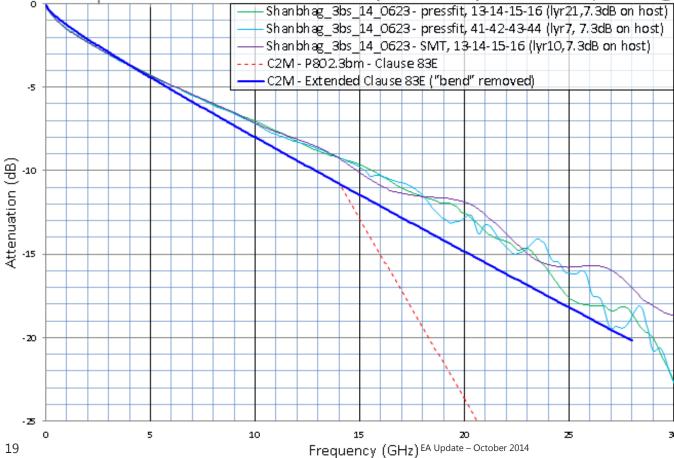

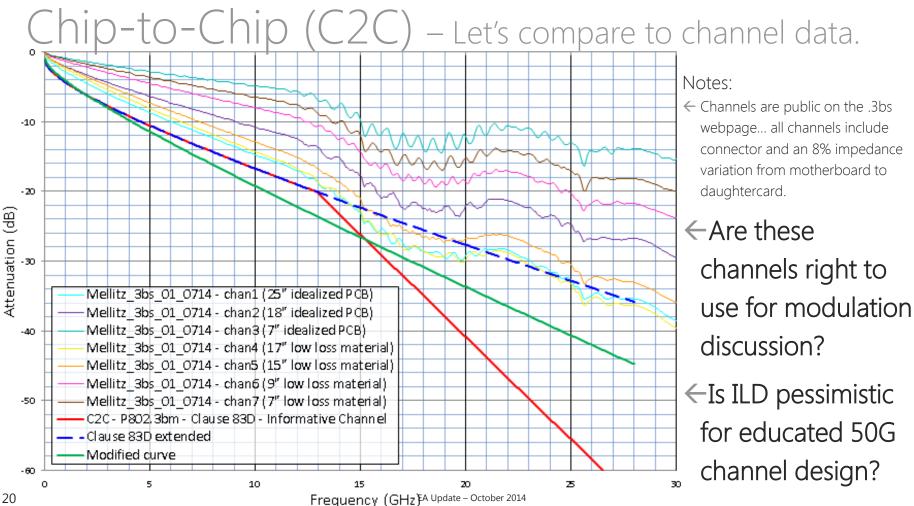

# Sandy Limit Lines

Looking at some possible limit lines to guide channel definitions for modulation simulation

### Chip-to-Module (C2M) – Comparing channel data

Notes: ← TE Channels developed using

HFSS/ADS modeling tools. ← The 4″ host trace is and should be supported at mid-loss materials by 100G standards... 7" is certainly seen in designs, but industries seem to recognize and adjust with material and design tradeoffs.

Propose: Use extended CAUI4 C2M–like channels for Modulation discussion/comparison

30

Sandy Line Equations plotted for C2C and C2M 802.3bm draft – C2M equation (red curve)  $Insertion\_loss(f) \le \left\{ \begin{array}{cc} 1.076(0.075 + 0.537\sqrt{f} + 0.566f) & 0.01 \le f < 14 \\ 1.076(-18 + 2f) & 14 \le f < 18.75 \end{array} \right\} (dB)$ (83E-1) 802.3bm draft – c2C equation (red curve) \*although, standard uses COM as the normative spec, the following is offered as the informative "limit" line  $Insertion\_loss(f) \le \left\{ \begin{array}{cc} 1.083 + 2.543 \sqrt{f} + 0.761f & 0.01 \le f < 12.89 \\ -17.851 + 2.936f & 12.89 \le f < 25.78 \end{array} \right\} (dB)$ (83D-1)

C2M and C2C "extended curve" (blue curves)

Simply extend first portion of above curves for full frequency range; omit 14-18.75G and 12.89-25.78G equations, respectively.

Suggested/modified curve drawn in C2C (green curve) 0.9 + 2.1 \sqrt{f}+1.17 f

# Next Steps

#### Next Steps to Nov 2014 Proposals

- Use the C2C and C2M channels submitted to the P802.3bs and provide a modulation scheme.

- Reach consensus on which channel groupings (LR/MR-C2C/VSR-C2M/XSR/USR) make sense from power/performance tradeoffs based on simulations

# Thank you!

From: Vasu Parthasarathy Beth Kochuparambil Vivek Telang Joel Goergen