# Analysis of: Type 3 and 4 PD Cport\_max to be supported by PSE linrush\_min IEEE802.3bt July 2015

Yair Darshan

## **Objectives**

- To investigate and propose values for Type 3, 4 PSEs and PDs:

- PD Cport\_max for Single Signature PD that need to be supported by PSE linrush min per pair set<sup>1</sup>.

- Currently it is ≤180uF for Type 1 and 2 ( 25.5W/180uF ratio )

- PSE linrush-2P min (and linrush-2P max) that is required to finish PD POWERUP within 50msec.

- Currently 0.4A min, 0.45A max per pair set.

- To clarify what is Cport per pair set for SS PD.

- To suggest Annex 33A.5 (Informative) PD Inrush and Tinrush behavior<sup>2</sup> and compliant PD model for <u>implementation independent PSE<sup>3</sup></u> compliance tests during POWER UP (or Editor Note to address it later after we agree on the details)

#### Notes:

- 1. Dual Signature Type 3 and 4 PDs can work with Cport≤180uF per pair set

- 2. I twill help PD vendors to follow spec requirements with clear PD possible physical behavior and what they need to do to complete linrush within 50msec max.

- 3. We need clear test setup that will be used to verify that PSE supports the required minimum POWER UP energy (linrush min for at least 50msec) regardless of how PSE is implementing POWER UP.

## Background and list of resources

POWERUP model is based on the principle used to derive Type 1 and Type 2 POWER UP specifications

| • | POWER UP model: | Annex A. |

|---|-----------------|----------|

|   |                 |          |

Annex B. PD Typical Block Diagram:

Clarifying definition of Cport for SS PD. Annex C1 and C2.

What affects Cport max Annex D1 and D2.

Calculating PD Cin and Cout in DC/DC converter Annex E

Calculating minimum PSE Inrush current required to charge PD effective Cport to Vport Annex F1 and F2

Analyzing SS PD Types 2,3, and 4 for Cport max to be supported by PSE Annex F3, F4 and F5.

Method for compliance PD test setup for PSE Annex G1 and G2 implementation independent POWER UP requirements

New feature for faster POWER UP, lower power loss supports all high power PD loads. Annex H

#### Research Conclusions

- a) Type-2 SS PDs require 50uF input capacitance, have an effective capacitance of 100uF and are allowed to be within 180uF without additional PD burden.

- b) Type-3 SS PDs consume 2x the power of Type-2 PDs and may require 200uF to 235uF however it is recommended that the effective capacitance will stay total 180uF seen by 4P PSE.

- c) Type-4 SS PDs consumer ~4x the power of Type-2 PDs and may require at least 400uF-440uF. However it is recommend that the effective capacitance be increased to 360uF.

- d) PSE Input inrush currents need to stay 0.4A min to 0.45A max per pair set as is in the draft currently. This will keep the same electric charge (linrush x Cport) per pair set as it was for Type 2. This arrangement easily support 360uF for Type 4 PDs without additional PSF or PD burden

- e) Type 4 SS PDs that have operating mode of 60W and below, can still use total 180uF.

- f) It is also found that it will not be possible to specify total low linrush over 4P e.g. 0.4A min and 0.9A max due to interoperability problems (PDs will not work with all PSE due to shortage in startup energy).

- q) Cport for SS PD that is seen by the PSE has the same value if PSE is connected to the PD via 2P or 4P. It means that Cport≤180uF per pair set for SS PD as currently in the spec forces 360uF at the SS PD OUTPUT Diode Bridge. However Type 3 SS PD don't need 360uF to be supported by PSE. Type 4 does.

## Interoperability Check

- Type 3 SS PD with 180uF total input cap MAY work with Type 1/2 PSEs

- They will not motor boat at POWERUP → OK

- They will motor boat at POWER ON unless PD has 15W or 25.5W total operating mode **→**OK.

- Type 4 SS PD 360uF/90W connected to Type 1 or 2 PSE.

- It will motorboat with Type 1/2 PSE during STARTUP AND at POWER ON.... → No issue.

- 90W PDs will not work anyway with Type 1 and 2 PSEs...(90W>>15, 30W).

- It is more important to meet the objective to support 90W PDs than worry about motor boating of irrelevant use cases where PD power >0 CONNECTED TO Power source with 0W capability in general. It is not our objective to create problems and solve them....

- No difference than the case if Type 2 PD connected to Type 1 PSE. It will POWER up but will not work unless designed to work in reduced power needs

- It is not market use case. It is connection error that we don't care

- If it happen, no damage. We have inherent signaling of under power condition ©

- Nobody will design 90W PD to be connected to 15W PoE.

- We can allow such behavior for Type 4 with 360uF like we allow for any load to be connected to power source with no sufficient power capability.

- If Type 4 supports 60W and lower mode, it can use 180uF and all is good.

#### Summary: PD Table 33-18 item 9 propose updates.

| Item | Parameter               | Symbol | Unit | Min             | Max <sup>3</sup> | PD Type | Additional Information               |

|------|-------------------------|--------|------|-----------------|------------------|---------|--------------------------------------|

| 9    | Pair set capacitance    |        |      | 5 <sup>1</sup>  | 180              | 1, 2    | See 33.3.7.6, 33.3.7.3.              |

| 9a   | during MDI_POWER states | CPort  | uF   |                 |                  |         | See 33.3.7.3 for requirements when   |

|      |                         |        |      |                 |                  |         | Cport>Cport_max.                     |

|      |                         |        |      | 10 <sup>1</sup> | 180              | 3       | See 33.3.7.6, 33.3.7.3.              |

|      |                         |        |      |                 |                  |         | See 33.3.7.3 for requirements when   |

| 9b   |                         |        |      |                 |                  |         | Cport>Cport_max                      |

|      |                         |        |      | 10 <sup>1</sup> | 180              | 4       | For Type 4 power level 60W or lower. |

|      |                         |        |      |                 |                  |         | See 33.3.7.6, 33.3.7.3.              |

|      |                         |        |      |                 |                  |         | See 33.3.7.3 for requirements when   |

|      |                         |        |      |                 |                  |         | Cport>Cport_max                      |

| 9b   |                         |        |      | 201             | 360              | 42      | For Type 4 class 7 and 8.            |

|      |                         |        |      |                 |                  |         | See 33.3.7.6, 33.3.7.3.              |

|      |                         |        |      |                 |                  |         | See 33.3.7.3 for requirements when   |

|      |                         |        |      |                 |                  |         | Cport>Cport_max                      |

[Editor Notes (to be removed prior publication) The below concept is covered by the above baseline text table and by the text in 33.3.7.3)]

- 1. Cport min values are not part of this discussions and are presented here for whole topic clarity. See separate presentation on this topic.

- 2. Type 4 90W PD doesn't have to successfully POWER UP with PSE Type 1. 90W>15W so it will not work anyway in POWER ON. As a result it is not relevant if Type 4 PD with 360uF is connected to Type 1 PSE and fail startup. This is irrelevant use case.

- 2.1 IF PD Type 4 designed to work at Type 3 power level only, then it can use up to 180uF

- 3. Cport max is the Cport maximum value that will be supported by PSE linrush. If Cport>Cport max PD will limit linrush per 33.3.7.3

## **Updating 33.3.7.3**

#### **Existing Text:**

#### 33.3.7.3 lines 39 - 47 as follows:

Input inrush current at startup is limited by the PSE if CPort per pair set < 180 µF, as specified in Table 33– 11. If CPort per pair set ≥180 µF, input inrush current shall be limited by the PD so that Ilnrush PD per pair set max is satisfied.

#### Insert a note at the end of section 33.3.7.3 as follows:

NOTE— Cport per pair set is the Cport seen by an attached PSE on two twisted pairs

#### **Change to:**

#### Modify 33.3.7.3 lines 39 – 47 as follows:

Input inrush current at startup is limited by the PSE if CPort per pair set < Cport max 180 µF, as specified in Table 33–11. If CPort per pair set ≥ Cport  $\max \frac{180 \, \mu F}{}$ , input inrush current shall be limited by the PD so that Ilnrush PD per pair set max is satisfied.

Note: Cport max is the border line when PSE is responsible to limit linrush-2P per pair set or it is PD reasonability. There is no defined limit for Cport max if PD is limiting linrush-2P per pair set per the requirements of Table 33-18.

#### Insert a note at the end of section 33.3.7.3 as follows:

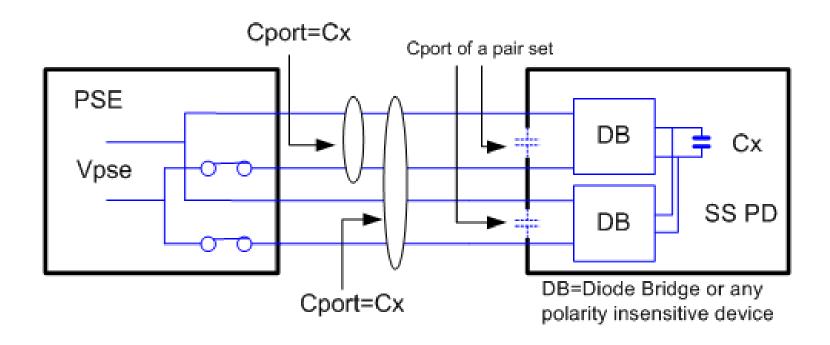

NOTE—Cport per pair set is the Cport seen by an attached PSE on two twisted pairs

NOTE: Cport in Table 33-18 is the total PD input capacitance during POWERUP and

POWER ON states that any PSE sees when connected to any single signature PD over a pair set or both pair sets.

When PSE is connected to Dual Signature PDs, Cport value requirements are specified in 33.2.7.6.

See PSE-PD simplified Cport interpretation drawing model in Annex C2.

## **Discussion**

## Thank You

Additional Information are presented in the Annexes next

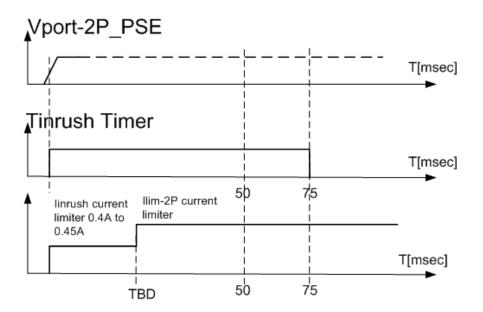

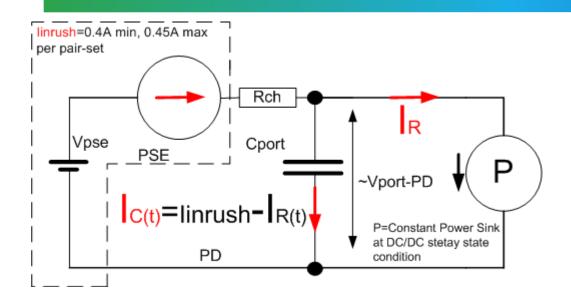

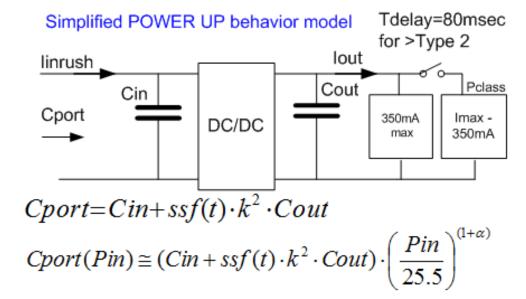

#### Annex A: System POWER UP Model

- PSE guarantees linrush min over each pair set.

- PD has to finish PD inrush within 50msec max. Regardless of:

- I<sub>R(t)</sub> value (350mA max) during linrush period Cport(t) profile.  $-I_R(t)$  and Cport(t) are time depended. When PWM starts operation, secondary capacitive loads WHEN connected the DC/DC output are reflected to the PD input.

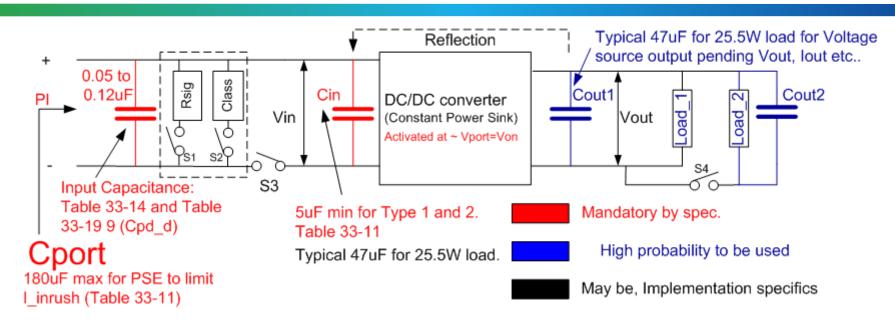

### Annex B: PD Typical Block Diagram (Type 1 and 2)

- There is mandatory minimum capacitance for a compliant PD (=5.05uF).

- When PSE is tested for compliance, it must contain minimum capacitance requirement.

- Cport is defined for the sum of all capacitive components at PD input AND all the reflected PD DC/DC output capacitors (Cout1, Cout2 etc.)

- Type 2 maximum TOTAL equivalent Input capacitance that PSE has to support with linrush min is 180uF. It includes Cin+Cpd\_d+ Reflected Cout1 etc.

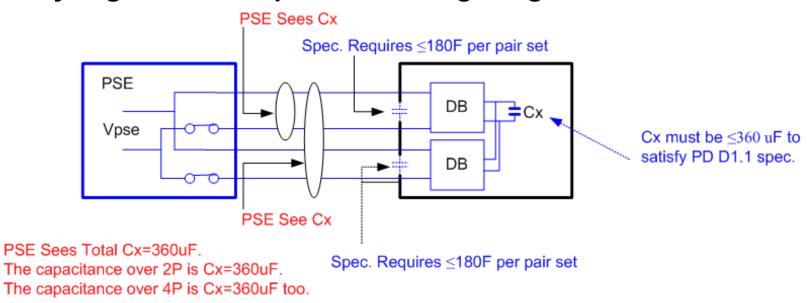

## Annex C1: Cport interpretation problem with SS PD PER D1.1 SPEC.

- Current spec requires PSE to support ≤180uF per pair-set which is total sum of ≤ 360uF for Type 3 and 4.

- Analyzing how it is implement in Single Signature PD......

- The problem is:

- Type 4 PD requires 360uF/90W to be supported by PSE.

- PSE don't see 180uF per pair set. It will see 360uF. Text need to be modified.

- No interoperability issue for Type 4 PD connected to Type 1 PSE. See interoperability slide.

## Annex C2: Cport proposed definition for SS PD.

- This is clear definition for Cport when SS PD is used.

- Cx is the same regardless if it is 2P or 4P operation as physically seen by PSE.

## Annex D1: What affects Cport max

- ssf(t)=soft start function time delay affects Vou/Vin value over time.

- k=Vout/Vin ratio

- Pin/25.5 is the power increased related to Type 2 power as reference.

- $\alpha$  <1 is representing a power conversion topology factor. A also depends on Pin.

- If we want to Increasing Pin[W] and keep the same \$/W as Type 2 and Type 2 design and performance of:

- Meeting linrush time =50msec max AND

- Using same ssf(t) timing AND

- Keeping the same heat dissipation on Cin and Cout AND

- Keep the voltage and current transient performance of Type 2 AND

- Then Cin and Cout must increased AND total linrush min must be increased to support it.

#### Annex D2: PD Cport possible variations during POWERUP time duration

$$Cport(t) \cong 0.05uF + Cin + u(t - \tau 1) \cdot Cout_1 \left(\frac{Vout(t)}{Vin(t)}\right)^2 + u(t - \tau 2) \cdot Cout_2 \left(\frac{Vout(t)}{Vin(t)}\right)^2 \dots$$

$$0.05uF + Cin + (Cout_1 + Cout_2) \cdot \left(\frac{Vout(t)}{Vin(t)}\right)^2 - \frac{Cport[uF]}{Vin(t)}$$

$$Cin + Cout_1 \left(\frac{Vout}{Vin}\right)^2 - \frac{Cport[uF]}{Vin(t)}$$

$$Cin = 5.05 \text{ to } 47.05$$

$$0.05 - \frac{Cport[uF]}{Vin(t)}$$

$$Cin = 5.05 \text{ to } 47.05$$

$$Cin = 5.05 \text{ to } 47.05$$

#### Behavioral qualitative description of PD input capacitance over time.

Notes:

- 1. t1,t2,t3 and t4 are implementation specifics.

- 2. Slopes of capacitance change is function of DC/DC transfer function and soft start.

- Regardless of actual Coort profile (implementation specifics), PD must get to steady state (Vport-PD dv/dt  $\rightarrow \varepsilon$ , practical  $\varepsilon \simeq 0.01$ ) within 50msec.

- Only PD physics affect the completion of PD Inrush.

- PSE Tinrush timer has no effect on the completion of PD inrush time.

#### Annex E: Calculating PD Cin and Cout in DC/DC converter

- Pin=PD DC/DC input power

- Pout=DC/DC output power

- dVpp is the ripple peak to peak required.

- Iinrush-2P PSE=PSE guaranteed minimum inrush current

- Iload=PD load input current limited to 350mA during PD POWERUP phase.

- Vin=PD DC/DC input voltage

- Fs=DC/DC switching frequency

- Lm=DC/DC primary side magnetizing inductance of inductor or transformer or coupled inductor.

- Ls=DC/DC secondary side magnetizing inductance of inductor or transformer or coupled inductor.

- Ktop= Topology factor i.e. buck, Boost Flyback etc. It is not given here. Assume K=1 for this discussion.

- The following are practical approximations for Flyback topology with sufficient accuracy for this discussion.

- Cin is approximated by  $Cin \cong k_{top} \cdot \left( \frac{Pin}{Vin \cdot Fs} + \frac{Vin \cdot D^2}{Lm \cdot Fs^2} \right) \cdot \frac{1}{dv}$

- Cout is approximated by  $Cout \cong k_{top} \cdot \left( \frac{Pout}{Vout \cdot Fs} + \frac{Vin \cdot (1-D)^2}{I.s \cdot Fs^2} \right) \cdot \frac{1}{dv}$

- Reflected Cout to the Input, Cinref is approximated (Vout/Vin)^2 and is started to be reflected to the input upon PWM controller starting point which is PD input voltage dependent and soft start i.e. time dependent as well.

- Total PD port maximum capacitance is Cin+ Cinref.

#### Annex F1: Calculating minimum PSE Inrush current required to **charge PD effective Cport to Vport**

IR start time is undefined in the current standard, it is assumed that IR(t) starts to reduce Inrush to (Inrush min-IR(t)) at t=0 although typically IR(t) will start to affect only when PWM starts at Von and with additional delay of the soft start mechanism. (At low value of Cport, soft start must be short and we will reach Von very quickly so it is fare working assumption)

$$\begin{split} I_{charge} \cdot Tinrush &= Q_{TOTAL} = \sum_{i=1}^{n} C_{i} \cdot \Delta Vi \\ \left( Iinrush_{\min} - I_{R_{i}} \right) \cdot Tinrush &= Q_{TOTAL} = \sum_{i=1}^{n} C_{i} \cdot \Delta Vi \\ Iinrush_{\min} &= I_{R_{i}} + \frac{\sum_{i=1}^{n} C_{i} \cdot \Delta Vi}{Tinrush} \end{split}$$

See Annex F2 for calculated examples

#### **Annex F2: Calculating minimum PSE Inrush current required to charge** PD effective Cport to Vport within 50msec.

| #  | PD Type | linrush_mi<br>n[A] | Vpse<br>[V] | Rch_max<br>[Ω] | Vpd_max[V]           | Pin<br>[W] | Iload<br>[A] | Cport<br>[uF] | Notes                     |  |

|----|---------|--------------------|-------------|----------------|----------------------|------------|--------------|---------------|---------------------------|--|

|    |         | Eq-1               |             |                | =Vpse -Rch*Ppse/Vpse |            |              | Annex<br>A    |                           |  |

|    |         |                    |             |                |                      |            |              |               | Typical DC/DC input total |  |

|    |         |                    |             |                |                      |            |              |               | Cin+Cinref                |  |

| 1  | 2       | 0.432              | 50          | 12.5           | 42.50                | 25.5       | 0.35         | 97            | minimum requirement       |  |

| 2  | 2       | 0.503              | 50          | 12.5           | 42.50                | 25.5       | 0.35         | 180           |                           |  |

| 3  | 2       | 0.523              | 55          | 12.5           | 48.18                | 25.5       | 0.35         | 180           |                           |  |

| 4  | 2       | 0.532              | 57          | 12.5           | 50.42                | 25.5       | 0.35         | 180           | Spec. Requirement         |  |

| 5  | 3       | 0.532              | 50          | 6.25           | 42.50                | 51         | 0.35         | 214*          | Typical DC/DC input total |  |

| 6  | 3       | 0.556              | 55          | 6.25           | 48.18                | 51         | 0.35         | 214*          | Cin+Cinref                |  |

| 7  | 3       | 0.566              | 57          | 6.25           | 50.42                | 51         | 0.35         | 214*          | minimum requirement       |  |

| 8  | 3       | 0.584              | 50          | 0.1            | 49.88                | 60         | 0.35         | 235*          | Typical DC/DC input total |  |

| 9  | 3       | 0.608              | 55          | 0.1            | 54.89                | 60         | 0.35         |               | Cin+Cinref                |  |

| 10 | 3       | 0.617              | 57          | 0.1            | 56.89                | 60         | 0.35         | 235*          | minimum requirement       |  |

| 11 | 4       | 0.597              | 50          | 6.25           | 42.50                | 71         | 0.35         | 290*          | Typical DC/DC input total |  |

| 12 | 4       | 0.629              | 55          | 6.25           | 48.18                | 71         | 0.35         | 290*          | Cin+Cinref                |  |

| 13 | 4       | 0.642              | 57          | 6.25           | 50.42                | 71         | 0.35         | 290*          | minimum requirement       |  |

| 14 | 4       | 0.679              | 52          | 6.25           | 41.18                | 90         | 0.35         | 400           | Typical DC/DC input total |  |

| 15 | 4       | 0.708              | 55          | 6.25           | 44.77                | 90         | 0.35         | 400           | Cin+Cinref                |  |

| 16 | 4       | 0.765              | 57          | 6.25           | 47.13                | 90         | 0.35         | 440           | minimum requirement       |  |

| 17 | 4       | 0.806              | 52          | 0.1            | 51.81                | 100        | 0.35         | 440           | Typical DC/DC input total |  |

| 18 | 4       | 0.832              | 55          | 0.1            | 54.82                | 100        | 0.35         | 440           | Cin+Cinref                |  |

| 19 | 4       | 0.850              | 57          | 0.1            | 56.82                | 100        | 0.35         | 440           | minimum requirement       |  |

Calculated for 1Vpp ripple criteria

## Annex F3: Analyzing Type 2 PD

- Cport is 180uF

- PD Tinrush=Cport\*Vin/Icharge≤50mSec may be hard to meet at worst case conditions. (Tinrush=180uF\*57V/(0.4A-0.35A)=205msec >> 50msec max.

- As a result PD designer had to optimize between all the following parameters:

- Cport < 180uF or</li>

- Design to operate at steady state at 30V to 42V or

- Not consuming 350mA during full PD Inrush time by using longer SSF time delay or

- Switch on other capacitive loads much after PDPOWER UP period or

- All combinations of the above means.

- As a result typical Type 2 PDs were used ~100uF total Cport or lower to meet the 50msec max PD linrush time.

- It was also sufficient from power level considerations as described in What affects Cport max slide for cost effective power conversion topologies.

## Annex F4: Analyzing Type 3 Single Signature PD

- Type 3 is 2x25.5W hence need ~2x the capacitance ~ 200uF

- Worst case calculation results with 200uF to 235uF for 51W PDs and 60W (Extended power). See calculations in Annex A2-1, A2-2

- In order to meet same Type 2 constrains, we need to:

- Increase linrush min from 0.4A to ~0.8A.

- **Conclusions:**

- linrush min total for Type 3: 0.8A min.

- linrush min per pair set=0.4A (maximum 0.45A).

- Cport for Type 3 SS PD=180uF max in order to be supported by PSE

## Annex F5: Analyzing Type 3 Single Signature PD

- Type 4 is ~4X Type 2 Power hence needs 400uF to 440uF for 71W PDs and 90W (Extended power).

- We can reduce it to 360uF if and only if linrus\_min total =0.8A min.

- (Allows some flexibility)

- See calculations in Annex A2-1, A2-2.

- **Conclusions:**

- linrush min for Type 4: 0.8A min.

- linrush min per pair set=0.4A (maximum 0.45A).

- Cport for Type 4 SS PD=360uF max in order to be supported by PSE.

#### **Annex G1** method for compliance PD test setup for PSE implementation independent POWER UP requirements

Worst case calculation for linrus from Annex F:

$$Iinrush_{\min} = I_{Ri} + \frac{\sum_{i=1}^{n} C_i \cdot \Delta Vi}{50m \sec}$$

- Ci are the capacitors value at the PD input including capacitors that are in the output and are reflected to the input during PD startup time duration.

- IR is limited to 350mA

- The above means that for Type 1 and 2 the maximum available startup charge is:

$$(0.4A - 0.35A) \cdot 50m \sec = \sum_{i=1}^{n} C_i \cdot \Delta Vi = 0.0025Coulomb$$

which limits possible  $\sum_{i=1}^{n} C_i \cdot \Delta Vi = Cport \cdot Vport \_PD$  operating combinations for the PD designer.

This conclusion sets the way for compliance PD test setup for checking if PSE meets its POWERUP requirements regardless the method it is using to support POWERUP.

See Annex C for compliant PD test setup for testing PSE POWERUP linrus and Tinrush requirements.

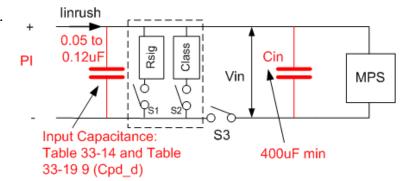

### Annex G2: compliant PD test setup for testing PSE POWERUP linrush and Tinrush requirements

- PSE has to supply startup energy for the worst case conditions.

- The PD test setup will contain big capacitor at its input so Inrush can be monitored for at least 50msec. Compliant PD test set up

- Worst case STARTUP energy is given by:

- 0.5\*Vpse max\*Iinrush max\*Tinrush min=0.5\*C\*Vpse max^2. Resulting with linrush max\*Tinrush min=C\*Vpse max

- Cin min in the test setup is: linrush max\*Tinrush min/Vpse max=0.45\*0.05/57=394uF.

- Use 400uF min and measure Iport that is within linrush min/max range for at least 50ms.

- Advantages:

- Implementation independent if PSE uses Tinrush timer or legacy POWERUP to determine PD ended linrush process.

- Simple proof that PSE delivers linrush min for at least 50msec.

- Real compliant PD with capacitive load.

- Uses only the correct stress on PSE circuitry compared to uncompliant PD test setups that is using constant current source of >450mA which represent short circuit condition (twice the energy) and not POWERUP which is half the energy as calculated above.

- The above is for each pair set. As a result, Type 1, 2, 3 and 4 can be tested with 400uF min at each pair set of the PD test setup.

#### Annex H: New feature for faster POWER UP, higher probability for successful startup, supports all high power PD loads

- Supporting High PD Cport to meet maximum 50msec PD linrush time can be implemented without additional burden on PSE or PD by the following new optional feature:

- Alow higher Inrush max per pair set i.e. >450mA after TBD time from PSE POWER UP and before Tinrush min.

- Benefits:

- a)Reducing dynamic stress on the MOSFET during POWER UP

- b)Reach faster startup with lower probability for startup oscillations

- c) Handle different load behavior during startup that is time dependent.