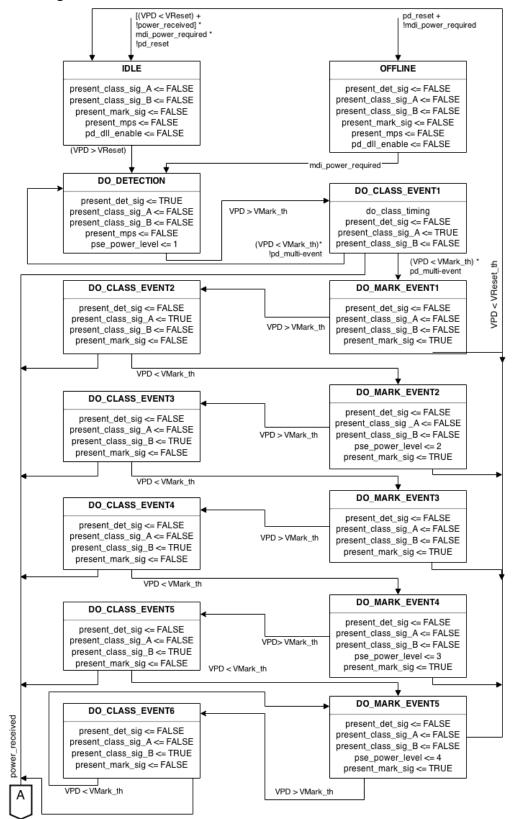

# 33.3.3 PD state diagram

The PD state diagram specifies the externally observable behavior of a PD. The PD shall provide the behavior of the state diagram shown in Figure 33–16.

### 33.3.3.1 Conventions

The notation used in the state diagram follows the conventions of state diagrams as described in 21.5.

# 33.3.3.2 Constants

The PD state diagram uses the following constants:

V<sub>Reset\_th</sub>

Reset voltage threshold (see Table 33–17)

$V_{Mark\_th}$

Mark event voltage threshold (see Table 33–17)

class\_sig

PD classification, one of either 0, 1, 2, 3, or 4 (see Table 33–16)

## 33.3.3.3 Variables

The PD state diagram uses the following variables:

| mdi_power_rec  | juired                                                                                             |                                                                                 |  |  |  |  |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| A contro       | ol variable                                                                                        | indicating the PD is enabled and should request power from the PSE by           |  |  |  |  |  |  |  |

|                |                                                                                                    | ction signature to the link, and when the PSE sources power to apply the MPS to |  |  |  |  |  |  |  |

| keep the       | keep the PSE sourcing power. A variable that is set in an implementation-dependent manner. Values: |                                                                                 |  |  |  |  |  |  |  |

|                | FALSE:                                                                                             | PD functionality is disabled.                                                   |  |  |  |  |  |  |  |

|                | TRUE:                                                                                              | PD functionality is enabled.                                                    |  |  |  |  |  |  |  |

| pd_multi-event |                                                                                                    |                                                                                 |  |  |  |  |  |  |  |

| A contro       | ol variable i                                                                                      | indicating whether the PD presents a Mulitple-Event class signature.            |  |  |  |  |  |  |  |

| Values:        | FALSE:                                                                                             | PD does not present a Multiple-Event class signature.                           |  |  |  |  |  |  |  |

|                | TRUE:                                                                                              | PD does present a Mulitple-Event class signature.                               |  |  |  |  |  |  |  |

| pd_dll_capable |                                                                                                    |                                                                                 |  |  |  |  |  |  |  |

| This var       | iable indica                                                                                       | ates whether the PD implements Data Link Layer classification.                  |  |  |  |  |  |  |  |

| Values:        | FALSE:                                                                                             | The PD does not implement Data Link Layer classification.                       |  |  |  |  |  |  |  |

|                | TRUE:                                                                                              | The PD does implement Data Link Layer classification.                           |  |  |  |  |  |  |  |

| pd_dll_enabled |                                                                                                    |                                                                                 |  |  |  |  |  |  |  |

| A variab       | le indicatir                                                                                       | ng whether the Data Link Layer classification mechanism is enabled.             |  |  |  |  |  |  |  |

| Values:        | FALSE:                                                                                             | Data Link Layer classification is not enabled.                                  |  |  |  |  |  |  |  |

|                | TRUE:                                                                                              | Data Link Layer classification is enabled.                                      |  |  |  |  |  |  |  |

| pd_max_power   |                                                                                                    |                                                                                 |  |  |  |  |  |  |  |

|                |                                                                                                    | indicating the max power that the PD may draw from the PSE. See power           |  |  |  |  |  |  |  |

| classific      | ations in Ta                                                                                       | able 33–18.                                                                     |  |  |  |  |  |  |  |

| Values:        | 0:                                                                                                 | PD may draw Class 0 power                                                       |  |  |  |  |  |  |  |

|                | 1:                                                                                                 | PD may draw Class 1 power                                                       |  |  |  |  |  |  |  |

|                | 2:                                                                                                 | PD may draw Class 2 power                                                       |  |  |  |  |  |  |  |

|                | 3:                                                                                                 | PD may draw Class 3 power                                                       |  |  |  |  |  |  |  |

|                | 4:                                                                                                 | PD may draw Class 4 power                                                       |  |  |  |  |  |  |  |

|                | 5:                                                                                                 | PD may draw Class 5 power                                                       |  |  |  |  |  |  |  |

|                | 6:                                                                                                 | PD may draw Class 6 power                                                       |  |  |  |  |  |  |  |

|                | 7:                                                                                                 | PD may draw Class 7 power                                                       |  |  |  |  |  |  |  |

|                   | <u>8:</u>                | PD may draw Class 8 power                                                                        |

|-------------------|--------------------------|--------------------------------------------------------------------------------------------------|

| pd_reset          |                          |                                                                                                  |

| An impl<br>OFFLIN |                          | -specific control variable that unconditionally resets the PD state diagram to the               |

| Values:           | FALSE:                   | The device has not been reset (default).                                                         |

|                   | TRUE:                    | The device has been reset.                                                                       |

| power_received    |                          |                                                                                                  |

| An indic          |                          | the circuitry that power is present on the PD's PI.                                              |

| Values:           | FALSE:                   | The input voltage does not meet the requirements of V <sub>Port_PD</sub> in Table 33–18.         |

|                   | TRUE:                    | The input voltage meets the requirements of V <sub>Port PD</sub> .                               |

| present_class_s   | sig_A                    | _                                                                                                |

|                   |                          | g the classification signature that is used during the first two class events(see 33.3.5) by the |

| Values:           | FALSE:                   | The PD classification signature is not to be applied to the link.                                |

|                   | TRUE:                    | The PD classification signature is to be applied to the link.                                    |

| present_class_s   | sig_B                    |                                                                                                  |

|                   | presenting<br>by the PD. | g the classification signature during the 3rd class event and all subsequent class events (see   |

| Values:           | FALSE:                   | The PD classification signature is not to be applied to the link.                                |

|                   | TRUE:                    | The PD classification signature is to be applied to the link.                                    |

| present_det_sig   | 5                        |                                                                                                  |

| Controls          | presenting               | g the detection signature (see 33.3.4) by the PD.                                                |

| Values:           |                          | A non-valid PD detection signature is to be applied to the link.                                 |

|                   | TRUE:                    | A valid PD detection signature is to be applied to the link.                                     |

| present_mark_s    | sig                      |                                                                                                  |

| Controls          |                          | g the mark event current and impedance (see 33.3.5.2.1) by the PD.                               |

| Values:           | FALSE:                   | The PD does not present mark event behavior.                                                     |

|                   | TRUE:                    | The PD does present mark event behavior.                                                         |

| present_mps       |                          |                                                                                                  |

|                   |                          | MPS (see 33.3.8) to the PD's PI.                                                                 |

| Values:           | FALSE:                   | The Maintain Power Signature (MPS) is not to be applied to the PD's PI.                          |

|                   | TRUE:                    | The MPS is to be applied to the PD's PI.                                                         |

| pse_dll_power_    |                          |                                                                                                  |

|                   |                          | output by the PD power control state diagram (Figure 33–28) that indicates the type              |

|                   | -                        | PD is being powered.                                                                             |

| Values:           |                          | The PSE is a Type 1 PSE (default).                                                               |

|                   | 2:                       | The PSE is a Type 2 PSE.                                                                         |

|                   | 3:                       | The PSE is a Type 3 PSE.                                                                         |

|                   | 4:                       | The PSE is a Type 4 PSE.                                                                         |

| pse_power_lev     |                          |                                                                                                  |

|                   |                          | that indicates to the PD the level of power the PSE is supplying.                                |

| Values:           | 1:                       | The PSE is delivering the PD's requested power or 15.4W, whichever is less.                      |

|                   | 2:                       | The PSE is delivering the PD's requested power or 30W, whichever is less.                        |

|                   | 3:                       | The PSE is delivering the PD's requested power or 60W, whichever is less.                        |

|                   | 4:                       | The PSE is delivering the PD's requested power or 90W (TBD), whichever is less.                  |

| V                 |                          |                                                                                                  |

| V <sub>PD</sub>   |                          | Les defined in 1.4                                                                               |

| voitage a         | u the PD P               | I as defined in 1.4.                                                                             |

# 33.3.3.4 Timers

All timers operate in the manner described in 14.2.3.2 with the following addition. A timer is reset and stops

counting upon entering a state where "stop x\_timer" is asserted.

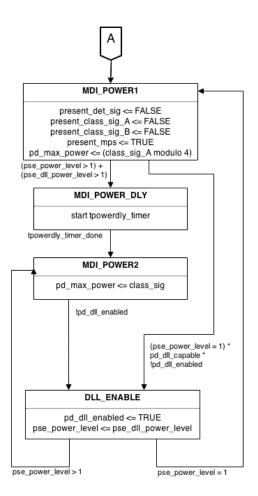

# tpowerdly\_timer

A timer used to prevent the Type 2 PD from drawing more than inrush current during the PSE's inrush period; see  $T_{delay}$  in Table 33–18.

### 33.3.3.5 Functions

#### do\_class\_timing

This function is used by a Type 3 or Type 4 PD to evaluate the type of PSE connected to the link by measuring the length of the classification event. The classification event timing requirements are defined in Table 33-10. This function returns the following variable:

Type\_3\_MPS: A control variable that indicates to the PD the Type of PSE to which it is connected. This variable is used to indicate which MPS timing requirements (see 33.3.8). the PD should use. Values: TRUE: The PSE uses Type 3 MPS requirements.

FALSE: The PSE uses Type 1 MPS requirements.

#### 33.3.3.6 State diagrams

Figure 33–16—PD state diagram

Figure 33–16—PD state diagram (continued)

NOTE 1—DO\_CLASS\_EVENT6 creates a defined behavior for a Type 2, Type 3, or Type 4 PD that is brought into the classification range repeatedly.

NOTE 2—In general, there is no requirement for a PD to respond with a valid classification signature for any DO\_CLASS\_EVENT duration less than  $T_{class}$ .

#### 33.3.5 PD classifications

See 33.2.6 for a general description of classification mechanisms.

A PD may be classified by the PSE based on the Physical Layer classification information, Data Link Layer classification, or a combination of both provided by the PD. The intent of PD classification is to provide information about the maximum power required by the PD during operation. Additionally, classification is used to establish mutual identification between Type 2, Type 3, and Type 4 PSEs and Type 2, Type 3, and Type 4 PDs.

The method of classification depends on the type of the PD and the type of the attached PSE. A PD

shall meet at least one of the allowable classification permutations listed in Table 33-8. A Type 1

PD may implement any of the class signatures in 33.3.5 and 33.6.

Type 2, Type 3, and Type 4 PDs implement both Multiple-Event class signature (see 33.3.5.2) and Data Link

Layer classification (see33.6).

PD classification behavior conforms to the state diagram in Figure 33-16.

### 33.3.5.1 PD 1-Event class signature

Class 0 is the default for PDs. However, to improve power management at the PSE, a Type 1 PD may opt to provide a signature for Class 1 to 3.

The PD is classified based on power. The Physical Layer classification of the PD is the maximum power that the PD draws across all input voltages and operational modes.

PDs implementing a Mulitple-Event class signature shall return Class 4 in accordance with the maximum power draw,  $P_{Class\_PD}$ , as specified in Table 33–18. Since 1-Event classification is a subset of Multiple-Event classification, Type 2, Type 3, and Type 4 PDs respond to 1-Event classification with a Class 4 signature. Type 1 PDs may choose to implement a Multiple-Event class signature and return Class 0, 1, 2, or 3 in accordance with the maximum power draw,  $P_{Class\_PD}$ . Type 2, Type 3, and Type 4 PD's classification behavior shall conform to the electrical specifications defined by Table 33–17.

In addition to a valid detection signature, PDs shall provide the characteristics of a classification signature as specified in Table 33–16. Type 1 and Type 2 PDs shall present one, and only one, classification signature during classification.

| Parameter                     | Conditions       | Minimum | Maximum | Unit |

|-------------------------------|------------------|---------|---------|------|

| Current for Class Signature 0 | 14.5 V to 20.5 V | 0       | 4.00    | mA   |

| Current for Class Signature 1 | 14.5 V to 20.5 V | 9.00    | 12.0    | mA   |

| Current for Class Signature 2 | 14.5 V to 20.5 V | 17.0    | 20.0    | mA   |

| Current for Class Signature 3 | 14.5 V to 20.5 V | 26.0    | 30.0    | mA   |

| Current for Class Signature 4 | 14.5 V to 20.5 V | 36.0    | 44.0    | mA   |

# Table 33–16—Classification signature<sup>1</sup>, measured at PD input connector

# 33.3.5.2 PD Multiple-Event class signature

PDs implementing Multiple-Event Physical Layer classification shall present class\_sig\_A during CLASS\_EV1 and CLASS\_EV2 and class\_sig\_B during CLASS\_EV3, CLASS\_EV4, CLASS\_EV5, and CLASS\_EV6. The PD's classification behavior shall conform to the electrical specifications defined by Table 33–17.

| PD Type | Class    | class_sig_A | class_sig_B |

|---------|----------|-------------|-------------|

|         | 0        | 0           | 0           |

| 1       | 1        | 1           | 1           |

|         | 2        | 2           | 2           |

|         | 3        | 3           | 3           |

| 2       | 4        | 4           | 4           |

|         | 1        | 1           | 1           |

|         | 2        | 2           | 2           |

| 3       | 3        | 3           | 3           |

|         | 4        | 4           | 4           |

|         | 5        | 4           | <u>0</u> 1  |

|         | 6        | 4           | <u>1</u> 2  |

| 4       | 7        | 4           | <u>2</u> 3  |

|         | <u>8</u> | <u>4</u>    | <u>3</u>    |

# Table 33–TBDA1—Multiple-Event Physical Layer Classification Responses

\*NOTE: See Table 33-16 for definitions of class signatures 1-4.

Until successful Multipile-Event Physical Layer classification or Data Link Layer classification has completed, a Type 2, Type 3, or Type 4 PD's pse\_power\_level state variable is set to '1.' A Type 2, Type 3, or Type 4 PD shall conform to the electrical requirements as defined by Table 33–18 for the level defined in its pse\_power\_level state variable.

| Item | Parameter                      | Symbol                | Units | Min   | Max  | Additional information |

|------|--------------------------------|-----------------------|-------|-------|------|------------------------|

| 1    | Class event voltage            | V <sub>Class</sub>    | V     | 14.5  | 20.5 |                        |

| 2    | Mark event voltage             | V <sub>Mark</sub>     | V     | 6.90  | 10.1 |                        |

| 3    | Mark event current             | I <sub>Mark</sub>     | mA    | 0.250 | 4.00 | See 33.3.5.2.1         |

| 4    | Mark event threshold           | V <sub>Mark_th</sub>  | V     | 10.1  | 14.5 | See 33.3.5.2.1         |

| 5    | Classification reset threshold | V <sub>Reset_th</sub> | V     | 2.81  | 6.90 | See 33.3.5.2.1         |

| 6    | Classification reset voltage   | V <sub>Reset</sub>    | V     | 0     | 2.81 | See 33.3.5.2.1         |

Table 33–17—Multiple-Event Physical Layer classification electrical requirements

#### 33.3.5.2.1 Mark Event behavior

When the PD is presenting a mark event signature as shown in the state diagram of Figure 33–16, the PD shall draw  $I_{Mark}$  as defined in Table 33–17 and present a non-valid detection signature as defined in Table 33–15.

The PD shall not exceed the  $I_{Mark}$  current limits when voltage at the PI enters the  $V_{Mark}$  specification as defined in Table 33–17.

V<sub>Mark\_th</sub> is the PI voltage threshold at which the PD implementing Multiple-Event class signature transitions into and out of the DO\_CLASS\_EVENT1, DO\_CLASS\_EVENT2, DO\_CLASS\_EVENT3, DO\_CLASS\_EVENT4, or DO\_CLASS\_EVENT5 states as shown in Figure 33–16.

The PD shall draw  $I_{Mark}$  until the PD transitions from a DO\_MARK\_EVENT state to the IDLE state.  $V_{Reset\_th}$  is the PI voltage threshold at which the PD implementing Multiple-Event class signature transitions from a DO\_MARK\_EVENT state to the IDLE state as shown in Figure 33–16.

#### 33.3.6 PSE Type identification

A Type 2 PD shall identify the PSE Type as either Type 1 or Type 2 (see Figure 33–16). A Type 3 PD shall identify the PSE Type as either Type 1, Type 2, or Type 3. A Type 4 PD shall identify the PSE Type as either Type 1, Type 2, or Type 4.

The default value of pse\_power\_level is 1. After a successful Multiple-Event Physical Layer classification or DataLink Layer classification has completed, the pse\_power\_level is set to either 2, 3 or, 4.

The PD resets the pse\_power\_level to '1' when the PD enters the DO\_DETECTION state.

# 33.3.7 PD power

The power supply of the PD shall operate within the characteristics in Table 33–18.

The PD may be capable of drawing power from a local power source. When a local power source is provided, the PD may draw some, none, or all of its power from the PI.

| Item | Parameter                                    | Symbol                 | Unit | Min   | Max                         | PD<br>Type | Additional information                        |

|------|----------------------------------------------|------------------------|------|-------|-----------------------------|------------|-----------------------------------------------|

| 1    | Input voltage                                | V                      | v    | 37.0  | 57.0                        | 1          | See 33.3.7.1,<br>Table 33–1                   |

| 1    |                                              | V <sub>Port_PD</sub>   | v    | 42.5  | 57.0                        | 2          |                                               |

| 2    | Transient operating input voltage            | V <sub>Tran_lo</sub>   | v    | 36.0  |                             | 2          | For time dura-<br>tion defined in<br>33.2.7.2 |

| 3    | Input voltage range during                   | V <sub>Overload</sub>  | v    | 36.0  | 57.0                        | 1          | See 33.3.7.4,                                 |

| 5    | overload                                     | • Overload             | •    | 41.4  | 57.0                        | 2          | Table 33–1                                    |

|      | Input average power,<br>Class 0 and Class 3  | _                      |      |       | 13.0                        | 1, 3       |                                               |

|      | Input average power,<br>Class 1              |                        |      |       | 3.84                        | 1, 3       |                                               |

|      | Input average power,<br>Class 2              | P <sub>Class_PD</sub>  | w    |       | 6.49                        | 1, 3       | See 33.3.7.2,<br>Table 33–1                   |

| 4    | Input average power,<br>Class 4              |                        |      |       | 25.5                        | 2, 3       |                                               |

| 4    | Input average power,<br>Class 5              |                        |      |       | TBD                         | 3          |                                               |

|      | Input average power,<br>Class 6              |                        |      |       | TBD                         | 3          |                                               |

|      | Input average power,<br>Class 7              |                        |      |       | TBD                         | 4          |                                               |

|      | Input average power,<br>Class 8              |                        |      |       | <u>TBD</u>                  | <u>4</u>   |                                               |

| 5    | Input inrush current                         | I <sub>Inrush_PD</sub> | А    |       | 0.400                       | 1, 2       | Peak value—<br>See 33.3.7.3                   |

| 6    | Inrush to operating state delay              | T <sub>delay</sub>     | S    | 0.080 |                             | 2          | See 33.3.7.3                                  |

|      | Peak operating power,<br>Class 0 and Class 3 |                        |      |       | 14.4                        | 1, 3       | See 33.3.7.4                                  |

|      | Peak operating power,<br>Class 1             | _ P <sub>Peak_PD</sub> | PD W |       | 5.00                        | 1, 3       |                                               |

| 7    | Peak operating power,<br>Class 2             |                        |      |       | 8.36                        | 1, 3       |                                               |

|      | Peak operating power,<br>Class 4             |                        |      |       | $1.11 \times P_{Class\_PD}$ | 2, 3       |                                               |

|      | Peak operating power,<br>Class 5             |                        |      |       | TBD                         | 3          |                                               |

| Table 33–18—PD p | ower supply limits |

|------------------|--------------------|

|------------------|--------------------|

|   | Peak operating power,<br>Class 6            |                   |           |      | TBD  | 3        |                        |

|---|---------------------------------------------|-------------------|-----------|------|------|----------|------------------------|

|   | Peak operating power,<br>Class 7            |                   |           |      | TBD  | 4        |                        |

|   | Peak operating power,<br>Class 8            |                   |           |      | TBD  | <u>4</u> |                        |

| 8 | Input current transient<br>(absolute value) |                   | mA/<br>μs |      | 4.70 | 1,2      | See 33.3.7.5           |

| 9 | PI capacitance during MDI_POWER states      | C <sub>Port</sub> | μF        | 5.00 |      | 1, 2     | See 33.3.7.6, 33.3.7.3 |

Table 33–18—PD power supply limits (continued)

| Item | Parameter                               | Symbol             | Unit            | Min  | Max   | PD<br>Type | Additional information                 |

|------|-----------------------------------------|--------------------|-----------------|------|-------|------------|----------------------------------------|

| 10   | Ripple and noise,<br>< 500 Hz           |                    | V <sub>PP</sub> |      | 0.500 | 1, 2       | See 33.3.7.7.<br>Balanced              |

|      | Ripple and noise,<br>500 Hz to 150 kHz  |                    | _               |      | 0.200 |            | source imped-<br>ance: R <sub>Ch</sub> |

|      | Ripple and noise,<br>150 kHz to 500 kHz |                    |                 |      | 0.150 |            |                                        |

|      | Ripple and noise,<br>500 kHz to 1 MHz   |                    | -               |      | 0.100 |            |                                        |

| 11   | a) PD Power supply turn on voltage      | V <sub>On</sub>    | V               |      | 42.0  | 1, 2       | See 33.3.7.1                           |

|      | b) PD power supply turn off voltage     | V <sub>Off</sub>   | V               | 30.0 |       | 1, 2       |                                        |

| 12   | PD classification stability time        | T <sub>class</sub> | S               |      | 0.005 |            | See 33.3.7.8                           |

| 13   | Backfeed voltage                        | V <sub>bfd</sub>   | V               |      | 2.80  |            | See 33.3.7.9                           |