# PD I<sub>Port\_RMS\_max</sub> requirement

Lennart Yseboodt, Matthias Wendt Philips Lighting – Research March 10, 2017

innovation 🕂 you

### PD Input power/current requirements

A PD has a number of input power / input current requirements listed as follows:

#### 1. 145.3.8 PD power

The PD shall operate within the characteristics in Table 145-28. Which includes  $P_{Port_PD}$ , which has a maximum of  $P_{Class_PD}$ .

#### 2. 145.3.8.4 Peak operating power

At any static voltage at the PI, and any PD operating condition, with the exception described in 145.3.8.4.1, the peak power for single-signature PDs shall not exceed  $P_{Class\_PD}$  for more than  $T_{CUT-2P}$  min, as defined in Table 145-16 and 5% duty cycle. Peak operating power shall not exceed  $P_{Peak\_PD}$ .

### PD Input power/current requirements

#### 3. 145.3.8.4 Peak operating power

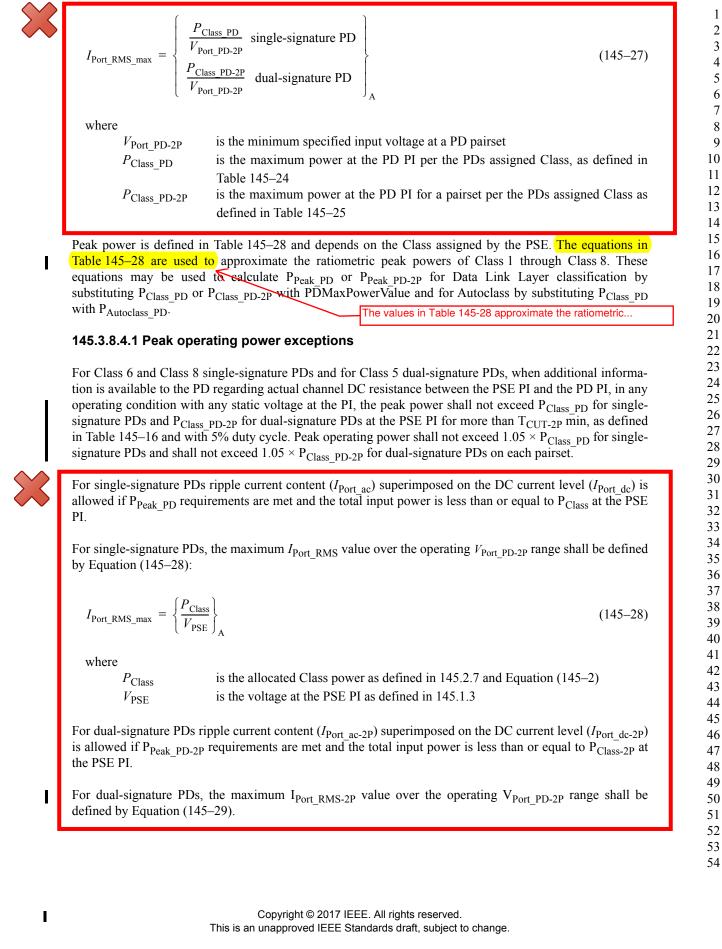

The maximum  $I_{Port\_RMS}$  value for all PDs except those described in 145.3.8.2.1 and 145.3.8.4.1, over the operating  $V_{Port\_PD-2P}$  range shall be defined by Equation (145-27):

$$I_{Port\_RMS\_max} = \left\{ \frac{P_{Class\_PD}}{V_{Port\_PD-2P}} \right\}_{A}$$

(145–27)

$V_{Port\_PD-2P} \text{ is defined as the minimum of the allowed } V_{Port\_PD-2P} \text{ range}.$ This makes the  $I_{Port\_RMS\_max}$  value more permissive than the average and peak input power requirements. The  $I_{Port\_RMS\_max}$  requirement also does not specify a measurement period or window length.

### Average power

#### 145.3.8.2 on Input average power says the following:

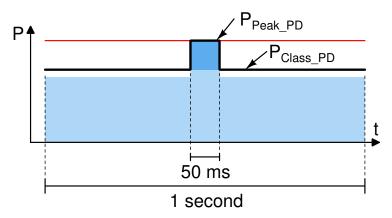

$P_{Class\_PD}$  is the maximum average PI power and applies to single-signature PDs. The maximum average power,  $P_{Class\_PD}$  or  $P_{Class\_PD-2P}$  in Table 145-24, Table 145-25 and Table 145-28 or PDMaxPowerValue in 145.5.3.3, is calculated over a 1 second interval. NOTE - Average power is calculated using any sliding window with a width of 1 s.

Average power over a specified amount of time, is the amount of energy (in Joule) consumed in that time period.

## Specification overview of (1) and (2)

- 1: Absolute max power consumption is P<sub>Peak\_PD</sub>.

- 2a: Total blue area of a sliding window of 1 second must be  $< P_{Class\_PD}$

- 2b: Power not to exceed P<sub>Class\_PD</sub> for more than 50ms/s

### Back to 802.3af

#### 802.3af specified peak current rather than peak power:

| 4 | Peak operating current,<br>Class 0, 3                  | I <sub>Port</sub> | mA | 400 | See 33.3.5.4 |  |

|---|--------------------------------------------------------|-------------------|----|-----|--------------|--|

|   | Peak operating current,<br>Class 1                     | I <sub>Port</sub> | mA | 120 |              |  |

|   | Peak operating current,<br>Class 2                     | I <sub>Port</sub> | mA | 210 |              |  |

| 5 | Input current (DC or RMS),<br>V <sub>Port</sub> =37Vdc | I <sub>Port</sub> | mA | 350 | See 33.3.5.3 |  |

|   | Input current (DC or RMS),<br>V <sub>Port</sub> =57Vdc | I <sub>Port</sub> | mA | 230 |              |  |

This allowed a PD to take significant peak power, eg:

$56V \cdot 400$ mA = 22.4W, far more than the 14.4 W allowed in 802.3at.

## 802.3af and IPort\_RMS

#### 802.3af solved this in the following way:

#### 33.3.5.4 Peak operating current

At any operating condition the peak current shall not exceed  $P_{Port} \max/V_{Port}$  for more than 50ms max and 5% duty cycle max. Peak current shall not exceed  $I_{Port}$  max.

Ripple current content  $(I_{ac})$  superimposed on the DC current level  $(I_{dc})$  is allowed if the total input power is less than or equal to  $P_{Port}$  max.

The RMS, DC and ripple current shall be bounded by the following equation:  $Irms = \sqrt{(Idc)^2 + (Iac)^2}$ .

The maximum  $I_{Port\_dc}$  and  $I_{Port\_rms}$  values for all operating  $V_{Port}$  range shall be defined by the following equation:  $I_{Port\_max}$  [mA] =12950/V<sub>Port</sub>.

With most of the spec written in current, this was the 802.3af way to express the combined power limit of normal and peak power not to exceed 12.95W.

### Definition of average power

Average power is the amount of energy for a given time period, divided by that time period.

$$P_{\text{avg}} = \frac{1}{T_2 - T_1} \int_{T_1}^{T_2} V(t) \cdot I(t) dt$$

There is no such thing as "RMS power". RMS is only a meaningful number for voltages and currents, where it signifies the amount of DC current/voltage that would cause equal power dissipation in a resistor than the signal of interest would.

Power meters report back RMS values of current and voltage, and an average power value. The average power value is determined by sampling *V* and *I* and integrating the product.

### **RMS** current

In a PoE system, the current drawn by the PD may have an irregular waveshape due to the load varying its power consumption in a non repetitive way. An RMS value of this current can be determined, but its value is heavily dependent on the time period considered.

The current specification for  $I_{Port\_RMS\_max}$  is wrong and unnecessary. If the  $P_{Class\_PD}$  and  $P_{Peak\_PD}$  requirements are met, the  $I_{Port\_RMS\_max}$  requirement is automatically met as well. The other way around is not true.

### Back to the future

The 802.3bt (and 802.3at) specification is written around **power** limits. Both average power, as well as absolute peak power is well defined.

The (lengthy) requirement and text around IPort\_RMS and IPort\_RMS\_max is:

- redundant to the power requirements

- ► has issues (uses minimum voltage, no time period specified)

As such this text should be removed.

See appended pages of D2.3 with editing instructions.

### Bibliography

https://en.wikipedia.org/wiki/Root\_mean\_square#Average\_power

https://en.wikipedia.org/wiki/True\_RMS\_converter

Article by Paul Qillen www.n4lcd.com/RMS.pdf

https://www.quora.com/What-is-the-difference-between-average-power-RMS-power-and-AC-power

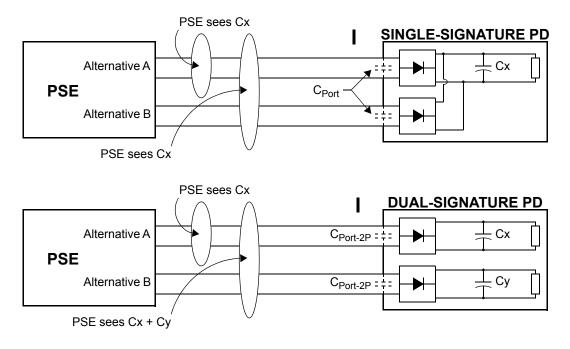

### Figure 145–32—C<sub>Port</sub> interpretation model

NOTE—The "dual-signature PD" in Figure 145–32 represents a PD with two completely isolated circuits connected to Mode A and Mode B. The PSE will see a capacitance of Cx + Cy. A dual-signature PD can also be implemented with a single load, resulting in a lower than Cx + Cy capacitance value as seen by the PSE.

For single-signature PDs, ripple current content  $(I_{Port_{ac}})$  superimposed on the DC current level  $(I_{Port_{dc}})$  is allowed if  $P_{Peak_{PD}}$  requirements are met and the total input power is less than or equal to  $P_{Class_{PD}}$ .

For dual-signature PDs, ripple current content  $(I_{Port_ac-2P})$  superimposed on the DC current level  $(I_{Port_dc-2P})$  is allowed if  $P_{Peak_{PD-2P}}$  requirements are met and the total input power is less than or equal to  $P_{Class_{PD-2P}}$ .

The RMS, DC and ripple current shall be bounded by Equation (145–26):

$$I_{\text{Port}\_\text{RMS}} = \begin{cases} \sqrt{(I_{\text{Port}\_\text{dc}})^2 + (I_{\text{Port}\_\text{ac}})^2} & \text{single-signature PD} \\ \sqrt{(I_{\text{Port}\_\text{dc-2P}})^2 + (I_{\text{Port}\_\text{ac-2P}})^2} & \text{dual-signature PD} \end{cases}$$

(145–26)

where

| $I_{\rm Port\_dc}$      | is the DC component of the input current for a single-signature PD               |

|-------------------------|----------------------------------------------------------------------------------|

| I <sub>Port</sub> ac    | is the RMS value of the AC component of the input current for a single-signature |

| _                       | PD                                                                               |

| I <sub>Port dc-2P</sub> | is the DC component of the input current for a dual-signature PD                 |

| I <sub>Port ac-2P</sub> | is the RMS value of the AC component of the input current for a dual-signature   |

|                         | PD                                                                               |

|                         |                                                                                  |

The maximum  $I_{\text{Port}\_\text{RMS}}$  value for all PDs except those described in 145.3.8.2.1 and 145.3.8.4.1, over the operating  $V_{\text{Port}\_\text{PD-2P}}$  range shall be defined by Equation (145–27):

Draft Amendment to IEEE Std 802.3-2015 IEEE P802.3bt DTE Power via MDI over 4-Pair Task Force

187

$$I_{\text{Port\_RMS-2P\_max}} = \left\{ \frac{P_{\text{Class-2P}}}{V_{\text{PSE}}} \right\}_{\text{A}}$$

(145–29)

where

$\begin{array}{l}P_{\text{Class-2P}}\\ (145-3)\\V_{\text{PSE}}\end{array} & \text{is the allocated Class power on a pairset as defined in 145.2.7 and Equation}\\ \text{is the voltage at the PSE PI as defined in 145.1.3}\end{array}$

NOTE—The duty cycle of the peak current is calculated using any sliding window with a width of 1 s.

### 145.3.8.5 Peak transient current

When the input voltage at the PI is static and in the range of  $V_{Port_PD-2P}$  defined by Table 145–28, the input current drawn by a single-signature PD shall not change faster than  $I_{Slewrate}$  defined in Table 145–28, in either polarity. Each pairset current drawn by a dual-signature PD shall not change faster than  $I_{Slewrate}$  defined in Table 145–28, in either polarity. This limitation applies after inrush has completed (see 145.3.8.3) and before the PD has disconnected.

### 145.3.8.6 PD behavior during transients at the PSE PI

A PD shall continue to operate without interruption in the presence of transients at the PSE PI as defined in 145.2.8.3. A single-signature PD includes  $C_{Port}$  as defined in Table 145–28. A dual-signature PD includes  $C_{Port-2P}$  as defined in Table 145–28 on each pairset.

The following PD configurations intrinsically meet the requirements in this subclause:

- Single-signature Type 3 PDs with peak power not exceeding  $P_{Class_{PD}}$ , and with an input capacitance of 180  $\mu$ F or less

- Single-signature Type 4 PDs with peak power not exceeding  $P_{Class_PD}$ , and with an input capacitance of 360  $\mu$ F or less

- Dual-signature Type 3 PDs with peak power draw not exceeding  $P_{Class\_PD-2P}$ , and with an input capacitance of 110  $\mu$ F or less per pairset

- Dual-signature Type 4 PDs with peak power draw that does not exceed P<sub>Class\_PD-2P</sub> and with an input capacitance of 180 μF or less per pairset

| PD Type | Transient condition | Initial voltage              | Final voltage                           | Source<br>dv / dt | Source<br>resistance     | Source current                    |

|---------|---------------------|------------------------------|-----------------------------------------|-------------------|--------------------------|-----------------------------------|

| 3, 4    | TR1                 | V <sub>Port_PSE-2P</sub> min | 56 V                                    | 2250 V/s          | $R_{Ch} \pm 2.5\%$       | Limited by Equa-<br>tion (145–30) |

| 3, 4    | TR2                 | V <sub>Port_PSE-2P</sub> min | V <sub>Port_PSE-2P</sub> min<br>+ 2.5 V | 3.5 V/µs          | $1.5 \ \Omega \pm 2.5\%$ | > 5 A capability                  |

### Table 145–29—Transient conditions

Table 145–29 defines two PSE transient conditions and PD Types to which these apply. Figure 145–33 shows operating bounds for the transients in Table 145–29. The shaded regions begin with the application of the transient and end at the times indicated in the Figure. These shaded regions can exceed normal operating limits and are not included in the average and peak operating power requirements set forth in Table 145–28.