### **Inrush NOPOWER**

HEATH STEWART DAVID STOVER

#### **Summary**

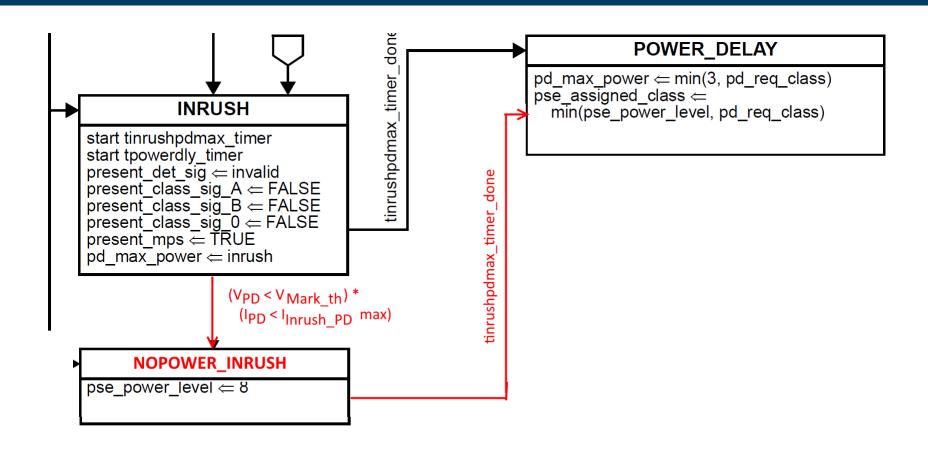

- As written PD INRUSH state does not allow a PD to increment pse\_power\_level

- ► PD INRUSH state has a duration of exactly 50ms

- ► PD PI V<sub>PD</sub> may drop below V<sub>Mark th</sub> during the INRUSH state

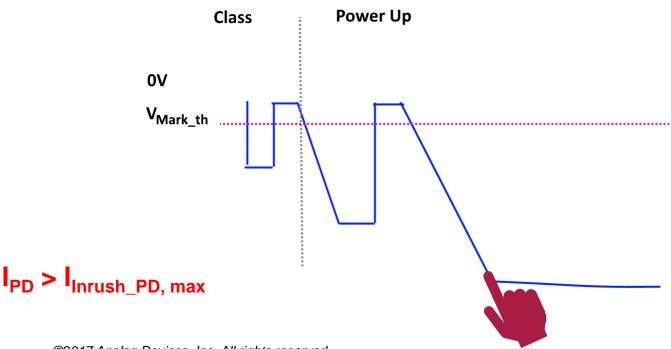

- Case 1: PD itself causes the voltage transient

- e.g. Switching on a substantial bulk capacitance

- Case 2: PD input voltage is manipulated externally

- e.g. PD compliance testing

- This voltage manipulation may be interpreted as a "false" mark event

# Case 1 PD Causes "False" Mark Event

- ► In this case, PD has *caused* the voltage drop

- Burden is on PD not to "increment" pse\_power\_level

- Risks tricking itself into thinking it has been allocated additional power

- ► Note: A PD is not allowed to oscillate during power up

# Case 2 (Invalid) PSE Causes "False" Mark Event

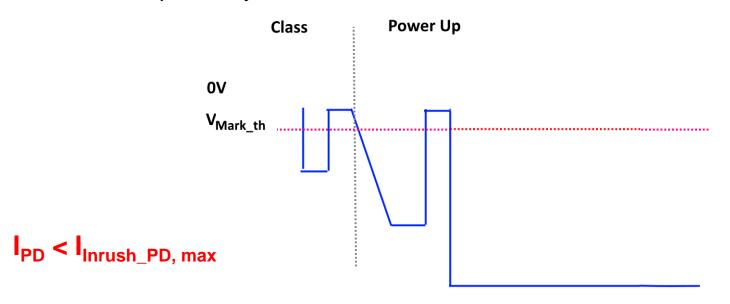

- Many PDs stay below I<sub>Inrush PD</sub> during power up

- A valid PSE will not collapse the voltage in this case

- In a compliant system, PD input voltage does not drop below V<sub>Off\_PD</sub> during inrush

- No interoperability requirement exists in this case

- Compliance with D3.3 INRUSH is an unnecessary burden for these PDs

- No interoperability benefit

#### **Baseline Fix**