# Proposed Baseline text for: Chip-to-module 25 Gb/s onelane Attachment Unit Interface (XXVAUI-1)

Tom Palkert Molex Jan. 5 2015

# Summary

- Heavily leverages 802.3bm Annex 83E (CAUI-4 Chip to Module)

- Changes to Intro text

- Changes to ISO diagram and application diagram

- Changes to PICS pro forma 'protocol summary' and 'major capabilities/options' tables

- All other sections referenced directly with change from '4 lane' to '1 lane'

## Clause structure

| Clause       | Changes                                                  |

|--------------|----------------------------------------------------------|

| Χ            | Introduction to 25 Gb/s networks                         |

| X+1          | 25G RS + XXVMII                                          |

| X+2          | 25G PCS ***                                              |

| X+3          | 25G FEC                                                  |

| X+4          | 25G PMA                                                  |

| X+5          | 25GBASE-CR PMD (copper cable) ***                        |

| X+6          | 25GBASE-KR PMD (backplane)                               |

| X+7          | 25GBASE-SR PMD (MMF optical)                             |

| Annex (X+4)A | XXVAUI chip-to-chip                                      |

| Annex (X+4)B | XXVAUI chip-to-module                                    |

| Annex (X+5)A | 25GBASE-CR TP parameters and channel characteristics     |

| Annex (X+5)B | 25GBASE-CR cable/host use cases ***                      |

|              | *** indicates Clauses/Annexes that need significant work |

• From brown\_092414a\_25GE\_adhoc

### Possible issues

- HCB/MCB performance

- See diminico presentation

- Crosstalk parameters/test procedures

- For single lane

# Overview paragraph

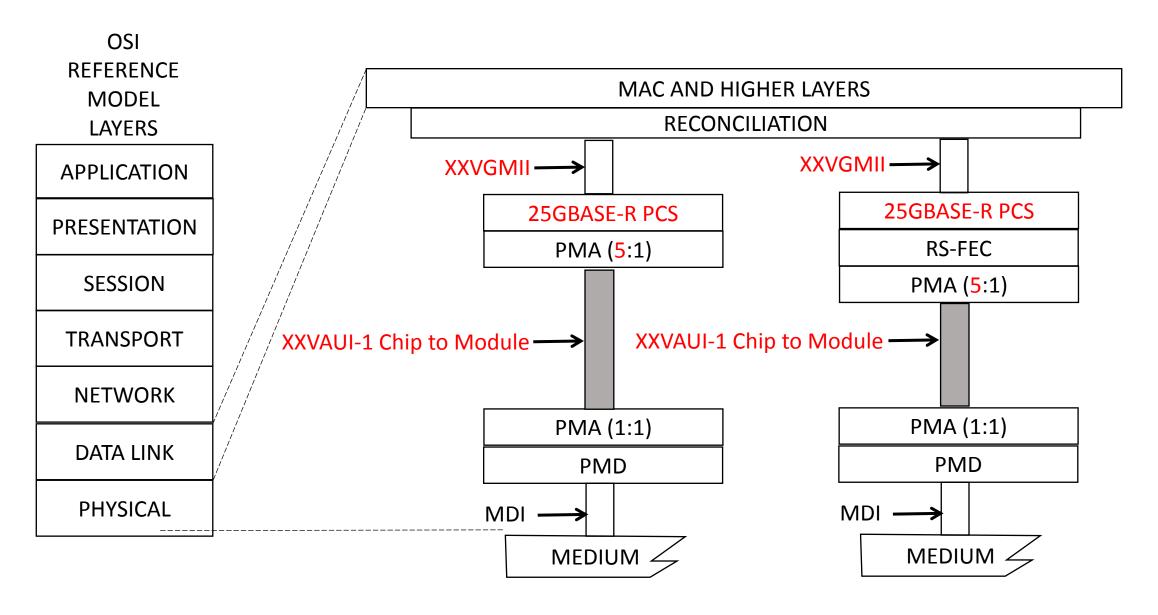

This annex defines the functional and electrical characteristics for the optional chip-to-module 25 Gb/s One-lane Attachment Unit Interface (XXVAUI-1). Figure X+4B-1 shows the relationship of the XXVAUI-1 chip-to-module interface to the ISO/IEC Open System Interconnection (OSI) reference model. The chip-to-module interface provides electrical characteristics and associated compliance points which can optionally be used when designing systems with pluggable module interfaces.

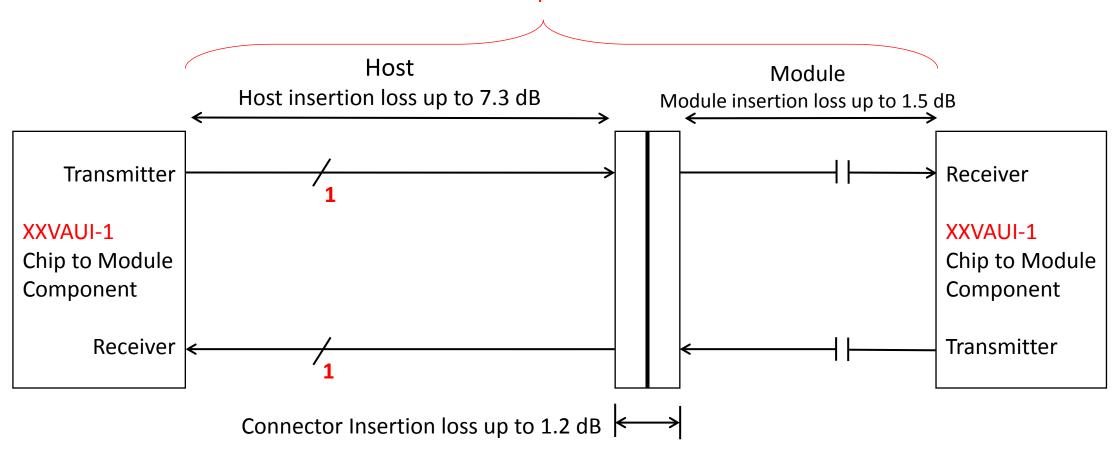

The XXVAUI-1 link is described in terms of a host XXVAUI-1 component, a XXVAUI-1 channel with associated insertion loss, and a module XXVAUI-1 component. Figure X+4B-2 depicts a typical XXVAUI-1 application, and summarizes the differential insertion loss budget associated with the chip-to-module application. The XXVAUI-1 chip-to-module interface comprises independent data paths in each direction. Each data path contains one differential lane which is AC coupled within the module. The nominal signaling rate is 25.78125 GBd. The chip-to-module interface is defined using a specification and test methodology that is similar to that used for CEI-28G-VSR defined in OIF-CEI-03.1 [Bx1].

Figure X+4B-1—Example XXVAUI-1 chip-to-module relationship to the ISO/IEC Open System Interconnection reference model and the IEEE 802.3 CSMA/CD LAN model

#### XXVAUI-1 Chip to Module Channel

Figure X+4B.2: Chip-to-module insertion loss budget at 12.89 GHz

#### 83E.5.2.2 Protocol summary

IEEE Std 802.3by-201x, Annex X+4B, Chip to module onelane 25Gb/s Attachment Unit Interface (XXVAUI-1)

| Identification of protocol standard                                                                                                                           | IEEE Std 802.3bm-201x, Annex 83E, Chip-to-module four-<br>lane 100 Gb/s Attachment Unit Interface (CAUI-4) |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|--|

| Identification of amendments and corrigenda to this<br>PICS proforma that have been completed as part of<br>this PICS                                         |                                                                                                            |  |  |

| Have any Exception items been required? No [] Yes [] (See Clause 21; the answer Yes means that the implementation does not conform to IEEE Std 802.3bm-201x.) |                                                                                                            |  |  |

#### 83E.5.3 Major capabilities/options

One

| Item | Feature                                 | Subclause   | Value/Comment                                                    | Status | Support           |

|------|-----------------------------------------|-------------|------------------------------------------------------------------|--------|-------------------|

| NOL  | Number of differential AC coupled lanes | 83E.1       | Four independent data paths<br>in each direction                 | М      | Yes [ ]           |

| BER  | Meets CAUI-4 BER require-<br>ment       | 83E.1.1     | See 83E.1.1                                                      | М      | Yes [ ]           |

| ADR  | Adaptive receiver                       | 83E.3.4.1.1 | Module CAUI-4 receiver does<br>not use<br>Recommended_CTLE_value | 0      | Yes [ ]<br>No [ ] |

### Proposed text if compliance board performance is different than CAUI-4

#### X+4B.4 XXVAUI-1 measurement methodology

X+4B.4.1 HCB / MCB characteristics This subclause describes common measurement tools and methodologies to be used for the XXVAUI-1 chip-to-module interface. Details of HCB and MCB characteristics are given in X+4B.4.1 and details of the eye diagram measurement methodology are given in 83E.4.2.

#### X+4B.4.1 HCB/MCB characteristics

HCB characteristics are described in xx.xx.1 where the HCB performs the equivalent function as the TP2 or TP3 test fixture. The MCB characteristics are described in xx.xx.2 where the MCB performs the equivalent functionality as the cable assembly test fixture.