# **TX DIFFERENTIAL PRECODER FOR 50Gb/s ELECTRICAL LINKS**

Raj Hegde & Magesh Valliappan

IEEE 802.3cd Task Force, IEEE 802.3 Plenary Meeting, July 2016, San Diego, CA.

#### **Case for the Precoder**

- FFE/CTLE and/or DFE are used to cancel ISI due to insertion loss

- FFE/CTLEs generally enhance noise but do not cause burst errors

- DFEs don't cause noise enhancement

- large tap weight due to high insertion loss can cause burst errors

- How do we limit burst errors?

- Limiting DFE tap weights (or the 'a' value) is an option.

- This implies that the ISI has to compensated for in some other way

- How to we check for compliance on tap weight limits?

- Precoding is an attractive alternative to limiting tap weights

- Precoder can mitigate burst errors due to high DFE tap-1

- Shaping higher DFE taps (taps 2, 3,...) is a lot easier

- Precoding function in the TX is activated when the RX needs it

- Does not affect a receiver that doesn't need it

#### • Expands the receiver design space with minimal overhead

#### **Precoder deployment**

- Precoding will be used only when needed

- Mandatory implementation in the TX.

- Enabled when the receiver/system deems precoding to be beneficial

- Chip-to-Chip segment

- Terminated in the electrical RX.

- Can be enabled using the management interface (currently used to configure TX-FIR)

- Shown in Hegde\_3bs\_01a\_1115

- Back Plane/ Direct Attach Cable application

- Enabled as part of the far-side transmitter tuning protocol

- Shown in <u>healey\_3cd\_01\_0516</u>

- No performance impact on

- an FFE based design

- segments other than C2C on a multi-segment link.

#### **Implementation Complexity**

- Purely digital implementation

- Area estimate and gate-count for different levels of parallelization

|                                    | <b>10T</b><br>(10 symbols/<br>10T cycle) | 16T | 20T | 32T |

|------------------------------------|------------------------------------------|-----|-----|-----|

| Design Area (µm <sup>2</sup> )     | 45                                       | 51  | 60  | 75  |

| Gate Count<br>(NAND2x1 equivalent) | 248                                      | 281 | 330 | 413 |

- Timing closure wasn't an issue on a commercially available advanced CMOS process node.

- Implementation overhead is minimal

## **Simulation Assumptions/Details**

- RS (544, 514) FEC is assumed

- Bit-muxing

- Symbol mutliplexing

- Round robin distribution of FEC symbols to the PCS lanes & muxing in the PMA

- Performance remains the same as multiplexing

- Gray Coding: Noise events can cause at most one bit error

- Burst error model

- Same as anslow\_3cd\_01\_0516

- Target Performance levels

- Frame Loss Ratio (BER equivalent): 6.2E-10 (1E-12), 6.2E-13 (1E-15), and 6.2E-15 (1E-18)

- Single PAM4 electrical link & Multi-part link scenarios

- Performance results without bit-muxing can be found in <u>hegde\_3cd\_01a\_0516</u>

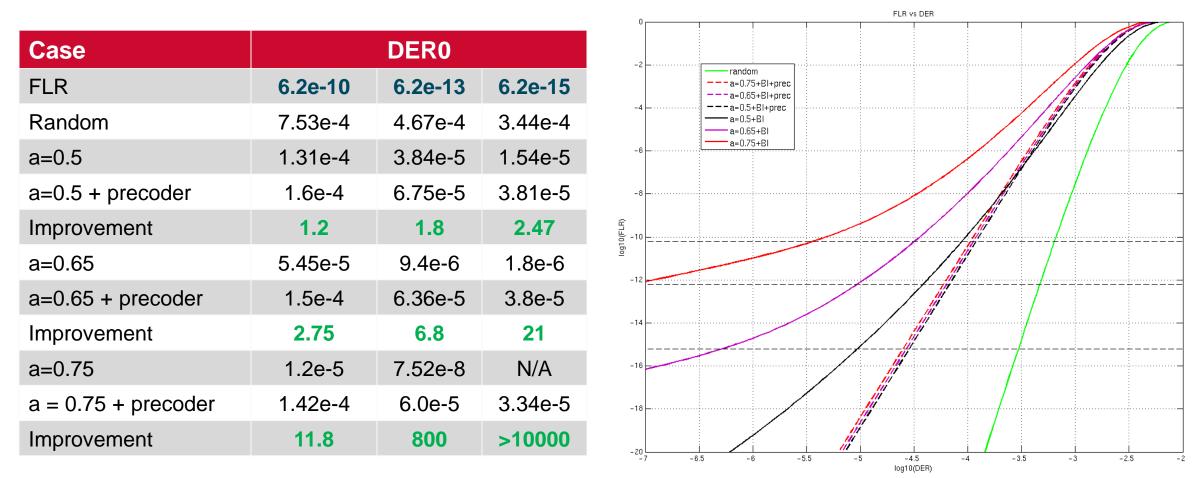

## Single Electrical Link – FLR vs DER0 with Bit Multiplexing

- At FLR = 6.2E-10, 'effective a' due to the precoder is better than 0.5

- Allows a BER target of 1E-4 for Back-plane and Direct Attach Cable applications

BROADCOM<sup>®</sup>

## Multi-segment Link – FLR vs DER0 with Bit Multiplexing

Optical link is held at BER = 2.4e-4 (0.16dB penalty)

|                     |         | FLR vs DER                                       |

|---------------------|---------|--------------------------------------------------|

| Case                | DER0    |                                                  |

| FLR                 | 6.2e-10 | -2                                               |

| Random              | 2.73e-4 | a=0.65+Bl+prec                                   |

| a=0.5               | 3.7e-5  | -4 - a=0.5+BI+prec $-4 - a=0.5+BI$               |

| a=0.5 + precoder    | 5.3e-5  |                                                  |

| Improvement         | 1.43    |                                                  |

| a=0.65              | 1.26e-5 |                                                  |

| a=0.65 + precoder   | 5e-5    |                                                  |

| Improvement         | 4       | -10                                              |

| a=0.75              | 1.21e-6 |                                                  |

| a = 0.75 + precoder | 4.8e-5  |                                                  |

| Improvement         | 40      |                                                  |

|                     |         | -7 -6.5 -6 -5.5 -5 -4.5 -4 -3.5 -3<br>log10(DER) |

• At FLR = 6.2E-10, 'effective a' due to the precoder is better than 0.5

• Allows a BER target of 1E-5 for chip-to-chip application

### **Summary**

- Effective for burst error protection due to dominant 1<sup>st</sup> tap in the DFE

- Alternative of limiting 'a' would impact link performance.

- Enabled only when needed

- No impact to an RX that doesn't need it

- Limited to chip-to-chip segment and Backplane/DAC links.

- Does not affect other segments of a multi-segment link

- Minimal overhead in terms of area, power, and design complexity

- less than 500 gates and approximately 50-80um<sup>2</sup> area

- Broadens the receiver design space by enabling a new class of receivers