# TDECQ Reference Receiver Precursor Constraint

Phil Sun, Credo Semiconductor

IEEE 802.3cd Interim, May 2018

# <u>Supporters</u>

- Haifeng Liu, Intel

- Chris Cole, Finisar

- Piers Dawe, Mellanox

- Mark Kimber, Semtech

- Bharat Tailor, Semtech

- Kohichi Tamura, Oclaro

- Jeff Twombly, Credo

- Paul Brooks, Viavi

- Richard Mellitz, Samtec

- Mike Dudek, Cavium

- Matt Traverso, Cisco

- Zvi Rechtman, Mellanox

- Zhigang Gong, O-netcom

- Johan Jacob Mohr, Mellanox

- Karen Liu, Kaiam

## **Introduction**

- O Historically TDECQ reference receiver was changed from 5-tap T/2 FFE to 5-tap T-spaced FFE to increase transmitter yield on TDECQ test. Considering post-cursors are usually important for channel loss and reflections, the maximum range of precursors was increased from about 1 UI to 2 UI. Receiver complexity caused by this has recently drawn attention. (Hope this had happened earlier!) Current spec allows up to two precursors [king 3cd 03 0118.pdf, sun 3cd 01a 0118.pdf].

- O Supporting multiple precursors forces real receivers to choose power-hungry structures. Meanwhile precursor 2 is not needed for systems with good bandwidth and little pre-cursor fiber dispersion, and can be compensated by TX FIR if needed [sun\_3cd\_042518\_adhoc, dawe\_3cd\_01a\_0318].

- This contribution proposes to constrain optical signal precursors, therefore simplify receiver design, and ensure interoperability.

- Simpler tasks, higher efficiency, lower cost!

# Cost of Precursor 2

- In general there will be hardware and power cost to support more precursors.

- For some architectures, pre-cursors are more costly than post-cursors and may bring extra distortion. For those SERDES without high-precision ADC, more precursors are usually difficult.

- Optimizing main tap location is possible on real receiver, but at significant cost of extra hardware and power.

- Small residual on precursor 2 (caused by temperature variation etc.) may be compensated by low cost techniques. But unconstrained precursor 2 allowed by current spec, which could be caused by wrong TX FIR settings, forces power-hungry receivers with multiple precursors.

- Receiver complexity and power can be significantly reduced if wild input signals are prohibited by defining good standards.

# TDECQ Measurement Results

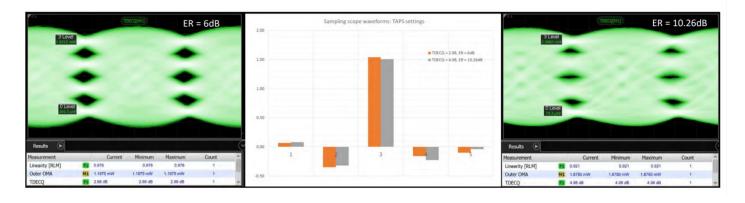

- TDECQ changes made in IEEE802.3bs and IEEE802.3cd, including 5-tap T-spaced FFE and threshold adjustment, are reported to effectively improve transmitter yield. Meanwhile precursor 2 is usually small, and has relatively less impact.

- For example, <u>mazzini 3bs 01 0917.pdf</u> shows main tap is optimized to tap 3 (2 precursors) for good transmitters. Precursor 2 is small.

Transmitter results over two reference settings: PRBS20.

### Theoretical Studies on Tap Weights

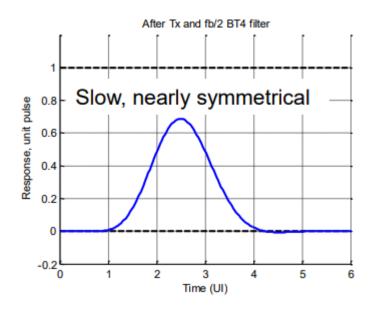

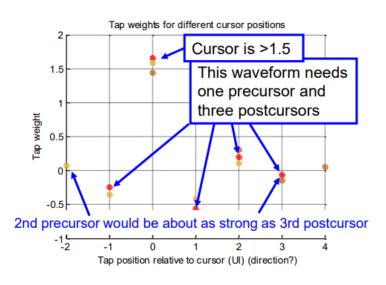

o dawe 3cd 01a 0318 shows the weight of precursor 2 is close to post 3 for most slow signal allowed for SMF. On top of this, reflections may happen on post 3 and need to be equalized.

#### TDECQ Measurement With TX FIR

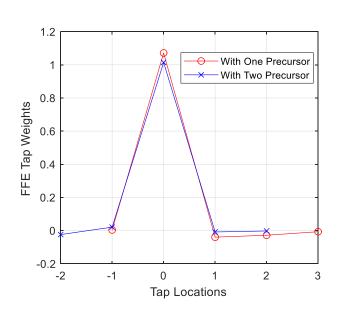

- We compared 100GBASE-DR TDECQ results for different number of FFE precursors.

- o If without any TX FIR, TDECQ is very bad.

- If playing with TX FIR, reference FFE with one or two precursors give similar TDECQ.

| Number of reference<br>FFE precursors | One  | two  |

|---------------------------------------|------|------|

| TDECQ (dB)                            | 1.73 | 1.69 |

#### Bandwidth Variation Impact on Precursors

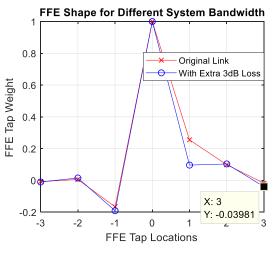

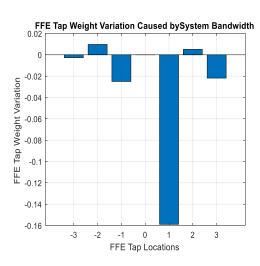

- o Compared to postcursor taps, precursor tap weights are less impacted by bandwidth variation due to temperature etc.

- FFE tap weight changes are analyzed for 3dB loss variation (modeled by adding an extra first order LPF). FFE main cursor is normalized to 1.

- o Bandwidth impact due to temperature etc. is mainly on post 1. precursor 2 variation is only about 1%. This weight is less than uncancelled post 3, and can be compensated by some simple equalization structures or simply left as residual.

- As a reference, precursors are typically handled by TX FIR for electrical links. TX FIR is only calibrated during link up training.

### Proposed Changes for 100GBASE-DR

#### 140.7.5.1 TDECQ reference equalizer

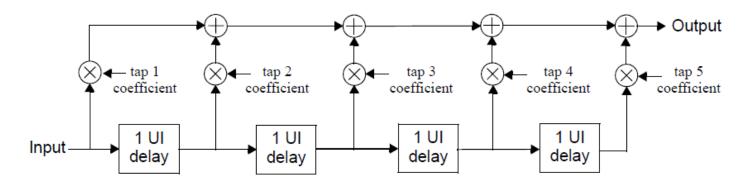

The reference equalizer for 100GBASE-DR is a 5 tap, T spaced, feed-forward equalizer (FFE), where T is the symbol period. A functional model of the reference equalizer is shown in Figure 140–4. The sum of the equalizer tap coefficients is equal to 1. Tap 1, tap 2, or tap 3, has the largest magnitude tap coefficient.

Figure 140–4—TDECQ reference equalizer functional model

• Changes:

Tap 1 or tap 2, has the largest magnitude tap coefficient.

# **Impact of This Proposal**

- o Minimizes precursor 2 weight at optical output by providing good system bandwidth or TX FIR. Prevents artificial large precursor 2 due to wrong TX FIR settings.

- This proposal does not prohibit a receiver from implementing multiple precursors, but guarantees small weight of residual precursor 2. Receiver can take advantage of this and equalize this small residual (due to bandwidth variation etc.) by more power efficient schemes. Note precursor variations due to temperature etc. is relatively small.

- o Impact on TDECQ should be trivial if assuming TX FIR. (TDECQ threshold may be adjusted to enable broader implementations while not reject good transmitters.)

- Compared to power-hungry receiver demanded by current spec, TX FIR complexity is trivial but effective on precursor cancellation.

- This contribution focuses on 100GBASE-DR to enable low power module (100G, 400G, and future 800G etc.).

Clean 106Gbps Eye after 13.2dB Channel with TX FIR

# **Conclusions**

- FFE precursor 2 in TDECQ test is usually small or not needed for optical links with good bandwidth and little precursor distortion, and precursor equalization can be done on TX.

- Device bandwidth will improve and receiver will not need heavy precursor 2 for good links. But current standard allows transmitters to create precursor 2, forces real receivers to implement expensive multiple precursors to ensure interoperability (to be standard compliant), therefore causes module power to stay high forever.

- To enable low power modules and ensure interoperability, propose to **limit** the number of precursors to one for 100GBASE-DR.

Thanks!