# IEEE *Draft* P802.3cg/D3.0 10BASE-T1L LPI synchronization

**Proposal relating to comment i-285**

MICK MCCARTHY, ANALOG DEVICES 24 MAY 2019

## LPI QUIET REFRESH synchronization

- IOBASE-T1L LPI includes no mechanism to provide a PHY with clear timing information about when LPI QUIET and REFRESH modes will be entered and exited.

- This has potential to cause difficulty for 10BASE-T1L EEE PHY implementations. LPI modes will be entered and exited depending on data traffic.

- Other PHY technologies that employ of MASTER/SLAVE timing scheme and echo cancellation employ some kind of synchronization such that PHY implementations enjoy more certainty about when LPI modes are entered and exited.

- 1000BASE-T symmetric LPI

- 1000BASE-T1 asymmetric LPI, with LPI synchronization (subclause 97.3.5.1)

#### **Overview of proposal**

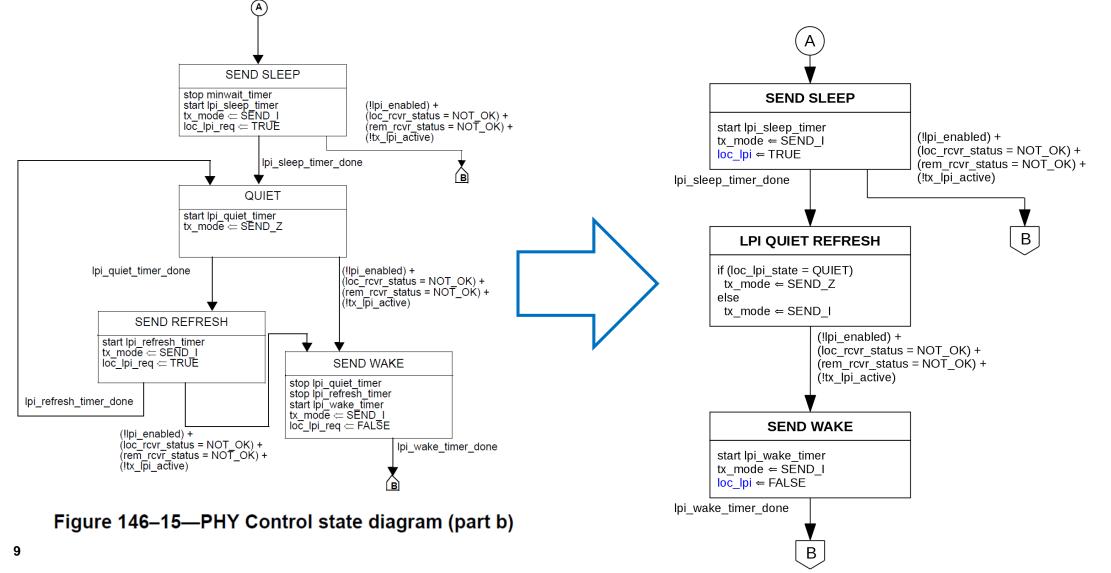

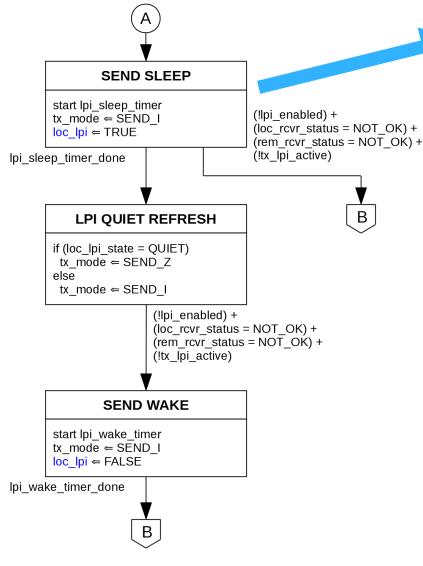

- Modify 10BASE-T1L PHY Control state diagram to add LPI synchronization mechanism using loc\_lpi\_req signal in advance of SEND IDLE OR DATA (link up).

- LPI synchronization mechanism dictates when a new LPI QUIET REFRESH timing state machine starts.

- Start of LPI QUIET REFRESH timing is communicated to link partner using loc\_lpi\_req signal, i.e. observed in link partner as rem\_lpi\_req

- ► LPI QUIET REFRESH timing state machine would remain active for the lifetime of the link.

- ► LPI QUIET REFRESH timing would synchronize to the symbol timer (TX\_TCLK).

- A PHY implementation could take advantage of LPI synchronization:

- To know when the link partner PHY is in the REFRESH state, and can restrict channel equalizer coefficient adaptation to only be active during this window.

- To know when local PHY is in the REFRESH state, and can restrict echo canceller coefficient adaptation to only be active during this window.

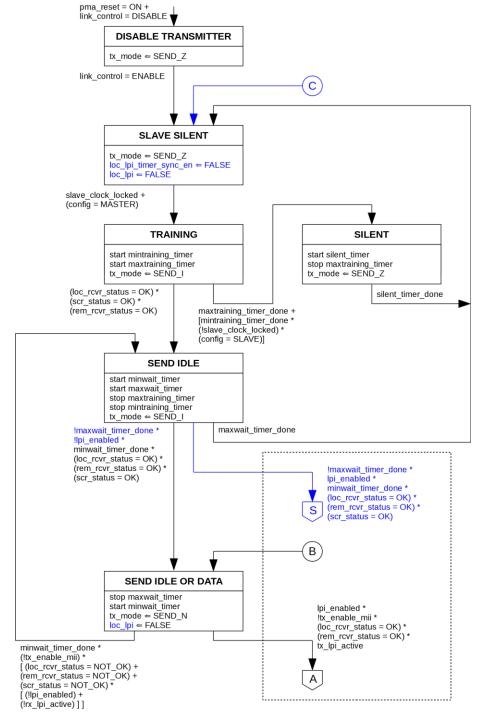

# Figure 146-14 – PHY Control state diagram (part a)

- Added entry to LPI synchronization sequence on exit from SEND IDLE state for LPI mode (labelled 'S' in diagram)

- New output from PHY Control state diagram: loc\_lpi\_timer\_sync\_en

- TRUE enables local LPI synchronization timing

- FALSE disables local LPI synchronization timing

- Not encoded in transmit symbol stream; no new communicated parameters required

- Note some minor corrections

- Use of !maxwait\_timer\_done in exit transitions from SEND IDLE

- Renaming loc\_lpi\_req as loc\_lpi (see later explanation)

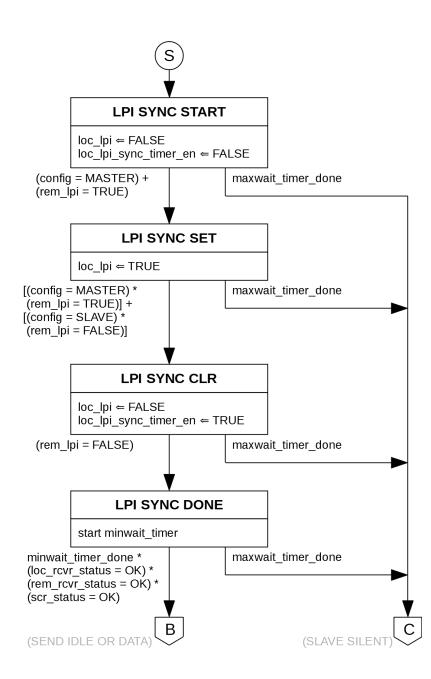

## **PHY Control LPI synchronization**

- ► LPI synchronization sequence is described as follows:

- MASTER first sets loc\_lpi = TRUE

- SLAVE waits to see rem\_lpi = TRUE (from MASTER), and then sets loc\_lpi = TRUE

- MASTER waits to see rem\_lpi = TRUE (from SLAVE), and then sets loc\_lpi = FALSE

- MASTER also sets loc\_lpi\_sync\_timer\_en = TRUE at the same time

- SLAVE waits to see rem\_lpi = FALSE (from MASTER), and then sets loc\_lpi = FALSE

- SLAVE also sets loc\_lpi\_sync\_timer\_en = TRUE at the same time

- In both MASTER and SLAVE, transition of loc\_lpi from TRUE to FALSE occurs at the same time as start of local LPI synchronization timing (loc\_lpi\_sync\_timer\_en transition from FALSE to TRUE).

- LPI synchronization mechanism takes place before link startup completion (PHY Control transition to SEND IDLE OR DATA).

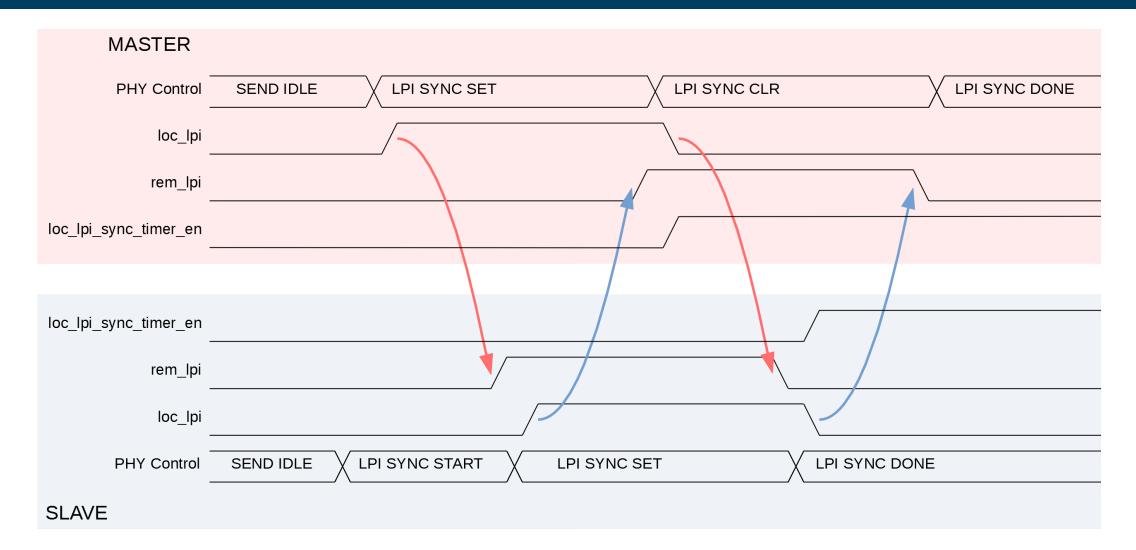

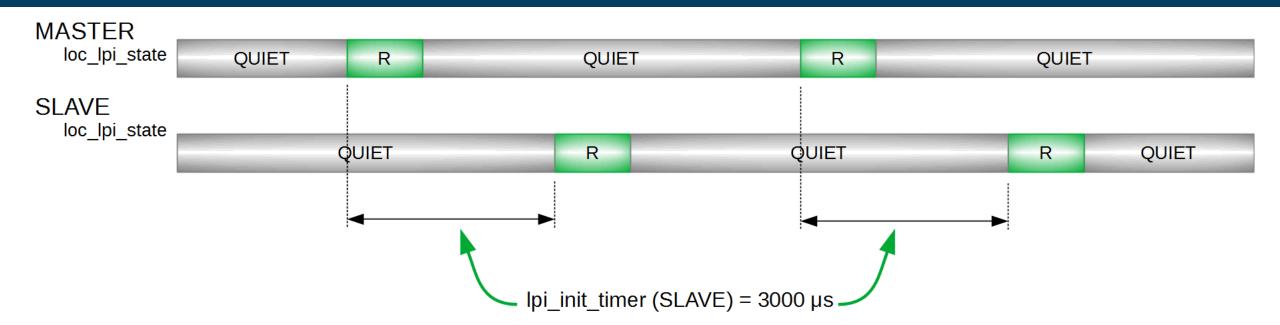

## LPI synchronization timing diagram

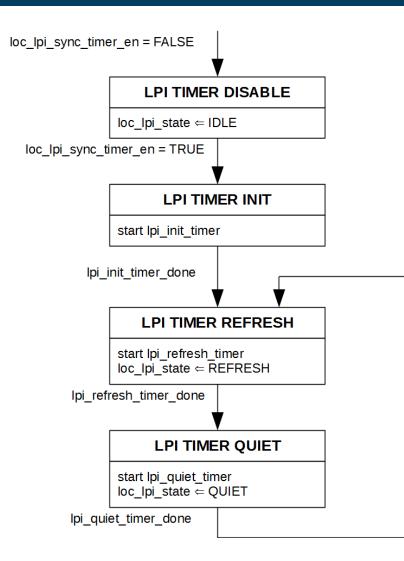

## LPI QUIET REFRESH timing state diagram

- Timing offset between MASTER and SLAVE REFRESH is effected in LPI TIMER INIT state:

- Define lpi\_init\_timer duration differently between MASTER and SLAVE

- MASTER lpi\_init\_timer duration 0 µs

- SLAVE lpi\_init\_timer duration 3000 µs

- This offset, i.e. 3000 µs, should be maintained for lifetime of link

- Maintain lpi\_refresh\_timer and lpi\_quiet\_timer:

- Ipi\_refresh\_timer 250 µs

- Ipi\_quiet\_timer 6000 µs

- All timers here would be synchronized to symbol period (TX\_TCLK). Might be defined in terms of symbol periods.

- As SLAVE maintains timing lock with MASTER, so timing relationship between MASTER and SLAVE LPI QUIET REFRESH cycling should also remain fixed (and predictable)

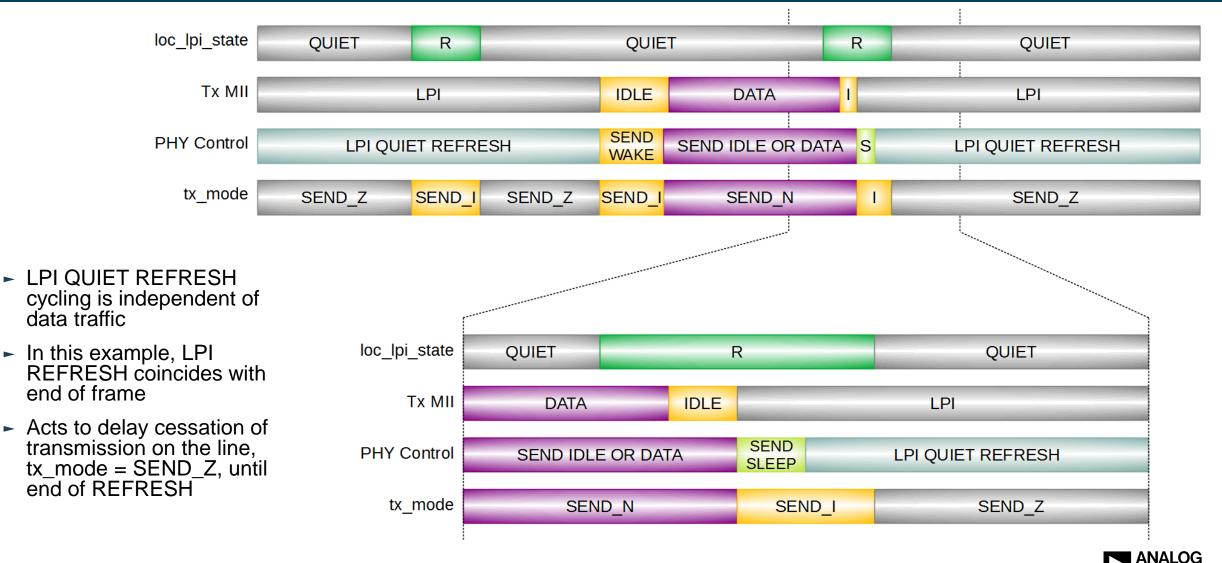

## LPI QUIET REFRESH cycling

- Time offset between MASTER and SLAVE LPI QUIET REFRESH cycling remains fixed for lifetime of link

- 3000 µs, as per lpi\_init\_timer duration

## **PHY Control LPI sequencing**

Combined LPI QUIET REFRESH state, with QUIET/REFRESH mode determined by loc\_lpi\_state variable

ANALOG

AHEAD OF WHAT'S POSSIBLE™

## PHY Control LPI sequencing – Ipi\_sleep\_timer duration

- Propose to reduce lpi\_sleep\_timer duration

- Currently this is set to 250 µs (as per <u>Graber\_3cg\_01a\_0419</u>)

- The reason for the relatively long duration here is to allow any ongoing adaptation tasks to complete before transmission ceases in QUIET state.

- But, given that link partner LPI QUIET REFRESH cycling can be known with certainty, a PHY should align to this, and should never require a longer duration in SEND SLEEP.

- Propose lpi\_sleep\_timer duration of 20 µs, same as minwait\_timer duration.

- Might be specified in terms of transmit symbol periods.

## LPI and frame transmission

#### **Potential energy savings**

- The reduced duration of the lpi\_sleep\_timer provides for improved energy savings, as the QUIET state should be reached sooner than in the current draft.

- A persistent data traffic pattern which provides a short period of LPI assertion between sending frames can even prevent entry to LPI QUIET altogether, if the period of LPI assertion is less than the lpi\_sleep\_timer. The only mitigation is to keep lpi\_sleep\_timer to a minimum.

- Knowledge of local and remote LPI refresh timing allows PHY implementation easier way of planning for filter coefficient updates

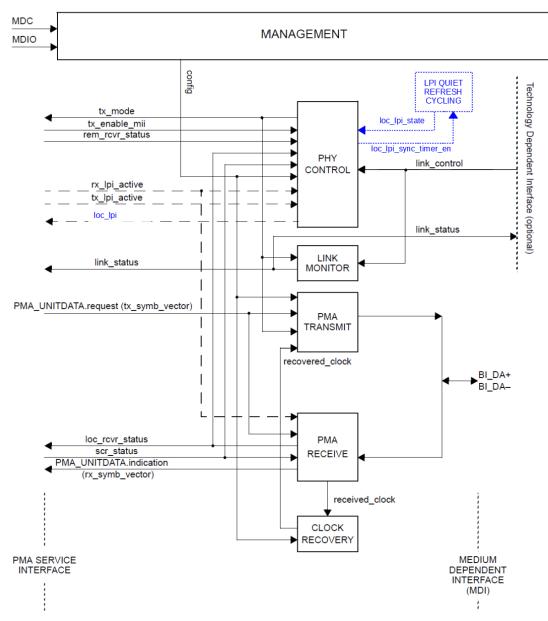

NOTE 1—The "recovered\_clock" shown indicates the delivery of the recovered clock back to PMA TRANSMIT in SLAVE mode for loop timing.

NOTE 2-Signals shown with dashed lines are required only for EEE functionality.

## Figure 146-11

Thank you

#### Note on LPI signal naming

- loc\_lpi\_req and rem\_lpi\_req naming used in D3.0.

- These names have been lifted from 1000BASE-T (Clause 40), and are not used in other PHY standards.

- The naming is appropriate for the symmetric LPI scheme of 1000BASE-T, where the PHYs must both simultaneously signal a request for LPI mode in order for the LPI mode to be entered.

- Where this is signalled from one PHY only it is only a request for LPI mode.

- In the context of 10BASE-T1L asymmetric LPI these names are inappropriate. For 10BASE-T1L, loc\_lpi\_req does not represent a request, and is rather a signal that the PHY transmit has entered the LPI mode of operation.

- Therefore, the following naming is proposed:

- Ioc\_lpi\_req → loc\_lpi

- rem\_lpi\_req → rem\_lpi