# Clause 104 Modifications for 10SPE

HEATH STEWART

## **Presentation Objectives**

- Accommodate 10SPE Long Reach

- Additional PHY capacitance

- Ikm Fieldbus Type A STP cabling

- Propose changes to Clause 104 SCCP to support 10SPE

- Modifications to SCCP timing

- Add clarity for PD reservoir capacitor recharge

- Add clarity to TSLOT by splitting into RESET, READ, and WRITE variants

### **Justification**

- PoDL provided two separate means of positively identifying a PD

- Detection Used for engineered systems requiring < 10ms start-up eg automotive</li>

- Not compatible with resistance of 10SPE Long Reach cable

- Classification Used for discoverable systems

- Based on 1-Wire<sup>™</sup>

- Does not require valid detection

- PD relies on "parasite power" for PSE during classification sequence

- PoDL classification is appropriate for 10SPE Long Reach

- Can be readily adapted to higher PHY and cable capacitance

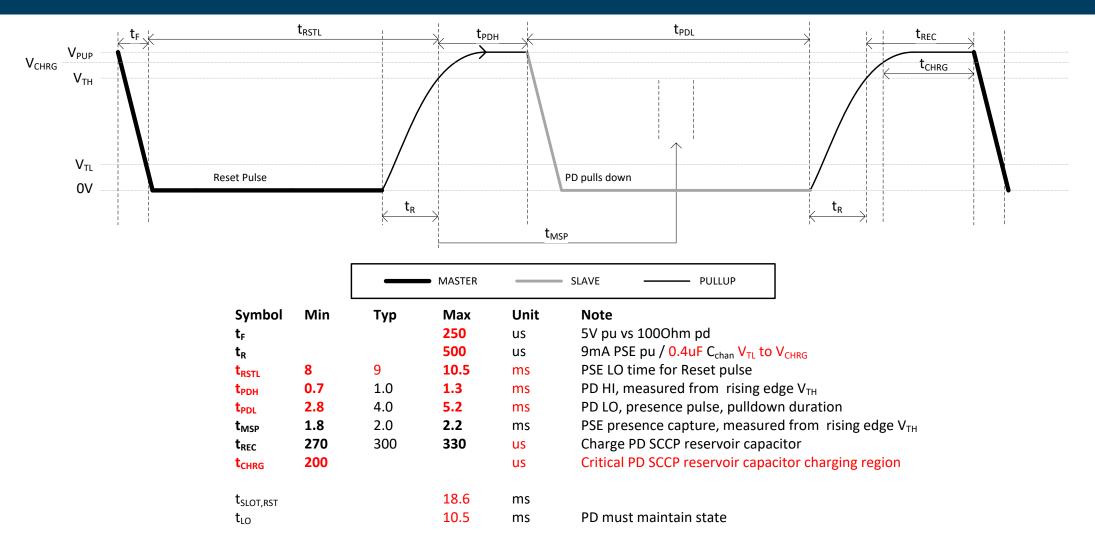

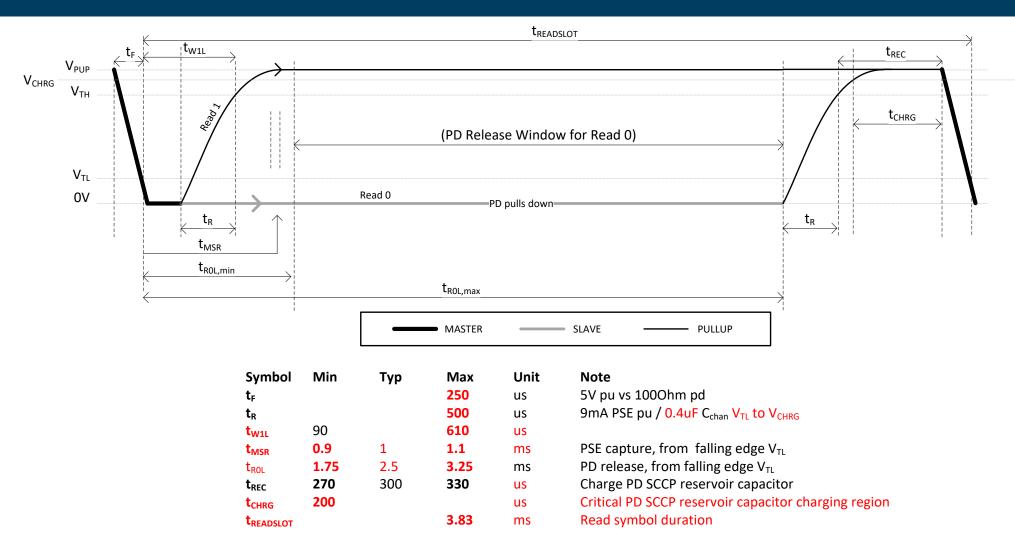

- $T_R$ , rise time, and  $T_F$ , fall time, must be extended

- To avoid slower bit rate, tighten PD timing uncertainty budget

- Was: +/-50%

- Propose: +/-30%

## **Presentation Objectives**

- ► Modify Table 104-8 SCCP Electrical Requirements

- Add clarity for PD reservoir capacitor recharge

- Create V<sub>CHRG, min</sub> = V<sub>PUP, min</sub> \* 90%

- Create t<sub>CHRG, min</sub> = 200us

- Track changes to PHY and cable capacitance

- Change C<sub>IN\_Class</sub> to 400nF

- Change C<sub>Bus</sub> to 72nF (TBD)

- Add clarity to T<sub>SLOT</sub> by splitting into RESET, READ, and WRITE variants

- Add  $t_{RSTSLOT}$ ,  $t_{WRITESLOT}$ ,  $t_{READSLOT}$  as shown in following slides

- Remove t<sub>SLOT</sub>

- Modifications to SCCP timing as shown in following slides

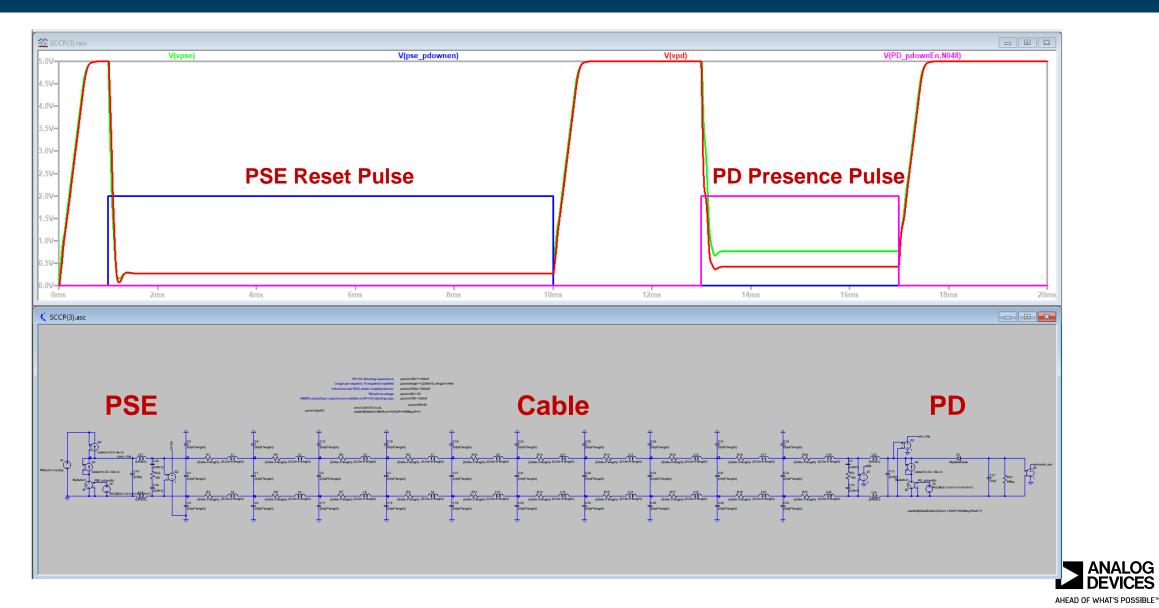

#### Spice Model of SCCP System 1km Fieldbus Type A Cable (STP), C<sub>PHY</sub> = 400nF

## **Reset command timing proof**

*Red* indicates changed parameters *Bold* indicates parameters captured in SCCP electrical requirements

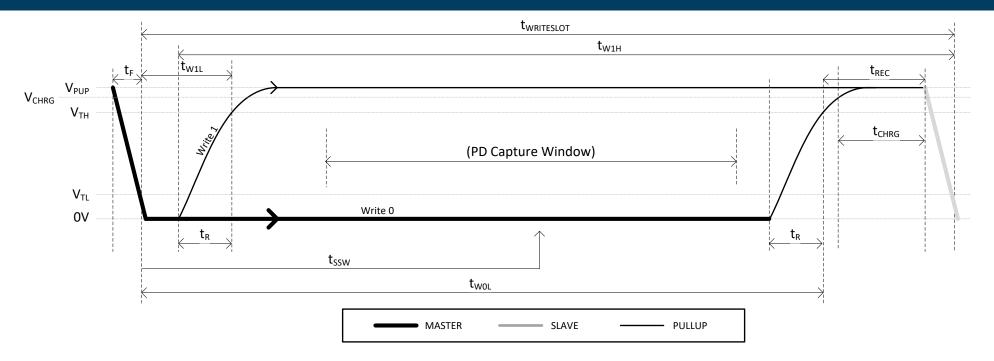

# Write 0/1 slot timing proof

| Symbol            | Min  | Тур | Max  | Unit | Note                                                                      |

|-------------------|------|-----|------|------|---------------------------------------------------------------------------|

| t <sub>F</sub>    |      |     | 250  | us   | 5V pu vs 1000hm pd                                                        |

| t <sub>R</sub>    |      |     | 500  | us   | 9mA PSE pu / 0.4uF C <sub>chan</sub> V <sub>TL</sub> to V <sub>CHRG</sub> |

| t <sub>w1L</sub>  | 90   |     | 610  | us   |                                                                           |

| t <sub>ssw</sub>  | 0.77 | 1.1 | 1.43 | ms   | PD capture measured from falling edge $V_{TL}$                            |

| t <sub>WOL</sub>  | 1.8  | 2.0 | 2.2  | ms   | PSE hold time for Write 0 symbol                                          |

| t <sub>REC</sub>  | 270  | 300 | 330  | us   | Charge PD SCCP reservoir capacitor                                        |

| t <sub>CHRG</sub> | 200  |     |      | us   | Critical PD SCCP reservoir capacitor charging region                      |

| twriteslot        |      |     | 2.78 | ms   |                                                                           |

*Red* indicates changed parameters *Bold* indicates parameters captured in SCCP electrical requirements

# Read 0/1 slot timing proof

*Red* indicates changed parameters *Bold* indicates parameters captured in SCCP electrical requirements

### Conclusion

- Technical feasibility has been established

- Ongoing mixed signal, system level validation

- Track 10SPE developments