# **Optional Cable Resistance Measurement**

GITESH BHAGWAT, ANDY GARDNER, HEATH STEWART SANTA BARBARA DESIGN CENTER

#### **Presentation Outline**

- Motivation- Reclaim Power Lost in Cable

- Leveraging existing SCCP protocol for resistance measurement

- Measurement- Overview

- PD and PSE Power Budgeting Calculations

- Optional Implementation

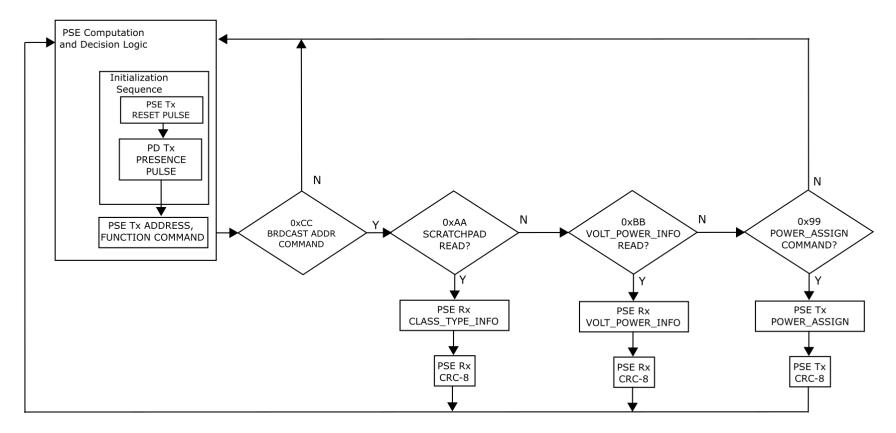

- SCCP flowchart

- Optional SCCP Registers

- SCCP Electrical Requirements

- Baseline Text for 104.7

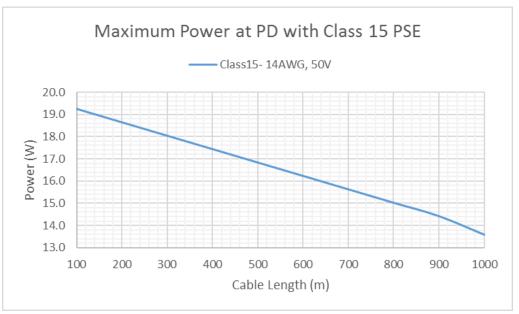

## Motivation- Reclaim Power Lost in Cable

- Systems with shorter cables are penalized

- For Example: Class 14 systems (14AWG, V<sub>PSE-min</sub> = 50V)

- P<sub>CLASS(min)</sub> = 19.4W This is the minimum power every Class 14 PSE is capable of supplying

- P<sub>PD(max)</sub> = 13.6W This is the maximum power any Class 14 PD is allowed to draw

- This is with an assumption that 5.87W of power is always lost in the cable

- 5.87W is calculated as  $I_{PI-max}^2 \times R_{loop(CLASS-max)} = 0.388A^2 \times 39$ ohms

- For systems with shorter links, for instance a 100meter link with about 40hms loop resistance,

- Power lost in the cable is about 0.6W

- With no change in PSE, the PD can now draw almost 19W an almost 40% increased power

|       |       |              | Specified | by AWG and          | Length       |          |                        |             |  |

|-------|-------|--------------|-----------|---------------------|--------------|----------|------------------------|-------------|--|

|       |       |              |           | 1000m               |              | 300m     |                        |             |  |

| AWG   | Class | Vpse,<br>min | lpi, max  | Rloop, max<br>(60C) | Ppd<br>1000m | lpi, max | Rloop,<br>max<br>(60C) | Ppd<br>300m |  |

| 18AWG | 1     | 20           | 102       | 59                  | 1.4          | 326      | 18                     | 4.6         |  |

| 14AWG | 2     | 20           | 155       | 39                  | 2.2          | 488      | 12                     | 6.8         |  |

| 24AWG | 3     | 20           | 52        | 116                 | 0.7          | 169      | 36                     | 2.4         |  |

| 18AWG | 4     | 50           | 254       | 59                  | 8.9          | 815      | 18                     | 28.5        |  |

| 14AWG | 5     | 50           | 388       | 39                  | 13.6         | 1221     | 12                     | 42.7        |  |

| 24AWG | 6     | 50           | 129       | 116                 | 4.5          | 400      | 36                     | 14.0        |  |

- Reference: http://www.ieee802.org/3/cg/public/May2018/stewart\_3g\_01f\_0518.pdf\_and IEEE802.3cg Draft 2.0

- 3

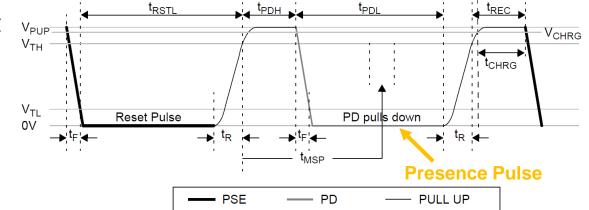

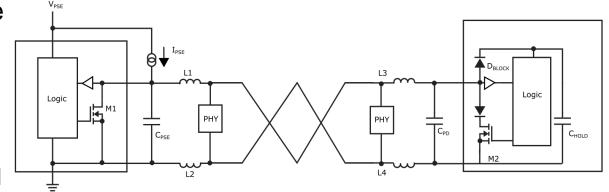

## Leveraging existing SCCP protocol for resistance measurement

- Each SCCP transaction is initiated with a PSE Reset Pulse followed by PD Presence Pulse

- While the PD is pulling down for the presence pulse, the PSE can measure current and voltage at its PI and calculate cable resistance

- However, variability of PD Pull down voltage can introduce significant error in calculated resistance

- To eliminate this uncertainty, PD reports to PSE the voltage at its PI during the presence pulse

- This can be implemented with an ADC measuring and reporting the Pull down voltage at PD's PI

- OR

- With a voltage shunt regulating a constant voltage and reporting that voltage

Reference: <u>http://www.ieee802.org/3/bu/public/sep14/gardner\_3bu\_1\_0914.pdf</u> and IEEE802.3cg Draft 2.0

#### Measurement - Overview

- PSE Sources a current in the range of 9mA to 16mA during PD Presence pulse

- PSE knows or measures this current value with the accuracy required to support the measurement

- PSE measures voltage at its PI with the accuracy required to support the measurement

- PSE-side measurement accuracy is a function of the PSEs desired R<sub>cable</sub> measurement accuracy, not specified by standard

- PD reports voltage at its PI during the Presence pulse

- PD reports the voltage as an 8 bit value with an accuracy of +/- 20mV and LSB of 10mV

- PD also requests a target power level

- PSE then calculates the cable resistance as:

$$R_{cable} = \frac{V_{meas-PSE} - V_{report-PD}}{I_{meas-PSE}}$$

PSE then reports the power allocated to PD through the PSE Status 2 register (clause 45)

## PD and PSE Power Budgeting Calculations

- $R_{CABLE\_MEAS} = \frac{V_{MEAS\_PSE,min} V_{report\_PD,max}}{I_{MEAS\_PSE,min}}$

- $\blacktriangleright R_{CABLE} = Min ((R_{CABLE_MEAS}), R_{LOOP(CLASS-max)})$

- ► If  $P_{PD\_REQ} > P_{PD(max)}$

- $P_{PD\_ASSIGN} = Min \{P_{PD\_REQ}, (P_{CLASS(min)} (I_{PI(MAX)}^2 \times R_{CABLE}))\}$

- Note: When  $R_{CABLE} = R_{LOOP(CLASS-max)}$ ;  $(P_{CLASS(min)} I_{PI(MAX)}^2 \times R_{CABLE}) = P_{PD(max)}$

- ► Else ( $P_{PD\_REQ} \le P_{PD(max)}$ )

- P<sub>PD\_ASSIGN</sub> = P<sub>PD\_REQ</sub>

► Sample:  $P_{PSE\_ALLOC} = V_{PSE(min)} \times \frac{V_{PSE(min)} - \sqrt{(V_{PSE(min)}^2 - 4 \times R_{CABLE} \times P_{PD\_ASSIGN})}}{2 \times R_{CABLE}}$

<sup>a</sup>V<sub>PSE(max)</sub> is the maximum allowed voltage at the PSE PI over the full range of operating conditions.

<sup>b</sup>V<sub>PSE\_OC(min)</sub> is the minimum allowed open circuit voltage measured at the PSE PI.

<sup>c</sup>I<sub>PI(max)</sub> is the maximum current flowing at the PSE and PD PIs except during inrush or an overload condition. I<sub>PI(max)</sub> may be exceeded during inrush or an overload (see 104.4.6.2). Users are cautioned to be aware of the ampacity of cabling, as installed, and local codes and regulations (see 104.8.1).

<sup>d</sup>P<sub>Class(min)</sub> is the minimum average available output power at the PSE PI.

<sup>e</sup>P<sub>PD(max)</sub> is the maximum average available power at the PD PI.

## PD INFO Register and PSE Control Register – Optional Implementation

#### ► Modify Table 104-9 and 45-211q as shown in this slide

| Bit(s)          | Name                                       |        | Desc  | riptio | n    |       |        |        |        |        |      |        | R/W |

|-----------------|--------------------------------------------|--------|-------|--------|------|-------|--------|--------|--------|--------|------|--------|-----|

| b[15:12]        | Туре                                       | 15     |       | 14     |      | 13    |        | 12     |        |        |      |        | RO  |

|                 |                                            | 1      |       | 1      |      | 1     |        | 0      |        |        | = Ty | pe A   |     |

|                 |                                            | 1      |       | 1      |      | 0     |        | 1      |        |        | = Ty | ре В   |     |

|                 |                                            | 1      |       | 0      |      | 1     |        | 1      |        |        | = Ty | pe C   |     |

|                 |                                            | 0      |       | 1      |      | 1     |        | 1      |        |        | = Ty | pe D   |     |

|                 | <del>Reserved</del><br>Cable<br>Resistance | 1- Cat | lo ro | istan  | co m | 02611 | omo    | ntor   | ablo   | Ч      |      |        |     |

| b[10]           | Measurement                                |        |       |        |      |       |        |        |        |        |      |        | RO  |

| b[10]<br>b[9:0] | Class                                      | 9      | 8     | 7      | 6    | 5     | 4      | 3      | 2      | 1      | 0    |        | RO  |

| 017.01          | 0.000                                      | 1      | 1     | 1      | 1    | 1     | 1      | 1      | 1      | 1      | -    | lass 0 |     |

| 0[9.0]          |                                            | 1 L    |       |        |      |       |        |        |        |        |      |        |     |

| 0[9.0]          |                                            | 1      | 1     | 1      | 1    | 1     | 1      | 1      | 1      | 0      | 1 =C | lass 1 |     |

| 0[9.0]          |                                            |        |       |        |      | 1     | 1<br>1 | 1<br>1 | 1<br>0 | 0<br>1 |      |        |     |

|                          | Table 45-211q- PO           | DL PSE Control register bit definitions   |     |  |  |  |

|--------------------------|-----------------------------|-------------------------------------------|-----|--|--|--|

| Bit(s)                   | Name                        | Description                               | R/W |  |  |  |

| 13.0.15: <mark>23</mark> | Reserved                    | Value always 0                            | RO  |  |  |  |

|                          | Enable cable resistance     | 1 = Cable resistance measurement enabled  | R/W |  |  |  |

| 13.0.2                   | measurement                 | 0 = Cable resistance measurement disabled |     |  |  |  |

|                          | Enable power classification | 1 = Power classification enabled          | R/W |  |  |  |

| 13.0.1                   |                             | 0 = Power classification enabled          |     |  |  |  |

|                          |                             | 1 = PSE enabled<br>0 = PSE enabled        |     |  |  |  |

| 13.0.0                   | PSE Enable                  |                                           |     |  |  |  |

## PSE Status 2 register changes

Modify Table 45-211s as shown in this slide

| Bit(s)                  | Name                            | Description                                                       |   |                |             | R/W |  |  |  |

|-------------------------|---------------------------------|-------------------------------------------------------------------|---|----------------|-------------|-----|--|--|--|

| 13.2.15                 | Invalid Class                   | 1 = Invalid PD class detected<br>0 = No invalid PD class detected |   |                |             |     |  |  |  |

| 13.2.14: <del>3</del> 9 | Reserved                        | Value always 0                                                    |   |                |             | RO  |  |  |  |

|                         | <del>Reserved</del> PD Assigned |                                                                   |   |                |             |     |  |  |  |

| 13.2.8:3                | Power                           | PD Assigned Power                                                 |   |                |             | RO  |  |  |  |

| 13.2.2:0                | PD Type                         | 2                                                                 | 1 | 0              |             | RO  |  |  |  |

|                         |                                 | 1                                                                 | 1 | 1              | = Unknown   |     |  |  |  |

|                         |                                 | 1                                                                 | 1 | 0              | = Reserved  |     |  |  |  |

|                         |                                 |                                                                   |   |                | Reserved    |     |  |  |  |

|                         |                                 | 1                                                                 | 0 | <del>x</del> 0 | Type E PD   |     |  |  |  |

|                         |                                 | 0                                                                 | 1 | 1              | = Type D PD |     |  |  |  |

|                         |                                 | 0                                                                 | 1 | 0              | = Type C PD |     |  |  |  |

|                         |                                 | 0                                                                 | 0 | 1              | = Type B PD |     |  |  |  |

|                         |                                 | 0                                                                 | 0 | 0              | = Type A PD |     |  |  |  |

### **SCCP** Flowchart

- Add Two SCCP Commands:

- 0xBB : VOLT\_POWER\_INFO Read

- 0x99 : POWER\_ASSIGN Write

- Replace Figure 104-13 with the figure shown on this slide

## SCCP Functions from the PD/ PSE State diagrams

Modify Clause 104.4 and 104.5 as shown below

#### 104.4.3.5 Functions

do\_classification

This function returns the following variables:

CLASS\_TYPE\_INFO register: (...description of register...)

PSEs that support cable resistance measurement shall also return the VOLT\_POWER\_INFO, POWER\_ASSIGN registers. Refer Table 104-10, 104-11 for description of contents.

#### 104.5.3.5 Functions

do\_sccp

This function returns the following variable to the PSE:

CLASS\_TYPE\_INFO register: refer to Table 104–9 for a description of the contents.

PDs that support cable resistance measurement shall also return the VOLT\_POWER\_INFO register. Refer Table 104-10 for description of contents.

## **Optional SCCP Registers**

- Add Optional SCCP Registers:

- (Table 104.10) VOLT\_POWER\_INFO:

- Voltage Reported by PD as an 8 bit value

- Initial Power Requested by PD as a 6 bit value

- (0.3125W/ LSB)

- 2 bits Reserved

| Bit(s)   | Name                                         | Description                          | R/W |

|----------|----------------------------------------------|--------------------------------------|-----|

| b[15:14] | Reserved                                     | Value Always 0                       | RO  |

| b[13:8]  | PD Requested<br>Power                        | Power Requested by PD, 0.3125 W/ LSB | RO  |

| b[7:0]   | Voltage at PD<br>PI during<br>Presence Pulse | +/- 20mV tolerance, 10mV per LSB     | RO  |

- ► (Table 104.11) POWER\_ASSIGN:

- PD Assigned Power, by PSE, as a 6 bit value

- (0.3125W/ LSB)

- 10 bits Reserved

| Table 104-11 POWER_ASSIGN Register |                      |                                  |     |  |  |  |  |

|------------------------------------|----------------------|----------------------------------|-----|--|--|--|--|

| Bit(s)                             | Name                 | Description                      | R/W |  |  |  |  |

| b[15:6]                            | Reserved             | Value Always 0                   | RO  |  |  |  |  |

| b[5:0]                             | PD Assigned<br>Power | PD Assigned Power, 0.3125 W/ LSB | WO  |  |  |  |  |

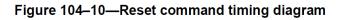

### **SCCP Electrical Requirements**

Modify Table 104-8 as shown in this slide

- PSE Input Logic Low threshold is determined as:

- V<sub>TL-PSE</sub> = V<sub>TL-PD</sub> + Link Resistance<sub>(max)</sub> × Probe Current<sub>(max)</sub>

- ► For Type E PSEs:

- Link Resistance<sub>(max)</sub> × Probe Current<sub>(max)</sub> = 59ohms × 16mA = 0.944V

- ► Hence,  $V_{TL} = 2V$  for Type E PSEs

- PDs that support cable resistance measurement, have a longer presence pulse to allow 50/60 Hz noise rejection during the measurement

|   | Item | Parameter                   | Symbol             | Unit | Min           | Max | PSE/PD<br>type                         | Additional<br>Information                            |

|---|------|-----------------------------|--------------------|------|---------------|-----|----------------------------------------|------------------------------------------------------|

|   | 1    | PSE Pull-up Voltage         | V <sub>PUP</sub>   | V    | Vgood_PSE_max | 5   | All                                    | See Table 104-1                                      |

|   | 2    | PSE Pull-up Current         | I <sub>PUP</sub>   | mA   | 9             | 16  | All                                    |                                                      |

| ) | 3    | Input Logic High Voltage    | V <sub>TH</sub>    | v    | 3             | -   | All                                    |                                                      |

|   | 4    | Input Logic Low Voltage     |                    |      |               | 1   | <del>All-</del> A, B,C,D,<br>Type E PD |                                                      |

|   |      |                             | V <sub>TL</sub>    | V    | -             | 2   | Type E PSE                             |                                                      |

|   | 5    | Sink Current                | I <sub>L</sub>     | mA   | 30            | -   | All                                    | V <sub>port</sub> > 0.8V                             |

|   |      |                             |                    |      |               |     |                                        |                                                      |

|   |      |                             |                    |      | 2.5           | 7.5 | A, B, C, D                             |                                                      |

|   |      |                             |                    |      | 2.8           | 5.2 | E                                      |                                                      |

|   | 15   | Presence-Detect Low<br>Time | t <sub>PDLOW</sub> | ms   | 21            | 31  | E                                      | PDs that support link segment resistance measurement |

#### Modify Clause 104.7

Implementation of SCCP by PSEs and PDs that present a valid detection signature is optional. PDs that present an invalid detection signature as specified in Table 104–6 shall implement SCCP. The PSE acts as a master during the SCCP exchange, controlling the PD that acts as the slave device. SCCP is a current-sinking, wired-OR (e.g., open-drain or open-collector), half-duplex bidirectional serial data bus. The PSE sources the required pull-up current. The logic high voltage is limited by the voltage signature device at the PD. PDs can derive power from the PSE's pull-up current during classification via the PD PI.

Measurement of cable resistance by PSEs and PDs that implement SCCP is optional. PSEs and PDs that implement cable resistance measurement shall support the VOLT\_POWER\_INFO and POWER\_ASSIGN registers (Table 104.10, 104.11). PSEs that implement cable resistance measurement shall report assigned power through PSE Status Register 2 (See 45.2.7b.3).

# Thank You!

QUESTIONS? FEEDBACK?